状态机——序列检测

module top_module ( input clk, input reset, // Synchronous reset input data, output start_shifting); reg[4:0]cs,ns; parameter IDLE=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000; always@(posedge clk)begin if(reset) cs<=IDLE; else cs<=ns; end always@(*)begin case(cs) IDLE:begin if(data==1) ns=s1; else ns=IDLE; end s1:begin if(data==1) ns=s2; else ns=IDLE; end s2:begin if(data==0) ns=s3; else ns=s2; end s3:begin if(data==1) ns=s4; else ns=IDLE; end s4:begin if(reset) ns=IDLE; else ns=s4; end default:ns=IDLE; endcase end //assign start_shifting=cs==s4; always@(posedge clk) if(reset) start_shifting<=0; else begin case(ns) IDLE:start_shifting<=0; s1:start_shifting<=0; s2:start_shifting<=0; s3:start_shifting<=0; s4:start_shifting<=1; default:start_shifting<=1; endcase end endmodule

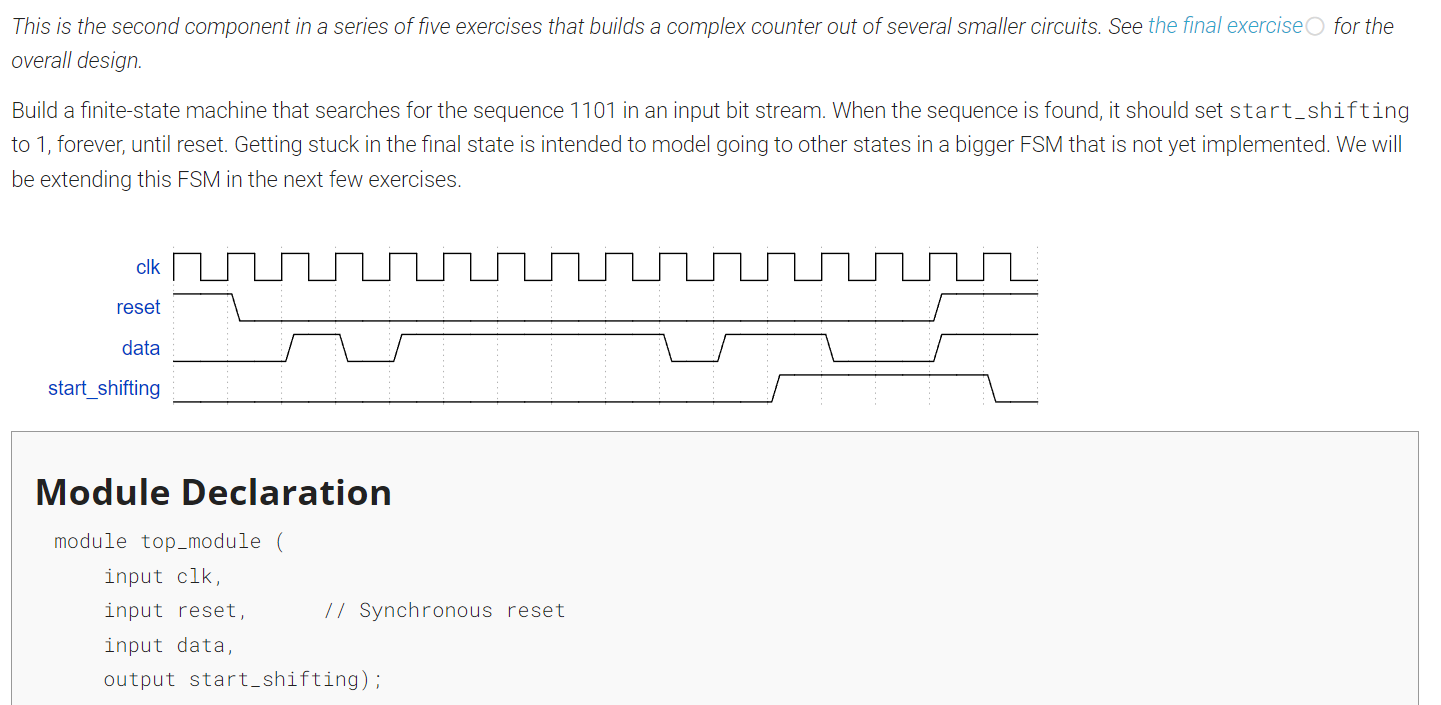

采用三段式状态机监测序列1101,注意当出现11后,再出现1时,状态s2保持为s2,出现0时进入s3。