异步信号与同步电路交互、亚稳态问题

在数字集成电路设计中,通常采用的是同步时钟的设计方法。在一个理想的全局时钟的控制下,只要电路的各个环节都实现了时序收敛,整个电路就可以可靠地实现预定的功能。但从实际应用的角度出发,一块复杂的SoC芯片上只用一个全局同步的时钟来设计是不经济的,此外,一块芯片的输入信号可能是来自另一块时钟完全不同步的芯片的输出。

如果强行让所有的设备或模块都工作在同一时钟频率下,为了满足最慢设备或模块的速度,而使系统不得不工作在相对较低的频率下,显然降低了系统性能。因此,在SoC设计中,必然会面临处理来自不同时时钟域的数据的问题,称为异步信号与同步电路的交互问题。

亚稳态现象:

通常,把两个彼此不同频率的时钟或两个彼此上升沿不对齐的时钟称作彼此异步时钟,异步时钟域的信号之间不可避免地会发生信号间的交互,一般把要传输到一个不同于它所在时钟域(目标时钟域)的信号称作异步输入信号(或异步信号)。

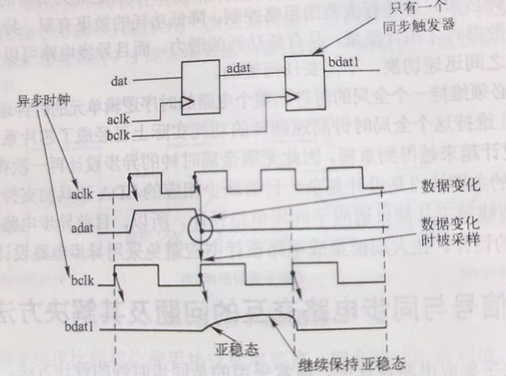

如图所示,信号adat在aclk时钟域,相对于bclk是异步输入信号,aclk和bclk称为异步时钟,两个触发器工作在不同时钟域下。由图可知,异步信号adat的下降沿正好发生在bclk时钟的上升沿附件,这样就违反了触发器的建立时间或保持时间,从而第二个触发器锁定了一个不确定的值,这个值可以是1,也可以是0,更有可能是一个物理上的不定态x—无效电平的状态。这种违反了触发器保持或建立时间且使触发器锁存到一个无效电平的状态的现象称作亚稳态现象。异步信号直接接入触发器输入端的时候不但可能传输一个错误的逻辑信号(信号实际值是1,但是触发器采集到的是0,或反之),更有可能使触发器进入亚稳态并将其传播下去,造成严重的系统错误,同时还会造成非常大的系统功耗损失。

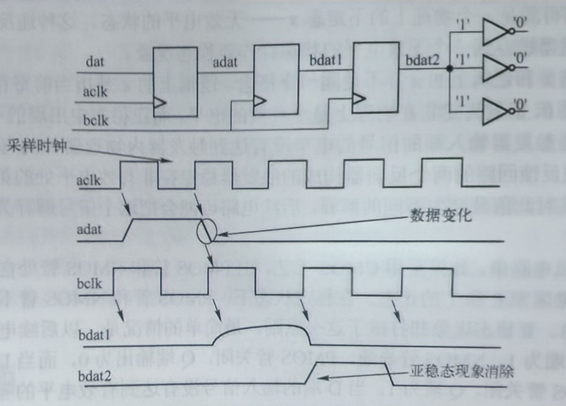

不难发现,只要在采到无效电平后等待足够长的时间,处在亚稳态的触发器就会回到一个有效的电平状态上去。而这个延时通常通过在采样异步信号的触发器后再加入一级触发器来实现,也就是说,异步信号只有在经过目的时钟域的两级触发器采样后,才会对目的时钟域的后续电路起作用。这种由双触发器构成的异步信号采样逻辑被称作同步器。

如图所示,这图好像有点问题。虽然第一级触发器(badt1)在采样异步信号的时候可能进入亚稳态,但是经过一个时钟周期的延时,当第二级触发器(bdat2)采样其输出信号时,它已经回到一个有效电平的稳定状态,使第二季触发器不会再出现亚稳态,从而防止了亚稳态在整个电路中的传播。完全解决亚稳态的方法是不存在的。触发器可能正好采样到输入信号的变化中点,从此点回到稳定电平的状态需要等待的时间理论上为无穷大。然而实际电路中极小的噪声或环境的变化都会使触发器脱离亚稳态,所以只要满足足够大小的等待时间,亚稳态出现的概率就会减小到在工程中可以忽略或接收的程度。如果系统的工作频率过高,系统中发生亚稳态的可能性就会增大,此时两级触发器构成的同步器不足以解决稳态问题,必须通过增加同步器的级数进而延长等待时间的方法来解决,带来的代价是异步信号的交互会变更慢。

亚稳态问题是异步时钟信号交互的物理(固有)问题。异步信号之间的信号交互可以归纳为两种类型—控制信号和数据信号。异步控制信号的处理又分为快时钟同步慢时钟域下的异步控制信号、慢时钟同步快时钟域下的异步控制信号;异步时钟域的数据同步依靠握手机制和异步FIFO来实现。具体实现待续。

摘抄自--《SoC设计方法与实现》

浙公网安备 33010602011771号

浙公网安备 33010602011771号