同步电路、异步电路设计

1. 同步电路

1.1同步电路的定义

所谓同步电路,即电路中所有受时钟控制的单元,如触发器(Flip Flop)或寄存器(Register),全部由一个统一的全局时钟控制。

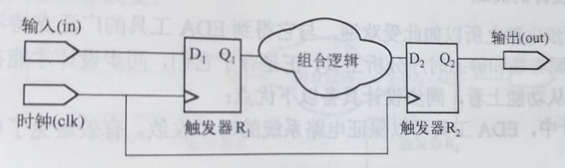

如图所示,触发器R1和R2都由一个统一的时钟clk来控制时序,在R1和R2之间有一堆组合逻辑,这就是一个最简单的同步电路。

1.2同步电路的收敛问题

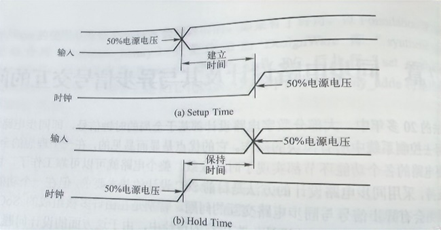

时序电路的一个首要问题是触发器的时序收敛问题。触发器的时序收敛保证了触发器输入端的数据在时钟信号的有效沿来临之前达到稳定。即满足了触发器的建立时间(Setup Time),同样也保证了触发器输入端数据在时钟有效沿过后的一段时间内保持稳定,即满足触发器的保持时间(Hold Time)。

第1级触发器R1的输出Q1在时钟上升沿后得到新值,Q1值经过一段组合逻辑后输出连接到下一级触发 器R2的输入端D2,经过这段组合逻辑必然要有一段延时 Tdelay输出才能最终稳定。假设触发器R2的建立时间为Tsetup2,所谓满足时序收敛首先要满足时钟周期T≥Tsetup2+ Tdelay, 可以看出同步电路的最大工作速度是由最长的组合逻辑路径延时决定的。同样为了保证D2在T时刻的值能够被无误地锁存,其值必须在保持时间Thold内保持稳定。这样整个同步电路就可以可靠无误地运行下去了。

1.3同步电路的优点与缺陷

优点:

在同步设计中,EDA工具可以保证电路系统的时序收敛,有效避免了电路设计中竞争冒险现象;

由于触发器只有在时钟边缘才改变取值,很大限度减少了整个电路受毛刺和噪声的影响的可能。

缺陷:

同步设计中最主要的问题是时钟偏斜(Clock Skew)及功耗的问题。

由于版图上达到每个触发器时钟端口的连线长度不同,驱动单元的负载不同等原因,如果没有经过处理,全局时钟线到达各个时序逻辑单元的时钟端口的时间就不可能相同。这种时钟到达在空间上的差别称为时钟偏斜(Clock Skew)。

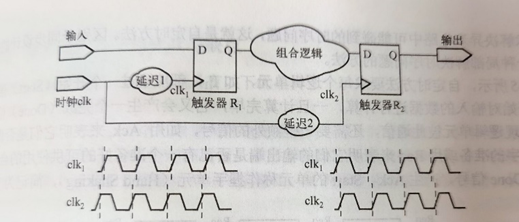

时钟偏斜如上图所示,时钟偏斜的后果是非常严重的,试想如果clk2早于clk1到达,会造成数据到达R2的建立时间不够,如果要保证电路正常工作就只能降低电路的工作频率。反之,clk2晚于clk1到达,会不满足保持时间的时序要求,从而产生竞争冒险现象。目前解决上述问题的方法是采用EDA工具进行时钟树综合。它的原理是根据最长时钟路径来平衡其他时钟路径,这就需要加入大量的延迟单元,使得电路的面积和功耗增加。

除了时钟偏斜,同步电路还受到时钟抖动(Clock Jitter)的影响。所谓时钟抖动指的是,芯片某一给定点上时钟信号的间歇性变化,即时钟周期在不同的时间段长短不一。

2.全异步电路设计

全异步设计和同步设计最大的不同就是它的电路中的数据传输可以在任何时候发生,电路中没有一个全局的或局部的控制时钟。

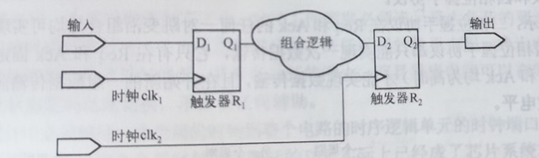

如图所示,触发器R1由时钟clk1控制,触发器R2由时钟clk2控制,R1的输出端Q1通过组合逻辑连接到R2的输入端D2。D2的输入端的数据值的跳变并不在clk2的控制之下,它可能在时钟clk2的任意时间点发生跳变。在全异步设计中,原来同步设计中可避免竞争冒险现象、减少噪声影响的优点全没有了。

2.1自定时方法

为了保证电路在任何操作条件和输入序列下都能正确工作,需要一套可靠的技术解决电路中可能碰到的时序问题,这就是自定时方法。区别于同步设计的全局时钟,它是一种局部解决时序问题的方法。

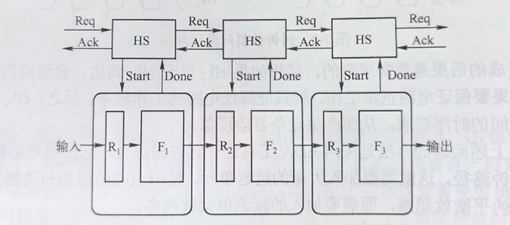

如上图所示,自定时方法要求每个逻辑单元,都能通过一个开始(Start)信号来启动,从而开始对输入的数据进行计算,一旦计算完毕,它又会产生一个完成(Done)信号。自定时方法工作方式描述如下:

首先,一个输入字节到达,F1的Req信号上升,如果F1此时没有运行,输入缓冲器R1接收数据,HS发出Ack,激活发出输入字的前级模块,然后,Start信号上升,F1开始运行。一段延迟后,Done信号升高,表明运算完成,接着,F1的HS模块向F2发出Req信号,由此,数据一步一步向下传播,实现了流水功能。

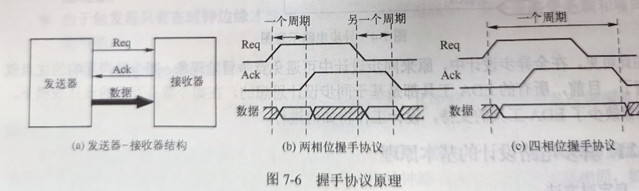

2.2握手协议自同步方法的实现离不开握手协议的支持,否则会出现竞争现象。

如图所示,二相位握手协议在Req和Ack的任何一对跳变沿组合处可实现一次数据信息,相应地,四相位握手协议却只能实现一次数据传输,它只有在Req和Ack固定的电平组合下(图中为Req和Ack均为高时)才能实现数据传输,且在开始新的一组数据前Req和Ack必须回到无效电平。显然,二相位握手协议比四相位握手协议效率要高,但会造成电路死锁,其稳定性要远远低于四相位握手协议,所以四相位握手协议是大多数自定时电路的首选实现方法。

2.3异步设计电路的优点与缺陷

优点:

模块化特性突出,对信号的延迟不敏感,没有时钟偏斜问题,有潜在的高性能特性,好的电子兼容性,具有低功耗的特性。

缺陷:

设计复杂,缺少相应的EDA软件支持。

摘抄自《Soc设计方法与实现》---

浙公网安备 33010602011771号

浙公网安备 33010602011771号