跨时钟域同步1---亚稳态的产生和解决方案

以下内容参考自:《正点原子逻辑设计指南》

逻辑设计中一般存在多个时钟,那么信号在多个时钟之间如何切换呢?这个就涉及到了异步电路设计,异步电路设计也是逻辑设计中非常重要的设计,可以说异步处理不好,逻辑出问题的可能性非常大。

一、亚稳态简介

在介绍异步设计方法之前,我们先了解下亚稳定的概念,为什么要先了解亚稳态呢?因为异步电路如果直接使用寄存器采样会出现问题,最常见的就是出现亚稳态。寄存器采样需要满足一定的建立时间(setup)和保持时间(holdup),而异步电路没有办法保证建立时间(setup)和保持时间(holdup),所以会出现亚稳态。

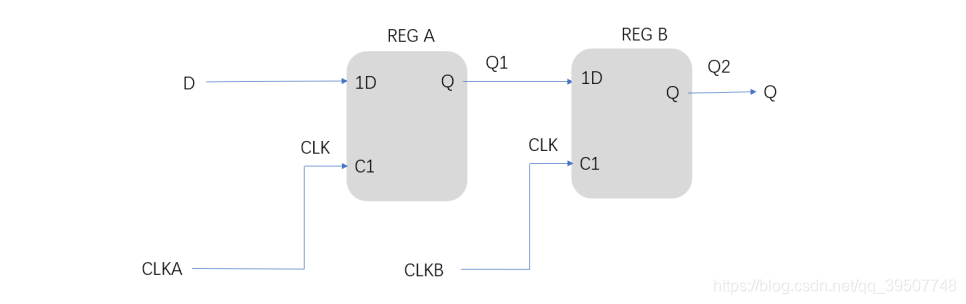

下图为两个不同时钟的寄存器的示意图,寄存器 B 采样可能采样到寄存器 A 输出的任意状态,包括 Q 的信号跳变沿。

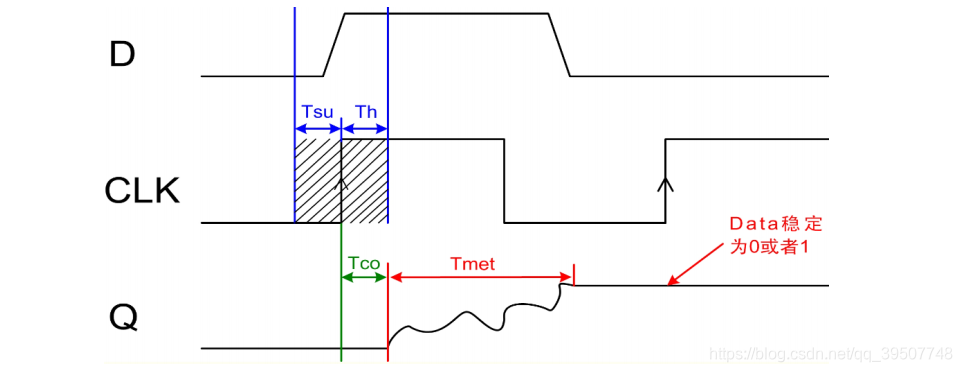

但是寄存器的 D 端信号需要满足建立时间 Tsu 和保持时间 Th 要求,否则就会出现 Q 端采样到不确定的值的状态,就是俗称的亚稳态。

二、亚稳态解决方法

异步电路设计就是要解决亚稳态的问题。异步电路设计一般有几个方法:

- 单 bit 信号:一般可按电平信号和脉冲信号来区分。

电平信号同步:同步逻辑设计中,电平信号是指长时间保持不变的信号。保持不变的时间限定是相对于慢时钟而言的。只要快时钟的信号保持高电平或低电平的时间足够长,以至于能被慢时钟在满足时序约束的条件下采集到,就可以认为该信号为电平信号。既然电平信号能够被安全的采集到,所以从快时钟域到慢时钟域的电平信号也采用延迟打拍的方法做同步。

脉冲信号同步:同步逻辑设计中,脉冲信号是指从快时钟域输出的有效宽度小于慢时钟周期的信号。如果慢时钟域直接去采集这种窄脉冲信号,有可能会漏掉。

- 假如这种脉冲信号脉宽都是一致的,在知道两个时钟频率比的情况下,可以采用"快时钟域脉宽扩展+慢时钟域延迟打拍"的方法进行同步。

- 如果有时窄脉冲信号又表现出电平信号的特点,即有时信号的有效宽度大于慢时钟周期而能被慢时钟采集到,那么对此类信号再进行脉冲扩展显然是不经济的。此时,可通过"握手传输"的方法进行同步。

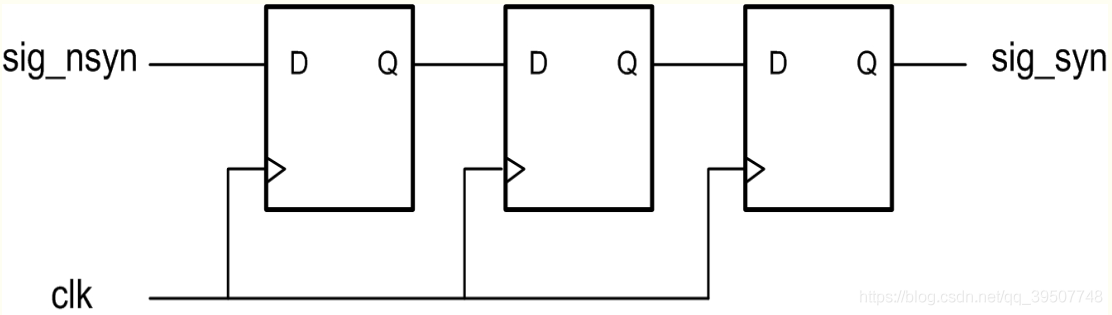

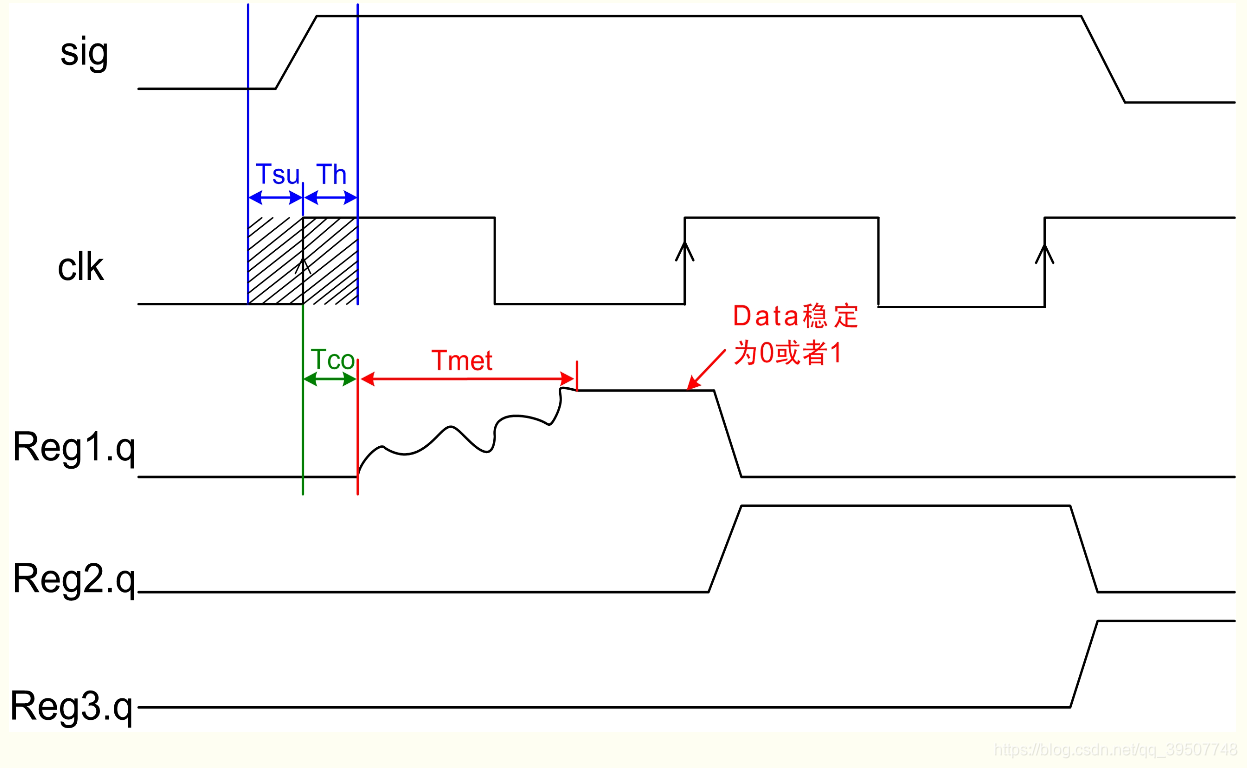

如上图所示就是一个正常第一级寄存器发生了亚稳态,第二级、第三极寄存器消除亚稳态时序模型。可以看出,当第一个寄存器发生亚稳态后,经过Tmet的振荡稳定后,第二级寄存器能采集到一个稳定的值。

- 多 bit 信号:使用格雷码+双D触发器、异步 FIFO 、DMUX同步器(延迟采样法)、或者使用握手协议。在这些方法中,除了传输的多bit数据信号,其中用到的各种单bit信号,仍然是通过打拍进行同步处理,如握手协议中的异步的

REQ/ACK。各方法的具体内容可参考:https://www.cnblogs.com/xianyufpga/p/13644201.html、异步 FIFO 设计。

常见的具体的解决办法可以看下图: 图源:https://zhuanlan.zhihu.com/p/414210434

三、常见问题及解答

1、为什么多比特不能采用打两拍的方法进行跨时钟域同步?

- 假设从时域A垮到时域B,在时域A刚好是从00变到11,在时域B中,时钟的上升沿来的时间是肯定一致的,但是各个bit从时域A到达时域B的时间是不一样的,slack不一样,亚稳态恢复到稳态的时间也是不一样的。因此如果只是简单的打两拍,由于00中的两个0并不是同时变成1的,因此子时域B中可能采到中间态01或10。

- 还有一个原因是多bit发生亚稳态的概率比单比特大很多,我们不这样做是可以降低亚稳态发生的概率的。

来看一个例子,设 src_data[2:0] 是二进制码的一个up计数器,值的变化为001 -> 010 -> 011 -> 100......

我们以001->010变化为例,在src_clk时钟沿到来之后,src_data[1]和src_data[0]都发生了反转。

- 现在假设我们对于每一位都用double flop同步到dst_clk去,dst_clk上的数据之前稳定在001, 那么当dst_clk的上升沿来的时刻和src_data变化的时刻差不多时会发生什么情况?有可能dst_data会直接变为010, 也有可能会有一个周期是000, 再变为010,也有可能是一个周期变为011,下一个周期再变为010。 这是因为src_data[1]和src_data[0]虽然都由src_clk触发,但是src_clk到达两个flop的时间不会完全一样,总会有先后,导致flop的Q端变化也会有先后。而double flop的第一级flop在latch src_data的时候也可能会latch上不同的值,即bit[0]和bit[1]分别latch上了变化前后的值。

- 另外还有一个原因是如果在dst_clk沿到来的时候src_data的flop的Q正在变化中,也就是在V_ih和V_il之间的时候,double_flop的第一级的D就会latch到一个即不是确定的1也不是确定的0的值,而在这个一个周期内这一级flop会将值稳定在0还是1也是说不准的,以上两个原因造成了,在dst_clk时钟域内,用double flop去同步的信号可能会出现错误。注意,这里说的多bit在同一个时钟沿发生翻转是针对src_clk来说的,而不是dst_clk来说的,这是回答你这个问题的核心。

2、慢到快使用打两拍同步的前提条件是?

- 传输的是单bit数据

- 周期不要太接近,频率比最好能大于或等于2

3、慢到快和快到慢考虑问题的区别?

- 慢到快,只要频率比满足时序约束条件,比如大于或者等于2,那么就无需考虑需要同步的信号是电平信号还是脉冲信号,直接打拍就可以。

- 快到慢,由于慢时钟不能保证采样到快时钟的每个周期的数据,所以需要考虑待同步的信号是电平信号还是脉冲信号。如果是脉冲信号,由于有效时间太短,比如只有一个快时钟周期,那么慢时钟就采样不到该,此时就需要对脉冲信号进行展宽操作。而如果是电平信号,只要宽度满足条件,直接打拍就可以了。