数据传输模型(建立时间与保持时间)

关于建立时间和保持时间的详细介绍以及相关例题可以参考以下文章:Verilog 建立时间和保持时间。

在介绍数据传输模型之前必须要了解的两个概念是建立时间和保持时间,下面就介绍一下建立时间和保持时间的含义及其物理意义?

-

建立时间就是时钟触发事件来临之前,数据需要保持稳定的最小时间,以便数据能够被时钟正确的采样。

-

保持时间就是时钟触发事件来临之后,数据需要保持稳定的最小时间,以便数据能够被电路准确的传输。

可以通俗的理解为:时钟到来之前,数据需要提前准备好;时钟到来之后,数据还要稳定一段时间。建立时间和保持时间组成了数据稳定的窗口,如下图所示。

下面看一种典型的上升沿 D 触发器,来说明建立时间和保持时间的由来。

G1~G4 与非门是维持阻塞电路,G5~G6 组成 RS 触发器。

时钟直接作用在 G2/G3 门上,时钟为低时 G2/G3 通道关闭,为高时通道打开,进行数据的采样传输。

但数据传输到 G2/G3 门之前,会经过 G4/G1 与非门,将引入时间延迟。引入建立时间的概念,就是为了补偿数据在 G4/G1 门上的延迟。即时钟到来之前,G2/G3 端的输入数据需要准备好,以便数据能够被正确的采样。

数据被时钟采样完毕后,传输到 RS 触发器进行锁存之前,也需要经过 G2/G3 门,也会引入延迟。保持时间就是为了补偿数据在 G2/G3 门上的延迟。即时钟到来之后,要保证数据能够正确的传输到 G6/G5 与非门输入端。

如果数据在传输中不满足建立时间或保持时间,则会处于亚稳态,导致传输出错。

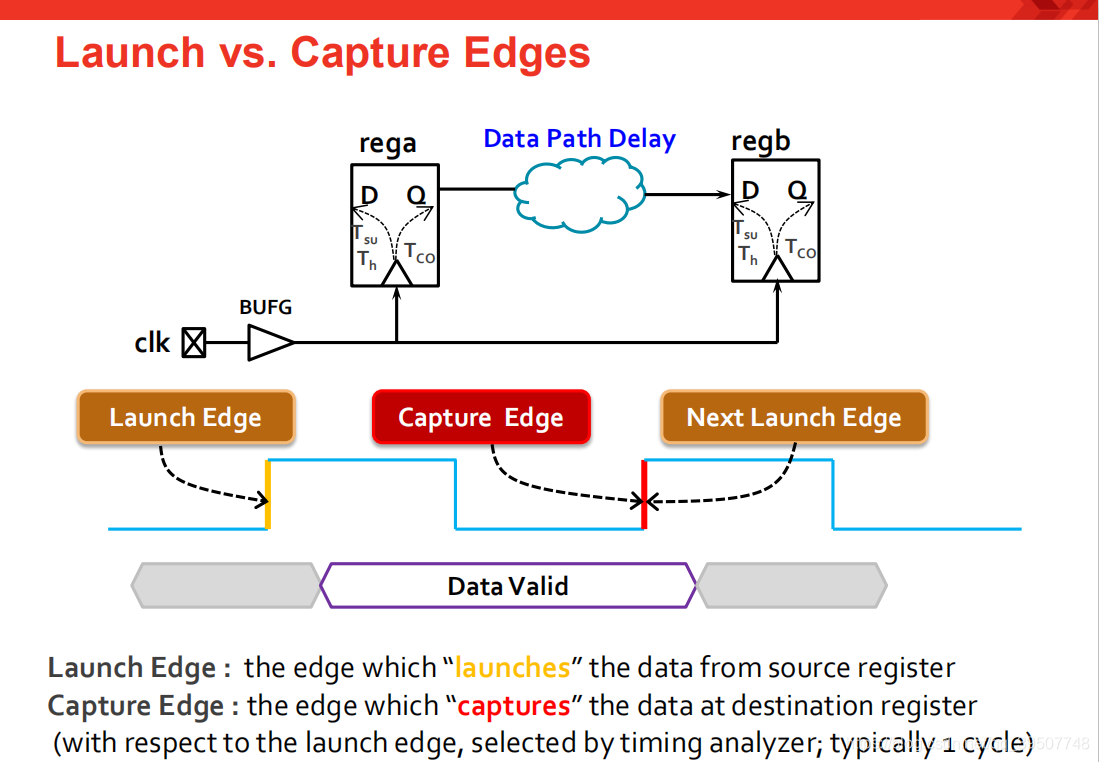

1、数据发起时间沿和捕获时间沿

数据的发起沿和数据的捕获沿相差一个CLK。

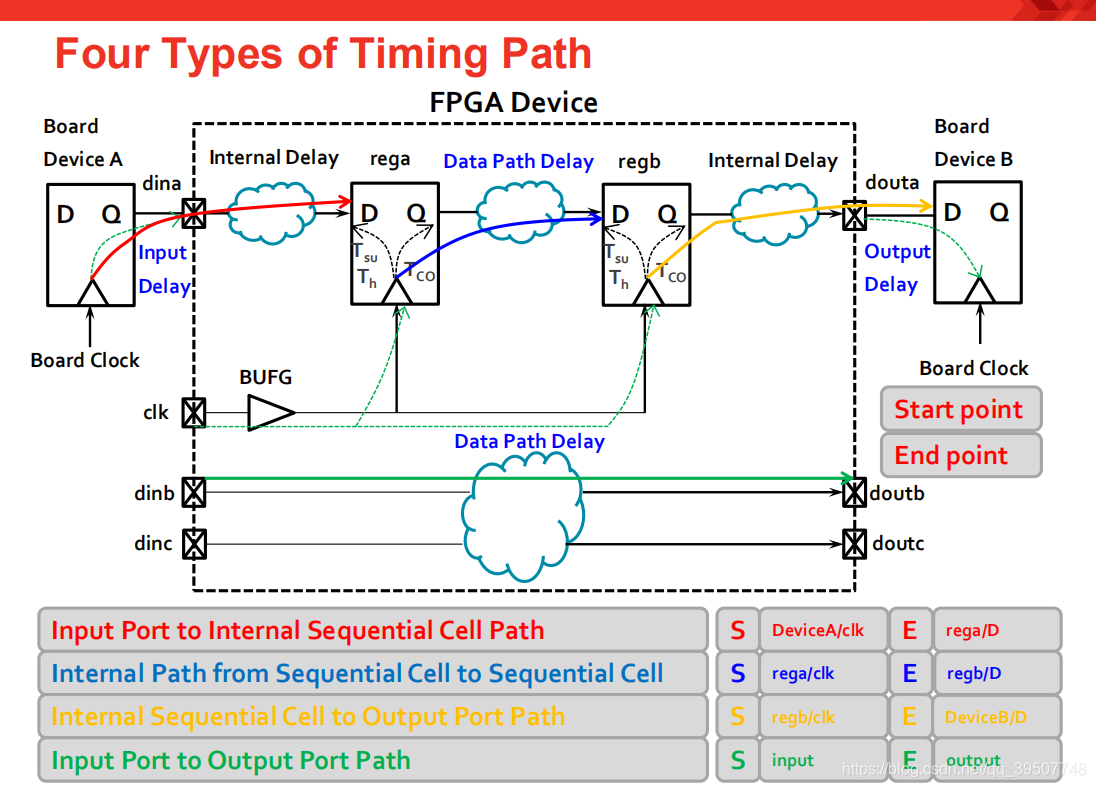

2、4种类型的时序路径

(1)输入端口到FPGA内部的第一级触发器;

(2)FPGA内部寄存器之间的路径;

(3)FPGA内部末级触发器到输出端口的路径;

(4)输入端口到输出端口的路径;

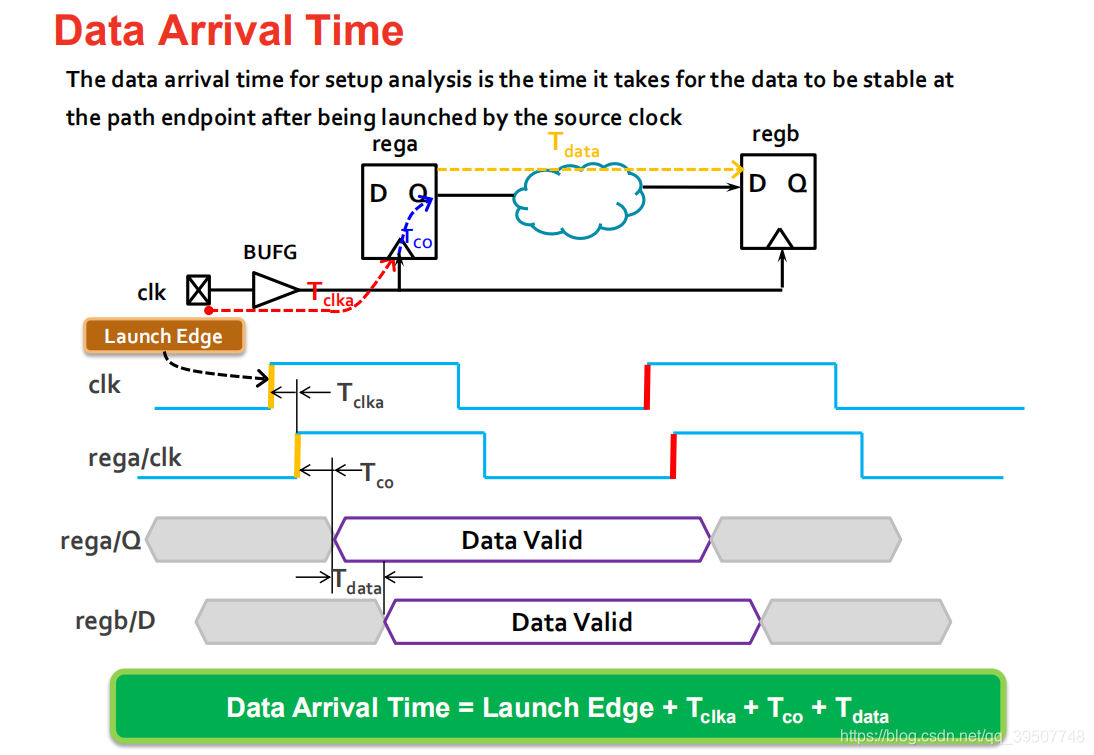

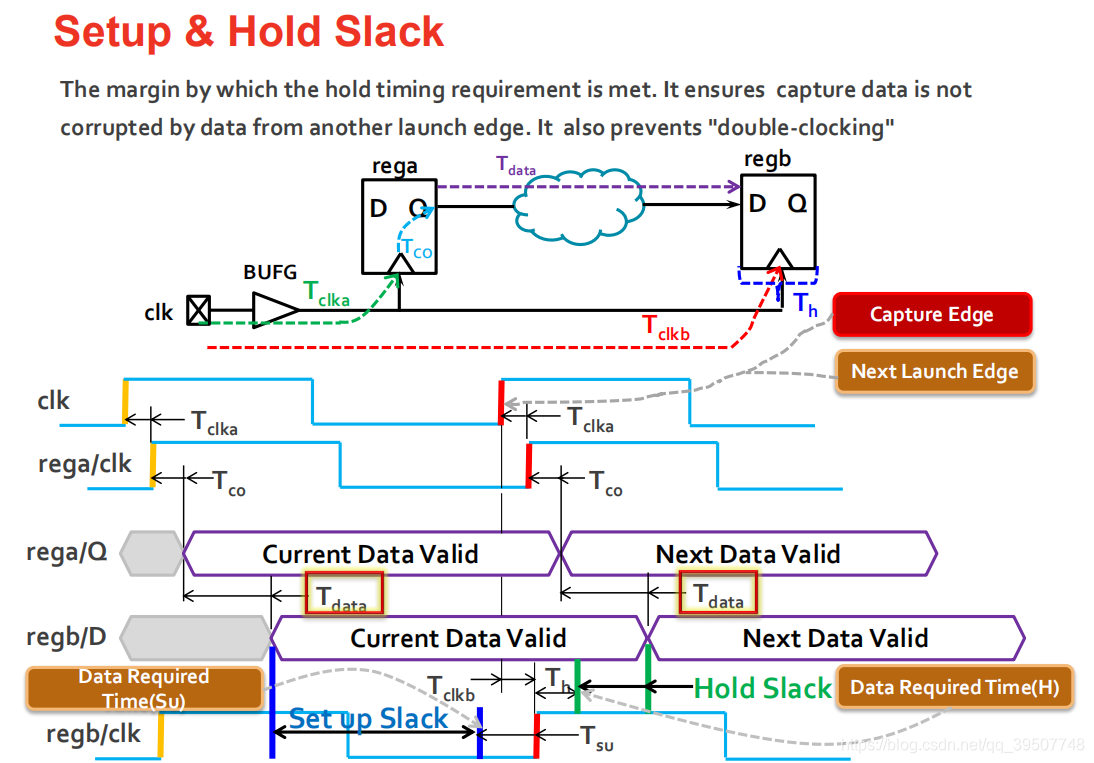

3、Data Arrival Time(setup): 建立时间数据到达时间

如果是hold的数据到达时间,则是从Capture Edge开始,再加上Tclka+Tco+Tdata;也即比setup的数据到达之间多了一个clk的时间。这里是需要区分的,因为后面计算setup和hold的裕量时会用到。

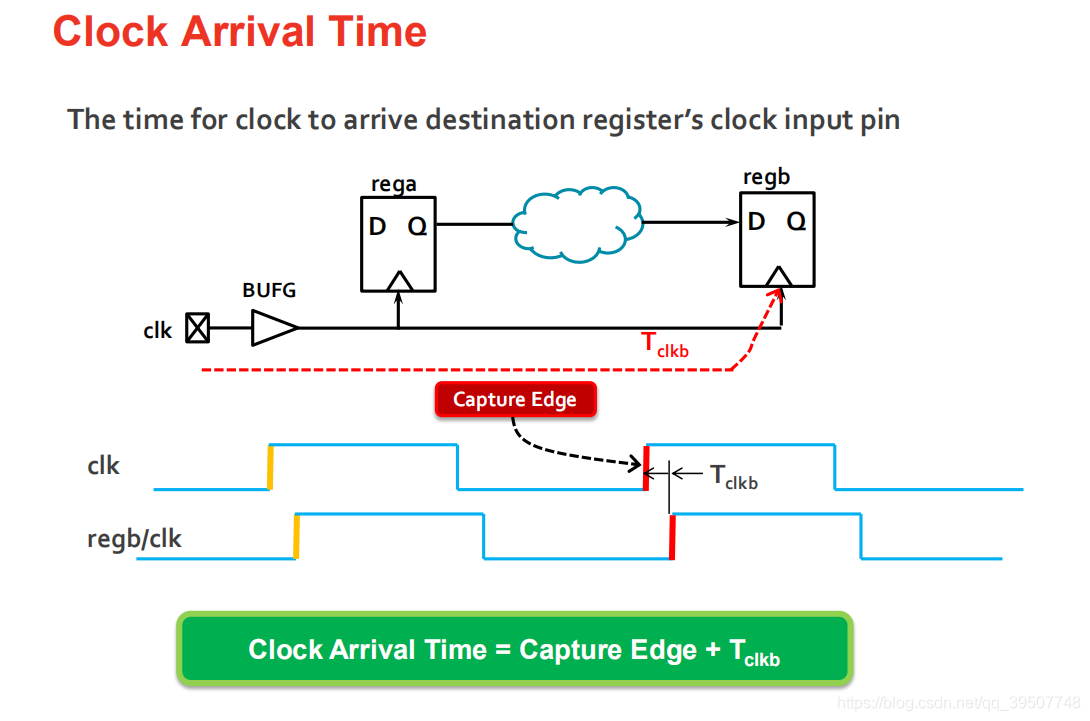

4、Clock Arrival Time: 目的寄存器时钟到达时间

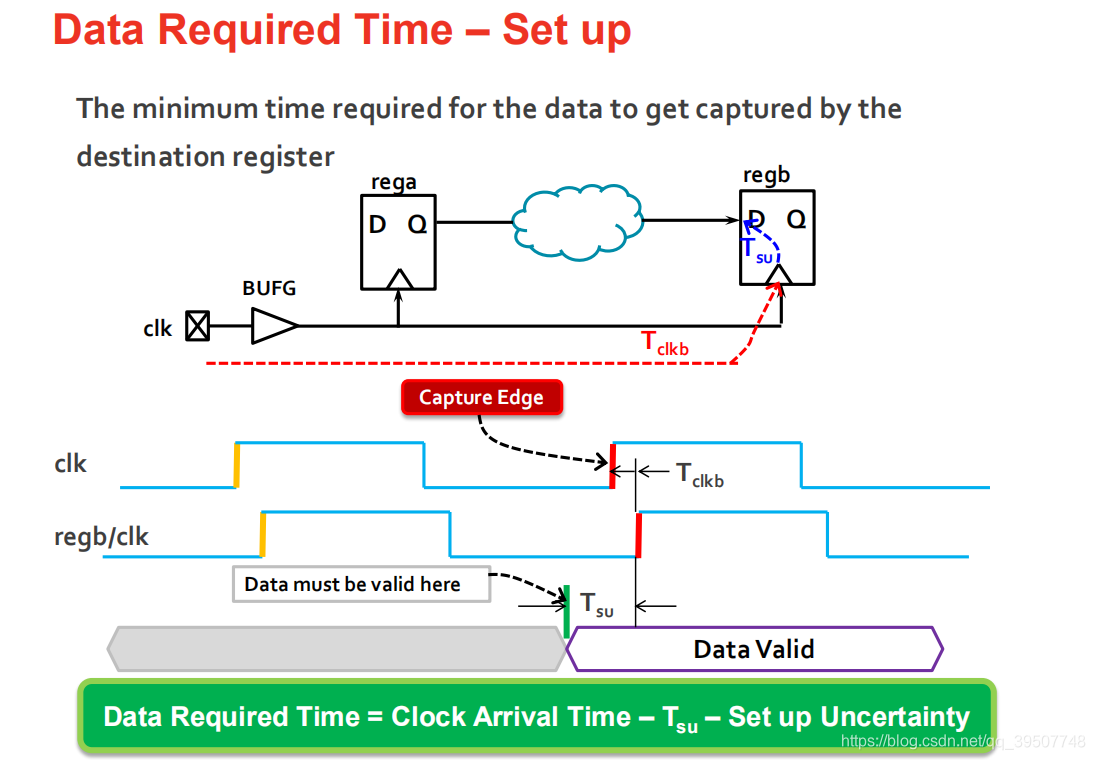

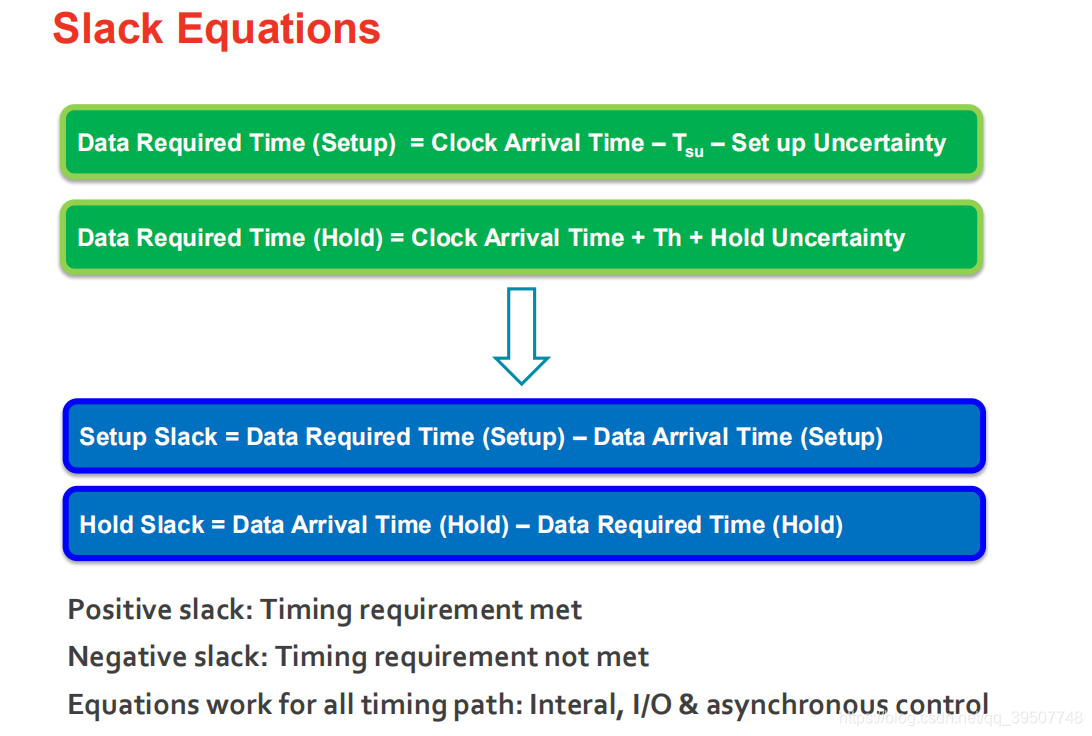

5、Data Required Time — Set up:建立时间的数据需求时间:

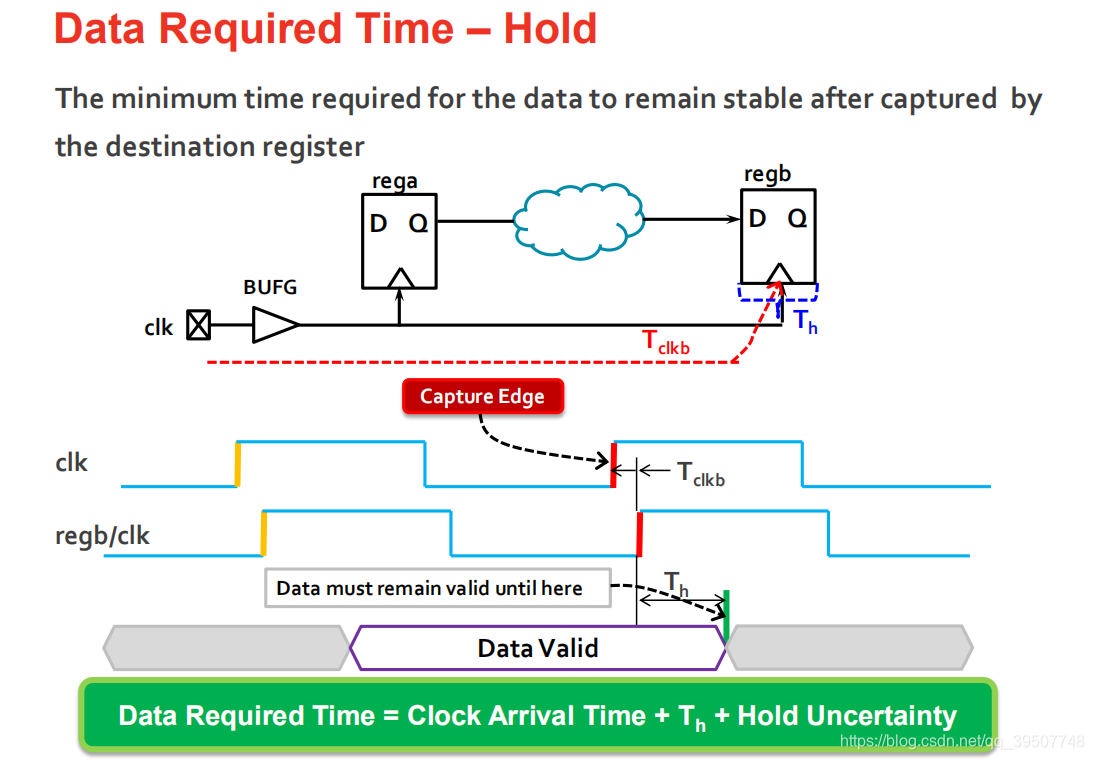

6、Data Required Time – Hold:保持时间的数据需求时间:

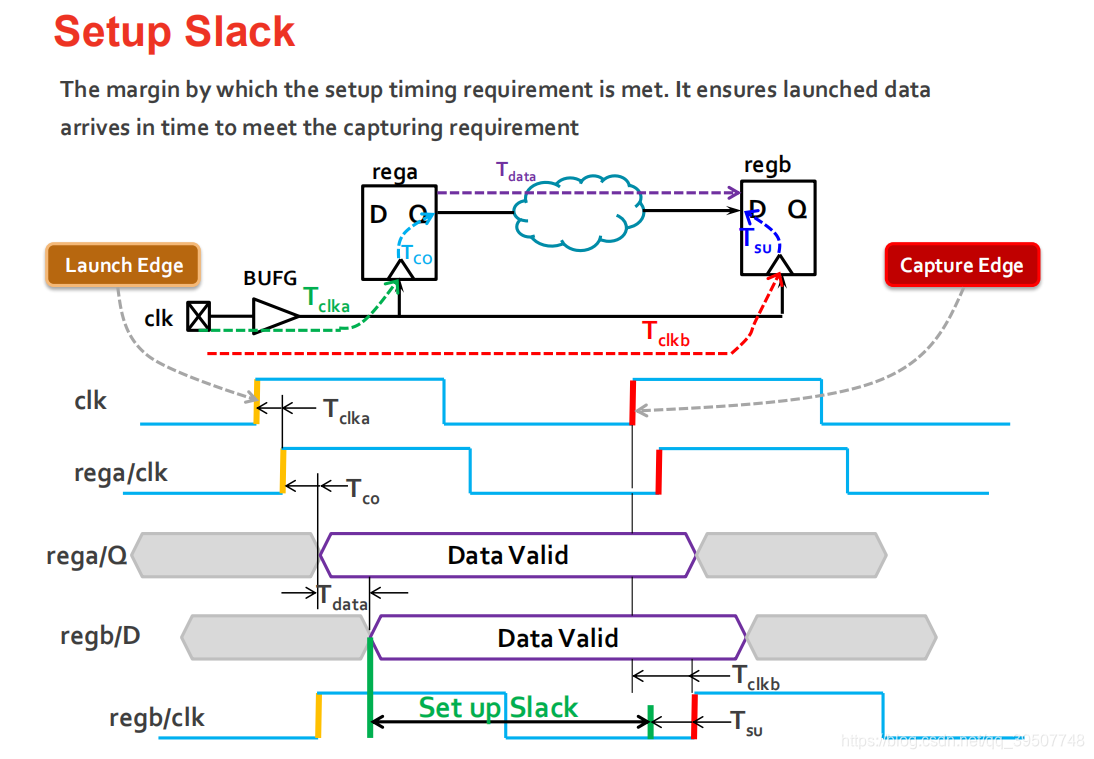

7、Setup Slack – 建立时间裕量

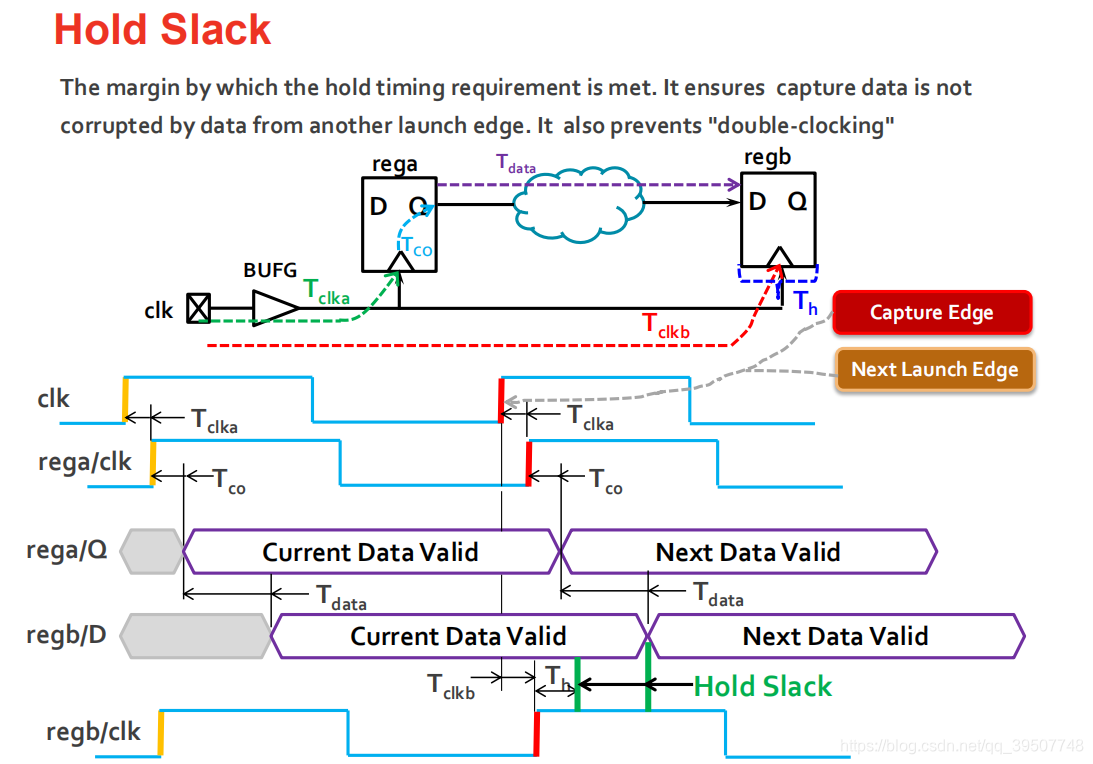

8、Hold Slack – 保持时间裕量

9、建立时间和保持时间裕量的公式

这里需要注意的是,Data Arrival Time(Setup)和Data Arrival Time(Hold)是不一样的,后者比前者多了一个clk,也即它代表的是下一个数据到达的时间,也即上一个数据无效的时间。

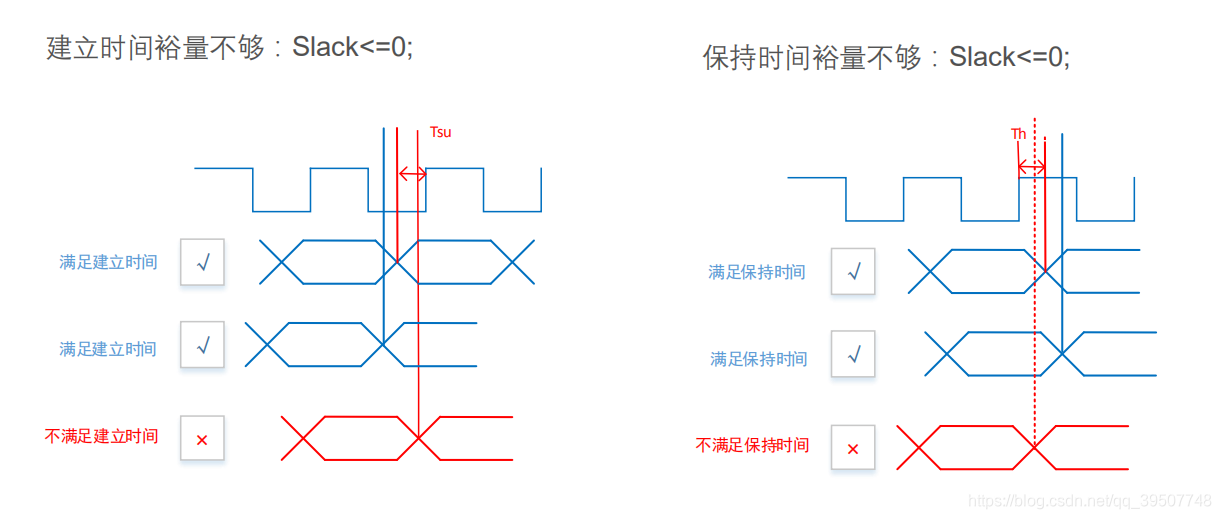

当时间裕量slack>0时满足时序要求,如果小于0则不满足,如下图所示:

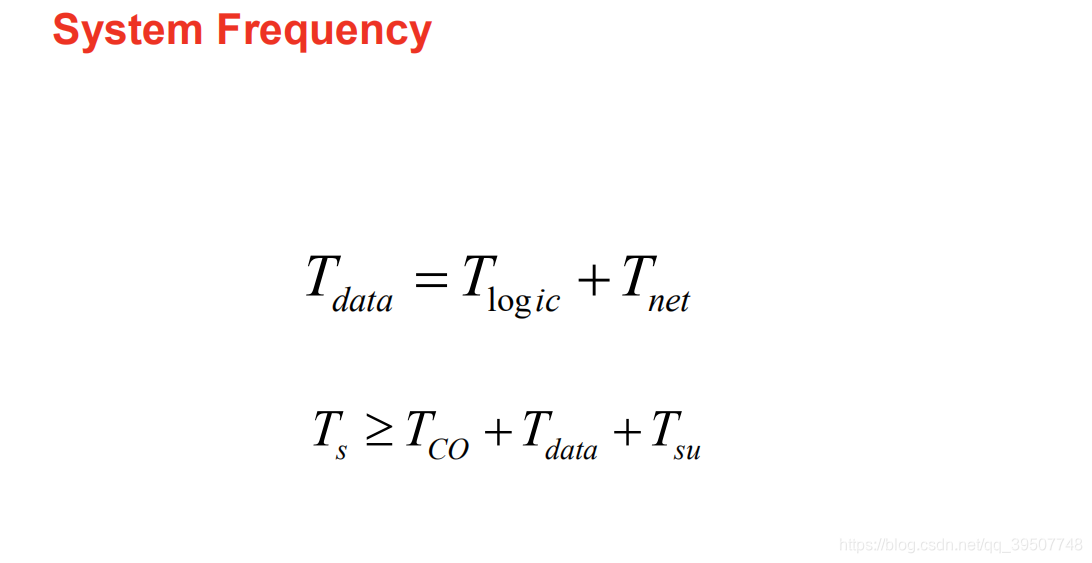

10、数据的延迟都有哪些?

| 参数名称 | 含义 |

|---|---|

| 建立时间Tsu | 器件工艺决定,是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。 |

| 保持时间Thold | 器件工艺决定,是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。 |

| Tco | 延迟由器件工艺决定,为寄存器时钟达到以后数据出现在输出端的延迟; |

| Tlogic | 组合逻辑处理时间,由用户的代码决定; |

| Tnet | 芯片内部布线延迟,由EDA工具决定; |

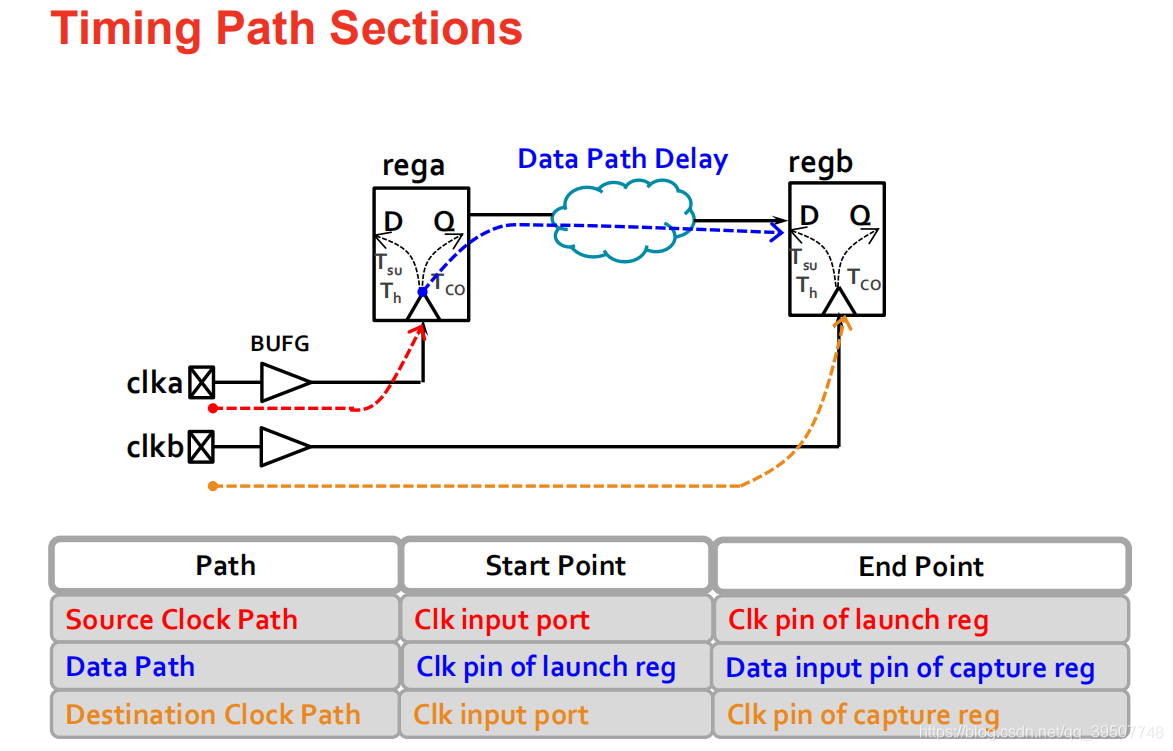

附:时序路径的三个部分

这里之所以要单独拿出来说,是因为你会发现在后面对某一个路径进行时序分析的时候,都是将时序路径分成这三部分;然后通过计算每一部分的延迟,再结合建立时间和保持时间,最终得到相应的slack(裕量),根据slack的值是否≥0以判断时序是否符合要求。

-

source clock path + data path = 实际的数据到达延迟路径;

-

T(destination clock path) - Ts(或者+Th) = 数据需求时间;

需要注意的是:

在计算数据需求时间时,如果是对建立时间进行时序分析,那么在T(destination clock path) - Ts中,destination clock path的初始时间就是一个clock周期;

而在对保持时间进行时序分析的时候,在T(destination clock path) +Th中,destination clock path的初始时间为0。