综合工具-DesignCompiler学习教程

-

7、Design Compiler 13讲,还有一个基本上很类似的专栏:https://www.cnblogs.com/xh13dream/tag/DC/,也可以参考。

Design Compiler 13讲中的部分内容:

Tcl与Design Compiler (二)——DC综合与Tcl语法结构概述

1、逻辑综合的概述

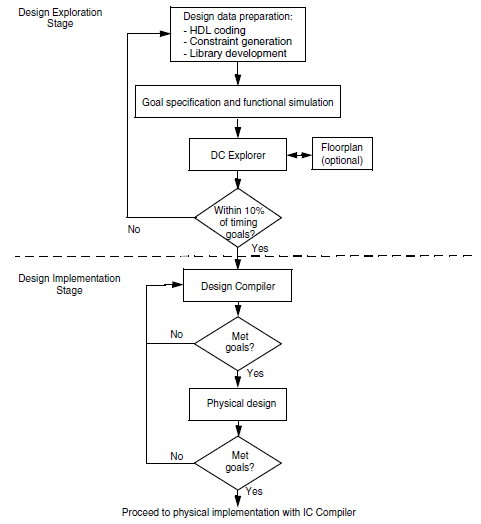

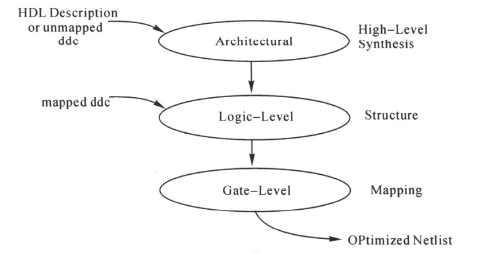

- DC工作流程分为三步

2、DC的三种启动方式

-

GUI

-

dc_shell

-

Batch mode

3、DC-Tcl语言的基本结构

Tcl与Design Compiler (三)——DC综合的流程

1、高层次设计的流程图

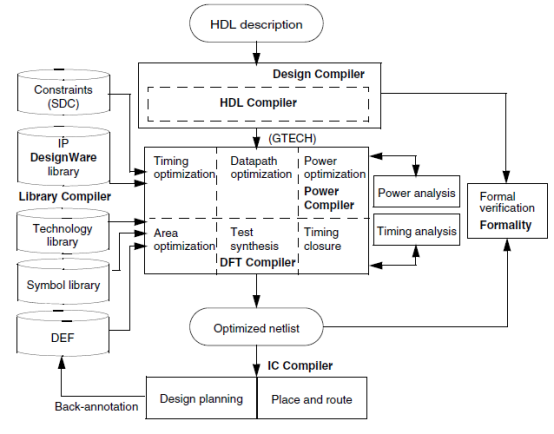

2、DC在设计流程中的位置

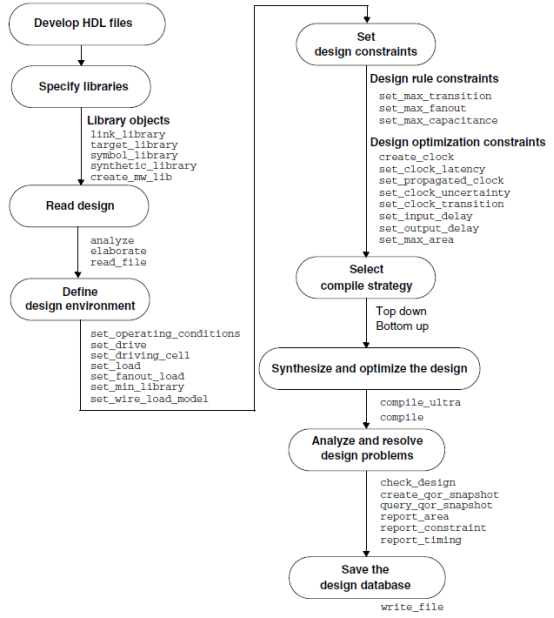

3、使用DC进行基本的逻辑综合的流程图与相应的命令

①准备设计文件

②指定库文件

③读入设计

④定义设计环境

⑤设置设计约束

⑥选择编译策略

⑦编译

⑧分析及解决设计中存在的问题

⑨存储设计数据

Tcl与Design Compiler (四)——DC启动环境的设置

(1)启动环境配置简述

(2).synopsys_dc.setup配置文件的书写

(3).synopsys_dc.setup的讲解

Tcl与Design Compiler (五)——综合库(时序库)和DC的设计对象

(1)标准单元库

-

①概述

一个ASIC综合库包括如下信息:

·一系列单元(包括单元的引脚)。

·每个单元的面积(在深亚微米中,一般用平方微米表示,在亚微米工艺下,一般用门来称呼,至于具体的单位,可以咨询半导体制造商)。

·每个输出引脚的逻辑功能。

·每个输入到输出的传递延时,输出到输出的传递延时;inout到输出的传递延时。

-

②内容与结构

Synopsys的工艺库是一个.lib文件,经过LC编译后,产生.db文件。工艺库文件主要包括如下信息:

·单元(cell)(的信息):(主要有)功能、时间(包括时序器件的约束,如建立和保持)、面积(面积的单位不在里面定义,可按照规律理解,一般询问半导体厂商)、功耗、测试等。

·连线负载模型(wire load models):电阻、电容、面积。

·工作环境/条件(Operating conditions):制程(process)(电压和温度的比例因数k,表示不同的环境之间,各参数缩放的比例)

·设计规则约束(Design ):最大最小电容、最大最小转换时间、最大最小扇出。

工艺库的结构如下所示:

(2)DC的设计对象

-

在了解了综合库之后,下面介绍一下DC的设计对象,虽然这个设计对象相对于综合库没有那么重要,但是还是要了解一下的。

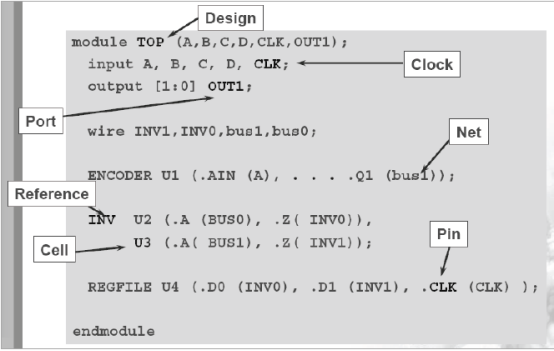

对于一个verilog代码模块,我们知道这是一个模块的名字是什么,这个模块的功能是什么,这个模块有哪些端口等等信息。但是对于DC来说,它不想我们那么理解,给它一个verilog模块,它把这个模块的内容当做设计对象(简称对象)来看。DC支持的对象和解释如下所示:

DC支持8中设计对象:

Design :具有某种或多种逻辑功能的电路描述;

Cell :设计的 instance;

Reference :cell 或 instance 在库中定义的名字;

Port :design 的输入、输出;

Pin :design 中 cell 的输入、输出;

Net :ports 和 pins 之间或 pins 之间的信号名;

Clock :被定义为时钟源的 pin 或 port;

Library :cell 的集合,如: starget_library,link_library;

(3)Design Ware 库

- DesignWare是Synopsys提供的知识产权(Intellectual Property,简称IP)库。IP库分成可综合IP库(synthesizable IP,SIP) ,验证IP库(Verification IP,VIP)和生产厂家库(foundry 1ibraries)。IP库中包含了各种不同类型的器件。这些器件可以用来设计和验证ASIC, SoC和FPGA。

Tcl与Design Compiler (六)——基本的时序路径约束

1、时序路径与关键路径

2、常见的时序路径约束

- 建立时间、保存时间和亚稳态

- 时钟的约束(寄存器-寄存器之间的路径约束)

- 输入延时的约束

- 输出延时的约束

- 组合逻辑的约束

Tcl与Design Compiler (七)——环境、设计规则和面积约束

1、工作环境属性约束

- 设置环境条件(set_operating_conditions)

- 设置线负载模型(set_wire_load_model)

- 设置驱动强度(set_drive与set_driving_cell)

- 设置电容负载(set_load与set_load load of)

2、设置设计规则约束

-

最大电容(max_capacitance)

-

最大转换时间(max_transition)

-

最大扇出(max_fanout)

3、面积约束

Tcl与Design Compiler (八)——DC的逻辑综合与优化

1、DC的逻辑综合及优化过程

主要包括:

- 第一阶段的结构级的优化(Architectural-Level Optimization)

- 第二阶段的逻辑级优化(Logic-Level Optimization)

- 最后阶段的门级优化(Gate-Level Optimization)

2、时序优化及方法

-

(1)当违规得比较严重时,也就是时序的违规(timing violation)在时钟周期的25%以上时,就需要重新修改RTL代码了。

-

(2)时序违规在25%以下,有下面的时序优化方法:

①使用compile_ultra命令(在拓扑模式下运行)

compile_ultra命令包含了以时间为中心的优化算法,在编译过程中使用的算法有:

- A 以时间为驱动的高级优化(Timing driven high-level optimization);

- B 为算术运算选择适当的宏单元结构;

-

- C 从DesignWare库中选择最好的数据通路实现电路;

- D 映射宽扇入(Wide-fanin)门以减少逻辑级数;

- E 积极地使用逻辑复制进行负载隔离;

- F 在关键路径自动取消层次划分(Auto-ungrouping of hierarchies)。

- set_dont_retime

- set_optimize_registers -design Pipeline

②使用compile -scan -inc 命令

③使用自定义路径组合、关键范围

Design Compiler中,常用report_timing命令来报告设计的时序是否满足目标。执行report_timing命令时,DC做4个步骤:

- 把设计分解成单独的时间组;

- 每条路径计算两次延迟,一次起点为上升沿,另一次起点为下降沿;

- 在每个路径组里找出关键路径(critical path),即延迟最大的路径;

- 显示每个时间组的时间报告。

DC的默认行为是对关键路径作优化。当它不能为关键路径找到一个更好的优化解决方案时,综合过程就停止。DC不会对**次关键路径(Sub-critical paths)**作进一步的优化。因此,如果关键路径不能满足时序的要求,违反时间的约束,次关键路径也不会被优化,它们仅仅被映射到工艺库。

使用自定义路径组合后,综合时,工具只对一个路径组的最差(延时最长)的路径作独立的优化,但并不阻碍另外自定义路径组的路径优化。产生自定义路径组也可以帮助综合器在做时序分析时采用各自击破(divide-and-conquer)的策略,因为report_timing命令分别报告每个时序路径组的时序路径。

自定义路径组: 用户自定义路径组后,如果设计的总性能有改善,DC允许以牺牲一个路径组的路径时序(时序变差)为代价,而使另一个路径组的路径时序有改善。在设计中加入一个路径组可能会使时序最差的路径时序变得更差。

关键范围: 关键范围不允许因为改进次关键路径的时序而使同一个路径组的关键路径时序变得更差。如果设计中有多个路径组,我们只对其中的一个路径组设置了关键范围,而不是对整个设计中的所有路径组都设置了关键范围,DC只会并行地对几条路径优化,运行时间不会增加很多。

④重新划分模块(Repartition Block)

Tcl与Design Compiler (九)——综合后的形式验证

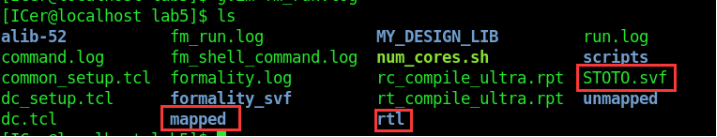

1、准备好RTL文件、综合优化后的文件以及带有优化映射信息的SVF文件:

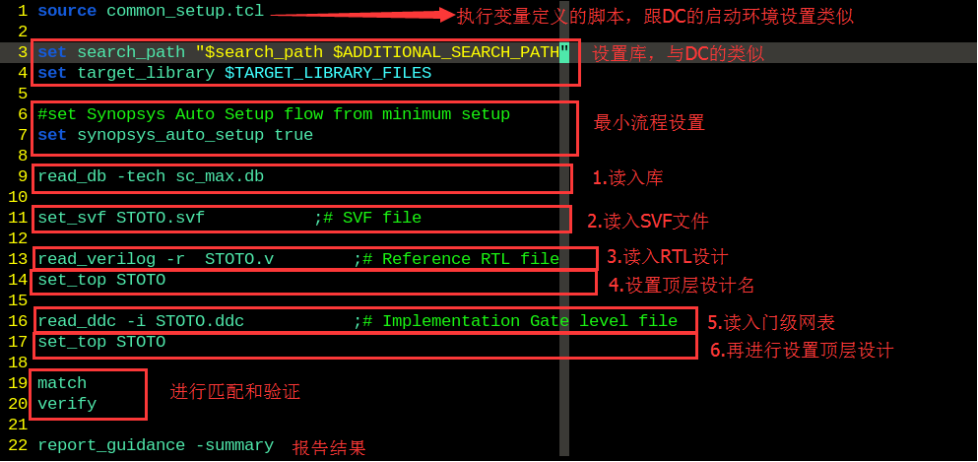

2、书写相应地流程文件:

3、执行我们写的脚本

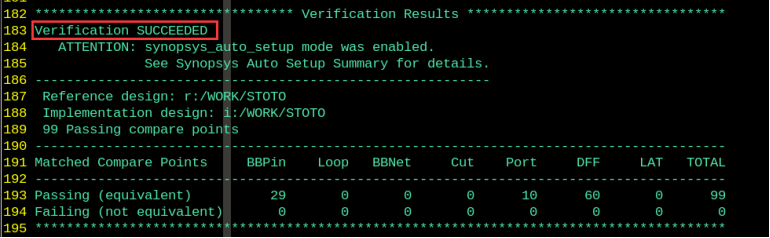

得到结果如下,说明验证通过了:

Tcl与Design Compiler (十二)——综合后处理

1、概述

-

.sdc文件:标准延时约束文件

-

Scan_def.def文件:DFT、形式验证可能用到

-

.sdf、.v文件:标准延时格式和网表格式文件,用于后仿真

2、综合网表处理与生成

-

(1)综合网表的处理:

-

(2)相关文件的生成

3、时序检查与报告的生成

-

(1)时序报告的查看:

第一部分是路径信息部分

第二部分是路径延迟部分

第三部分是路径要求部分

第四部分是时间总结部分

-

(2)timing_report的选项与debug

-

(3)设计违规检查

-

(4)查看分组优化结果

2、综合网表处理与生成

-

(1)综合网表的处理:

-

(2)相关文件的生成

3、时序检查与报告的生成

-

(1)时序报告的查看:

第一部分是路径信息部分

第二部分是路径延迟部分

第三部分是路径要求部分

第四部分是时间总结部分

-

(2)timing_report的选项与debug

-

(3)设计违规检查

-

(4)查看分组优化结果