CSAPP(第三版)第四章处理器体系结构

Y86-64 指令集体系结构

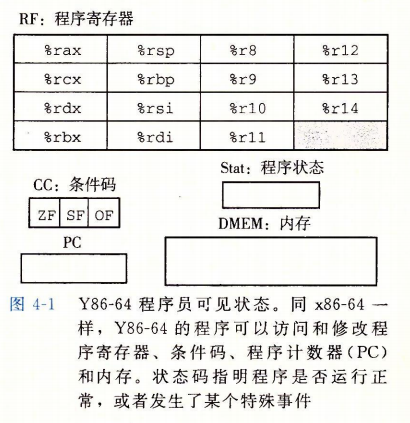

程序员可见的状态

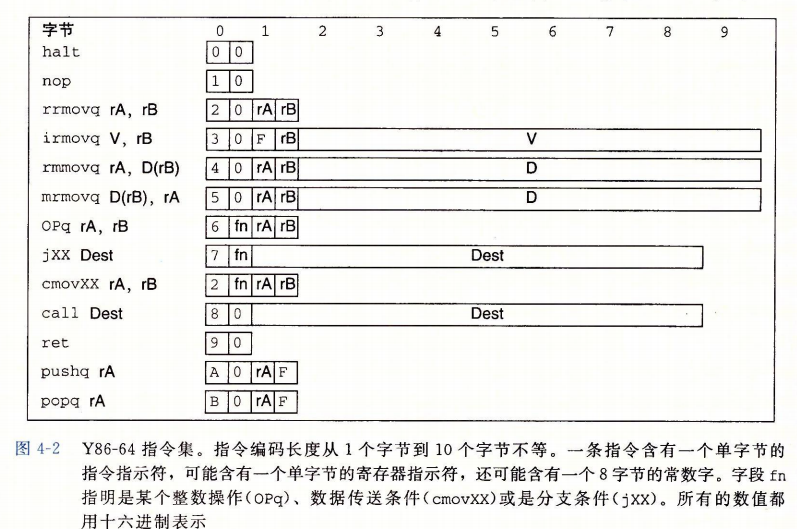

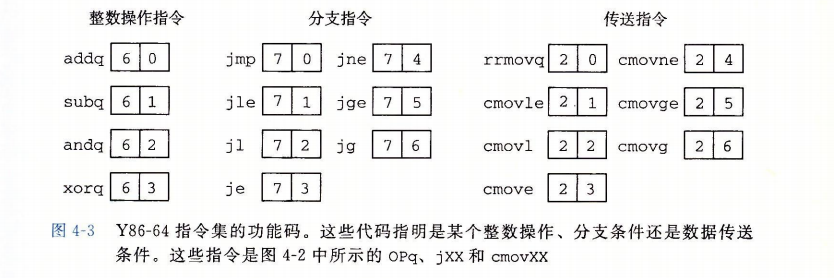

Y86-64指令集

指令编码

每条指令的第一个字节表明指令的类型。这个字节分为两个部分,每部分4位:高4位是代码部分,低4位是功能部分。

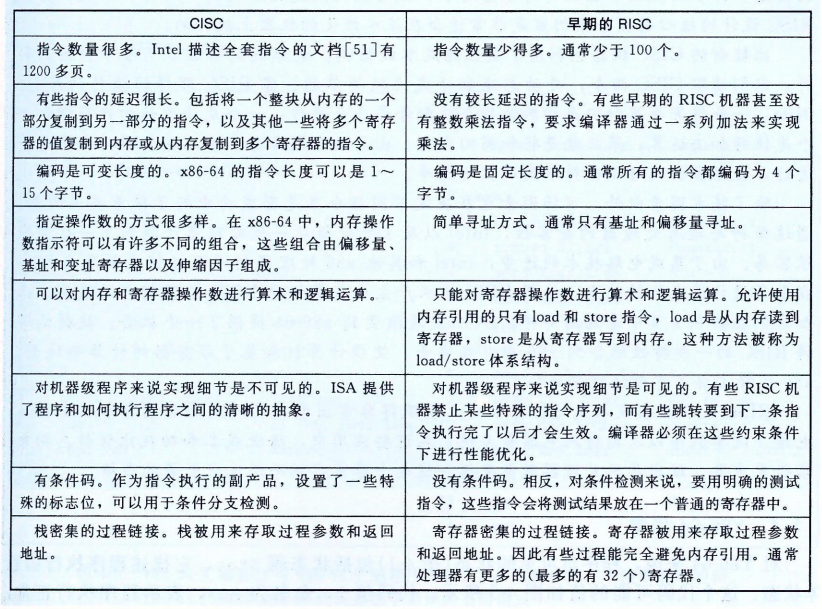

RISC和CISC指令集

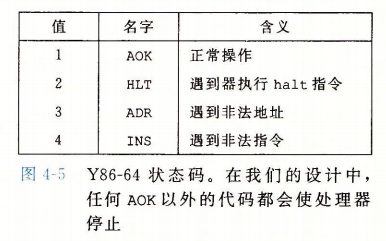

Y86-64异常

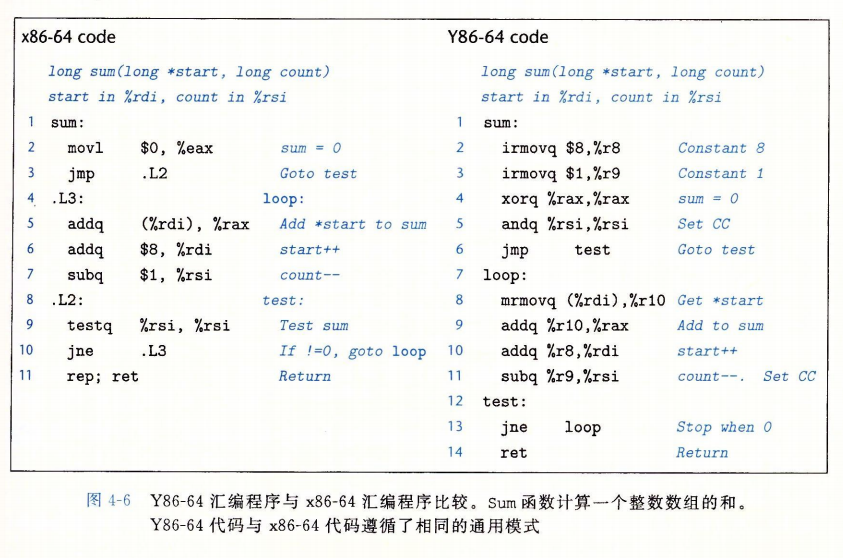

Y86-64程序

逻辑设计和硬件控制语言HCL

硬件设计中,用电子电路来计算对位进行运算的函数,以及在各种存储器中存储位。

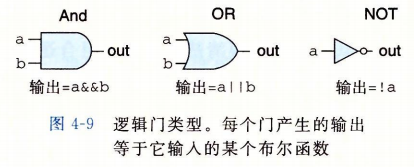

逻辑门

组合电路和HCL布尔表达式

将很多的逻辑门组合成一个网,就能构建计算块,称为组合电路。如何构建这些网有几个限制:

- 每个逻辑门的输入必须连接到下述选项之一:1.一个系统输入,2.某个存储器单元的输出,3.某个逻辑门的输出

- 两个或多个逻辑门的输出不能连接在一起。否则他们可能会使线上的信号矛盾,可能会导致一个不合法的电压或者电路故障。

- 这个网必须是无环的。也就是在网络中不能有路径经过一系列的门儿形成一个回回路,这样的回路会导致该网络计算的函数有歧义。

字级的组合电路和HCL的整数表达式

在HCL中,我们将所有字级的信号都声明为int,不指定字的大小。

集合关系

在处理器设计中,很多时候都需要将一个信号与许多可能匹配的信号做比较,以此来检测正在处理的某个指令代码是否属于某一类指令代码

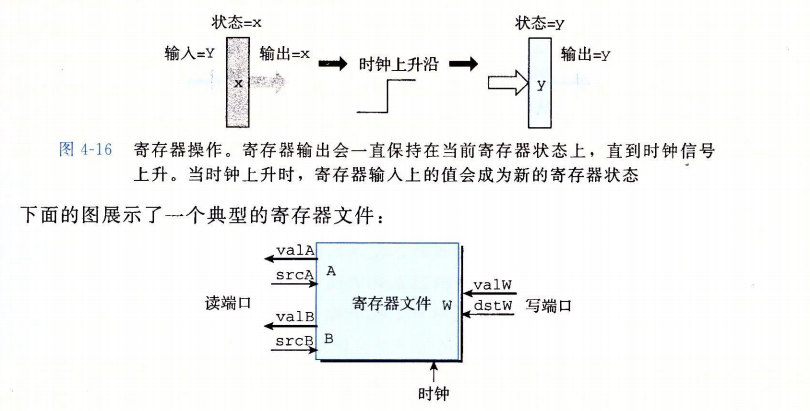

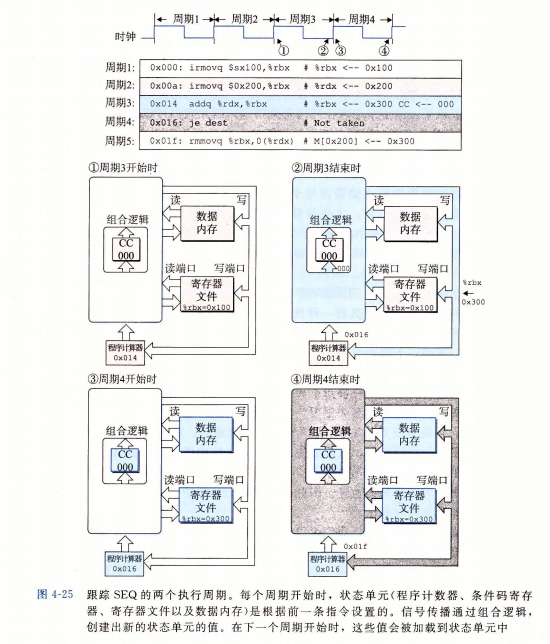

存储器和时钟

存储设备都是由同一个时钟控制的,时钟是一个周期性信号,决定什么时候要把新值加载到设备中。考虑两类存储器设备:

- 时钟寄存器存储单个位或字,时空信号控制集训期加载输入值。

- 随机访问存储器存储多个字,用地址来选择该读或者改写哪个字。

Y86-64的顺序实现

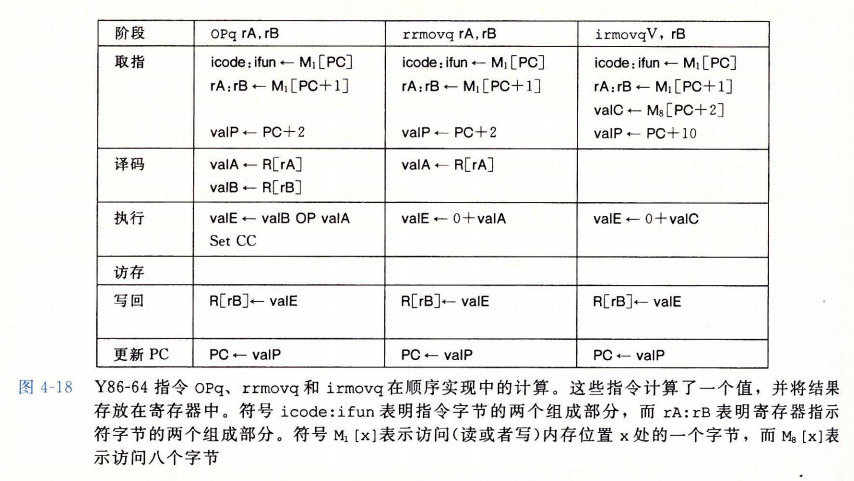

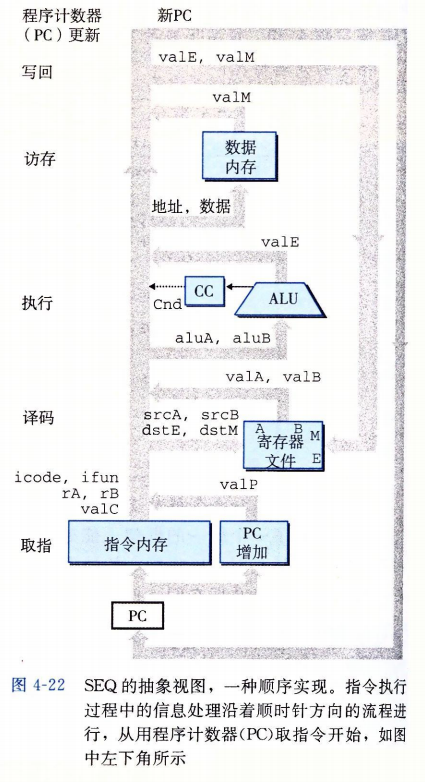

将处理组织成阶段

- 处理一条指令包括很多操作,大致分成以下6个阶段:

- 取指:取指阶段从内存读取指令字节,地址为程序计数器的值。

- 译码:译码阶段从结存器人间读入最多两个操作数,得到值valA和/或valB。

- 执行:在执行阶段,算数/逻辑单元要么执行指令知名的操作,计算内存引用的有效地址,要么增加或者减少栈指针。

- 访存:方寸阶段可以将数据写入内存,或者从内存读取数据。读出的值为valM。

- 写回:写回阶段最多可以写两个结果到寄存器文件。

- 更新PC:将PC设置成下一条指令的地址。

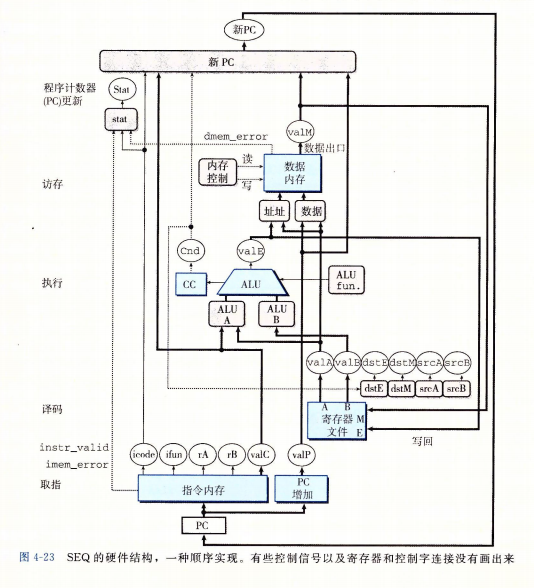

SEQ硬件结构

SEQ时序

SEQ阶段的实现

具体参考教材

流水线的通用流程

流水线的一个重要特性就是提高了系统的吞吐量,也就是单位时间内服务的顾客总数,不过他也会轻微的增加延迟,也就是服务一个用户所需要的时间。

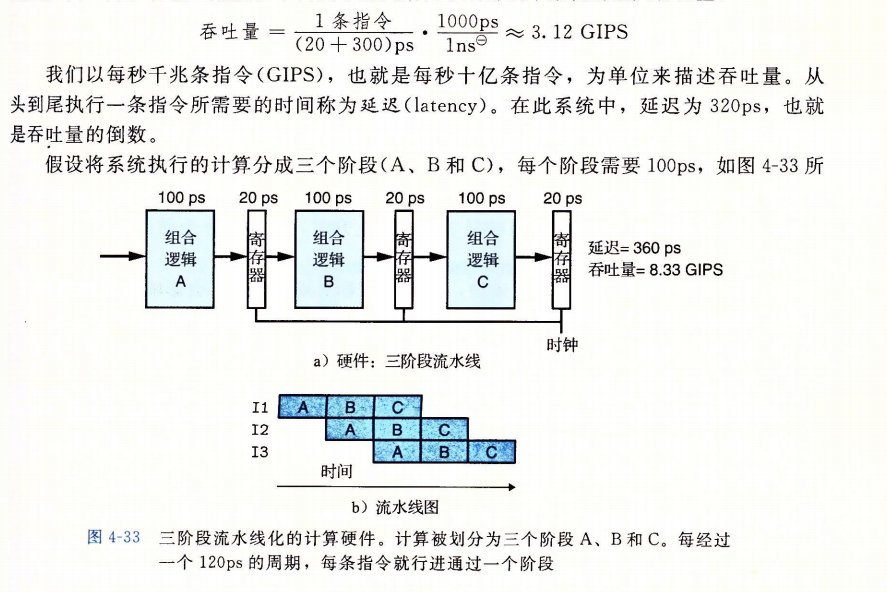

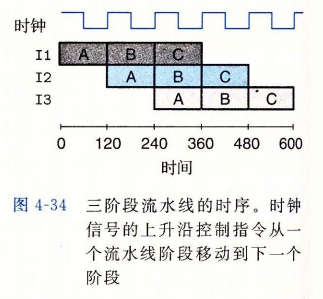

计算流水线

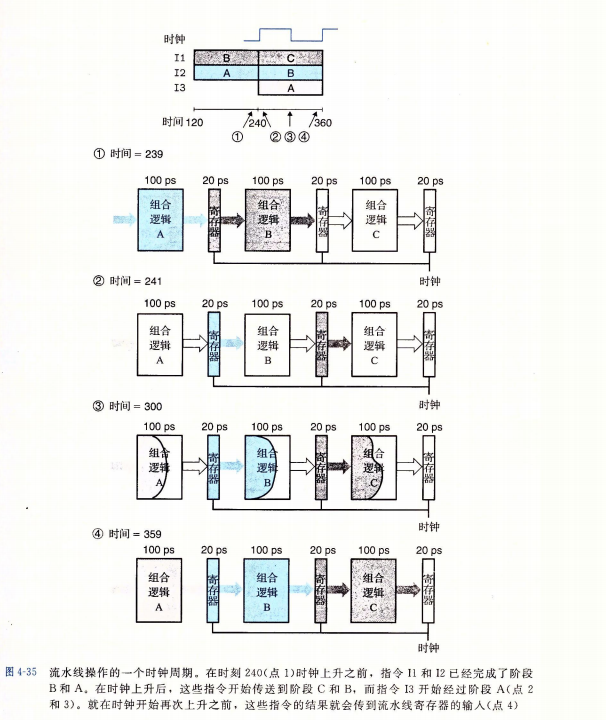

流水线操作的详细说明

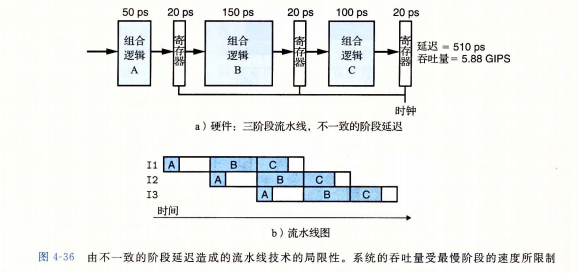

流水线的局限性

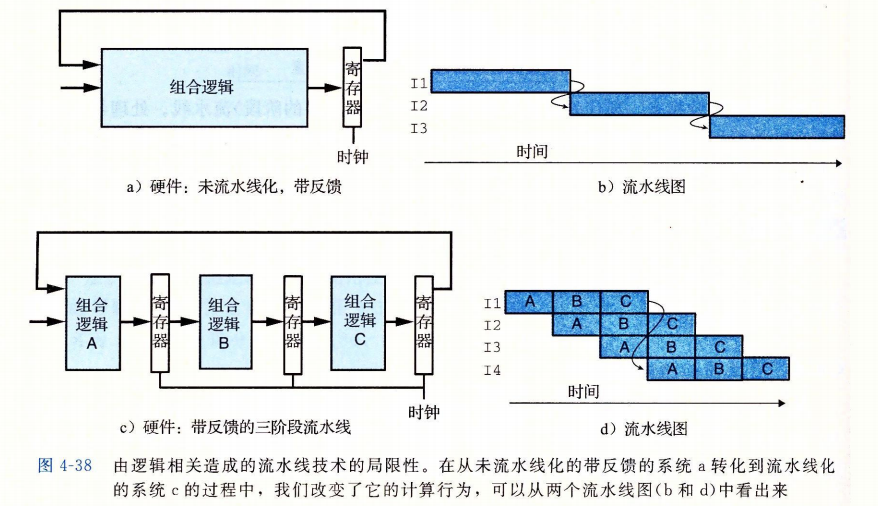

带反馈的流水线系统

Y86-64的流水线实现

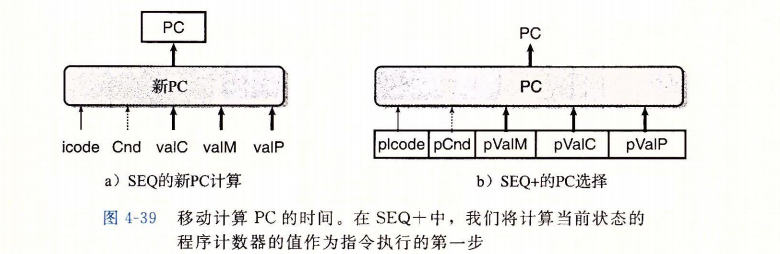

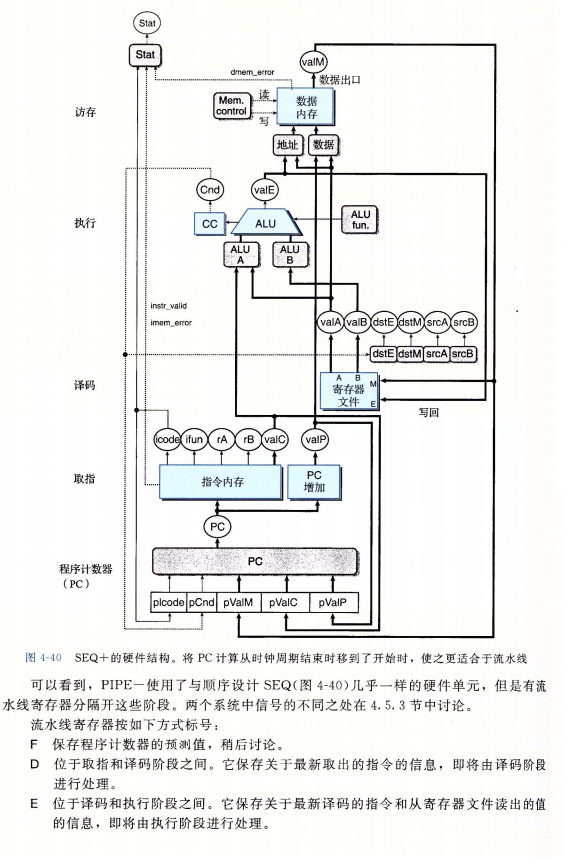

SEQ+:重新安排计算阶段

插入流水线寄存器

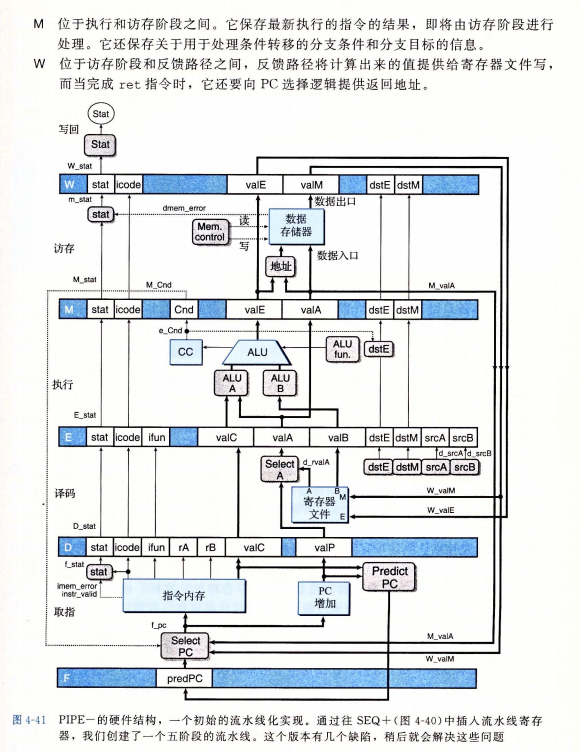

在SEQ+的各个阶段志建插入流水线寄存器,并对信号重新排列,得到PIPE-处理器,这里的-代表这个处理器和最红的处理器设计相比,性能要差一点。

对信号进行重新排列和标号

在流水线设计中,与各个指令相关联的这些值有多个版本,会随着指令一起流过系统。

预测下一个PC

流水线化设计的目的就是每个时钟周期都发射一条新指令,也就是说每个时钟周期都有一条新指令进入执行阶段并最终完成。

流水线冒险

PIPE-结构是常见一个流水线化的Y86-64处理器的好开端。不过将流水线技术引入一个带反馈的系统,当相邻指令间存在相关时会导致出现问题。在完成我们的书籍之前,必须解决这个问题。这些相关有两种形式:1.数据相关,2.控制相关。这些相关可能会导致流水线产生计算错误,称为冒险。

- 用暂停来木棉数据冒险:暂停是避免冒险的一种常用技术,暂停时,处理器会停止流水线中一条或者多条指令,直到冒险条件不在满足。

- 用转发来不免数据冒险:

- 用加载/使用数据冒险

- 避免控制冒险

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 【自荐】一款简洁、开源的在线白板工具 Drawnix

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· Docker 太简单,K8s 太复杂?w7panel 让容器管理更轻松!