指令流水线基础知识复习

-

流水线一般分为五段 : IF(取指) ID(译码) EX(执行) MEM(访存) WB(写回)

-

三种冒险 :

1)结构冒险 : 因硬件资源满足不了指令重叠执行的要求而发生的冒险。

2)数据冒险 : 当指令在流水线中重叠执行时,因需要用到前面指令的执行结果而发生的冒险。

3)控制冒险 : 流水线遇到分支指令和其它会改变PC值的指令所引起的冒险。

指令集并行

概念 :

指存在于指令一级即指令间的并行性, 主要是指机器语言一级, 如存储器访问指令、整型指令、浮点指令之间的并行性等。

主要特点:

并行性由处理器硬件和编译程序自动识别和利用, 不需要程序员对顺序程序作任何修改。

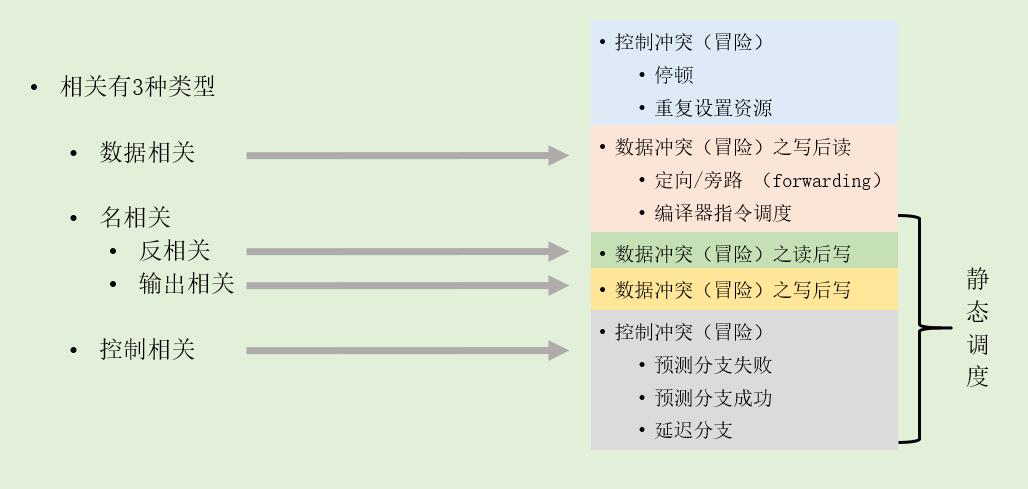

相关的概念:

相关是指两条指令之间存在某种依赖关系,是程序固有的一种属性。可分为 数据相关 、 名相关 、 控制相关等。

解决相关的两类方案:

-

保持相关,但是避免发生冲突。 -- 指令调度

-

通过代码变换,消除相关。 -- 寄存器重命名(消除 WAR WAW)

基本编译技术 - 循环展开 与 指令调度

虽然看不懂书上的空转周期是怎么来的,但是这俩加起来牛逼就完了

动态调度解决数据冒险

基本思想:

相关与流水线冲突:

需要知道的几个基本概念 :

静态调度 : 是依靠编译器对代码进行调度,也就是在代码被执行之前进行调度;通过把相关的指令拉开距离来减少可能产生的停顿。

动态调度 : 在程序的执行过程中,依靠专门硬件对代码进行调度,减少数据相关导致的停顿。

指令顺序执行:指令放入流水线的顺序和指令完成的顺序一致;

指令乱序执行:指令放入流水线的顺序和指令完成的顺序不一致,也就是说有些指令进入流水线后被阻塞的,而在其后进入流水线的指令先完成了。

读数据的猴急之 RAW 冲突 (写后读) : 还没写完就给读走了,这一冒险是最常见的类型,与真数据相关相对应。

插队写之 WAW 冲突 (写后写) : j 在 i 之前写入数据, 导致本该被 j 覆盖掉的 i 值,成为最后留在该位置的值。这种冒险与输出相关相对应。

写数据的猴急之 WAR 冲突 (读后写) : 还没有读取,就将新的值写入了目标位置,导致读取的值是新值。

第一个字母抢先执行导致

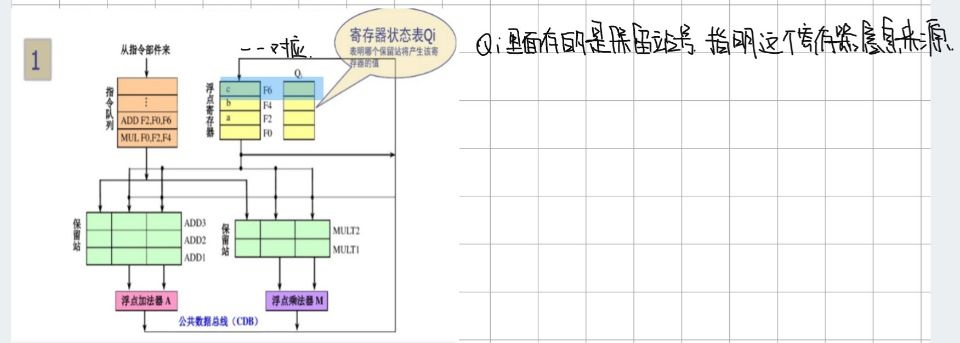

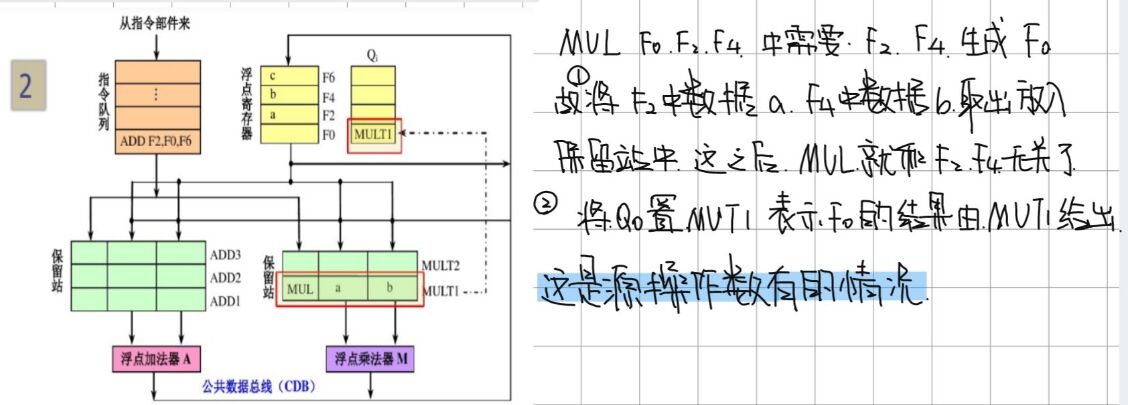

Tomasulo 算法

核心思想

1) 记录和检测指令相关,操作数一旦就绪就立即执行,把发生 RAW 冲突的可能性减少到最小。

2)通过寄存器换名来消除 WAR 冲突和 WAW 冲突。

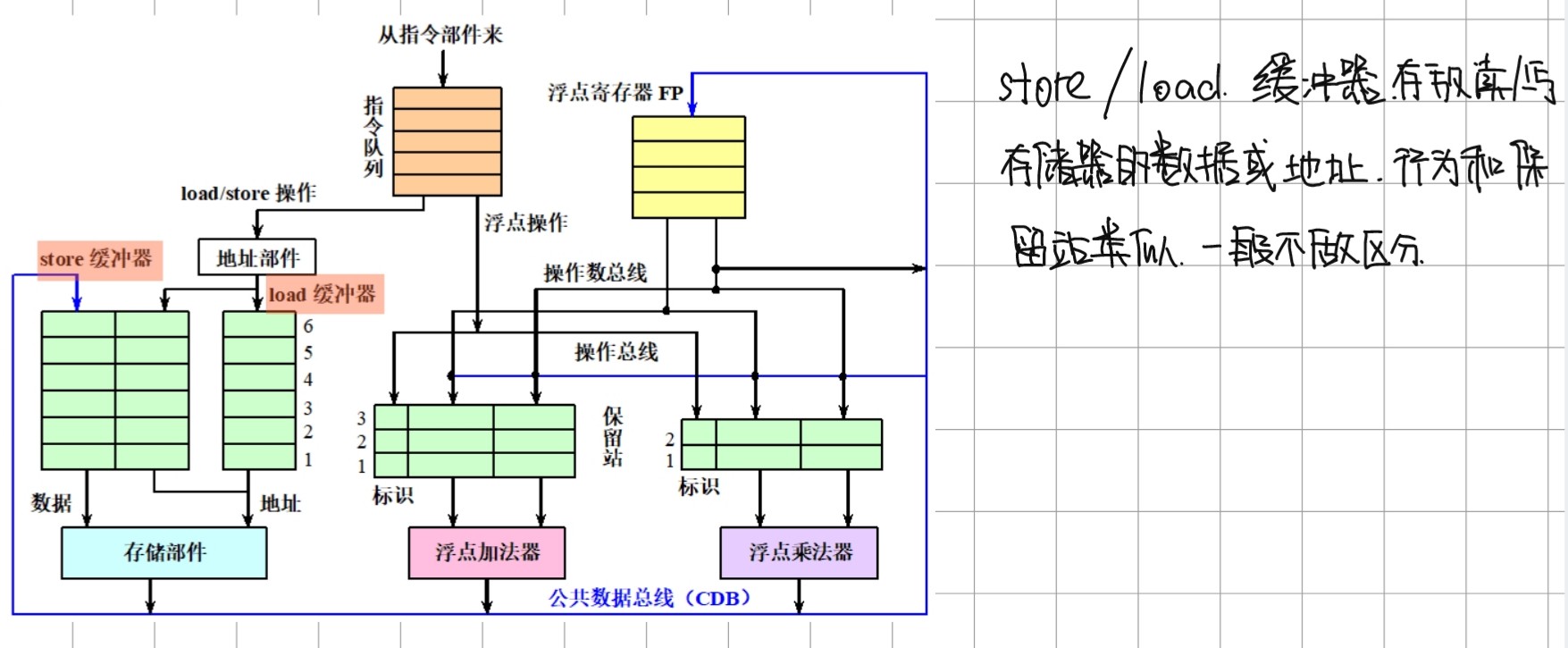

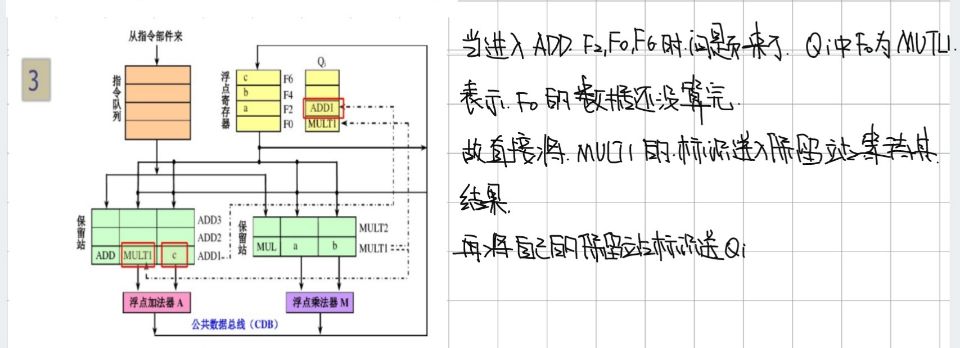

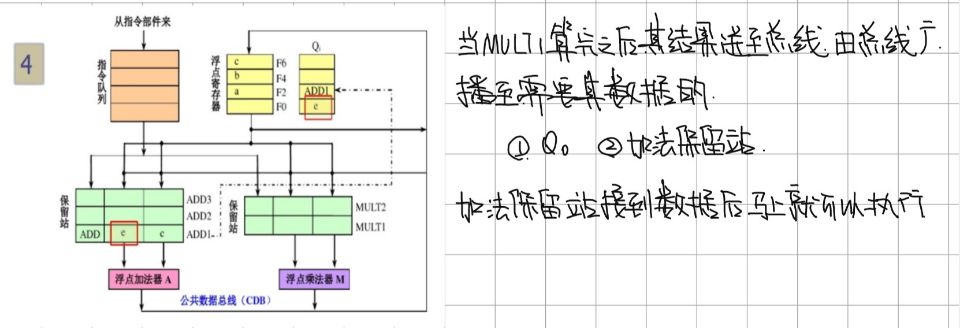

基本结构

一个简单的 用来帮助理解的栗子

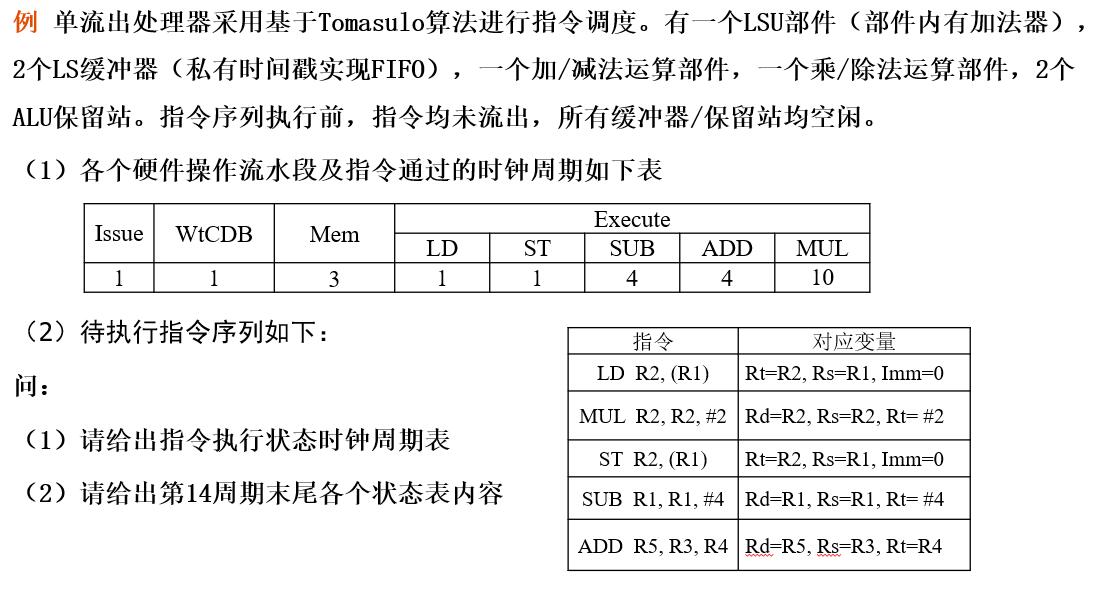

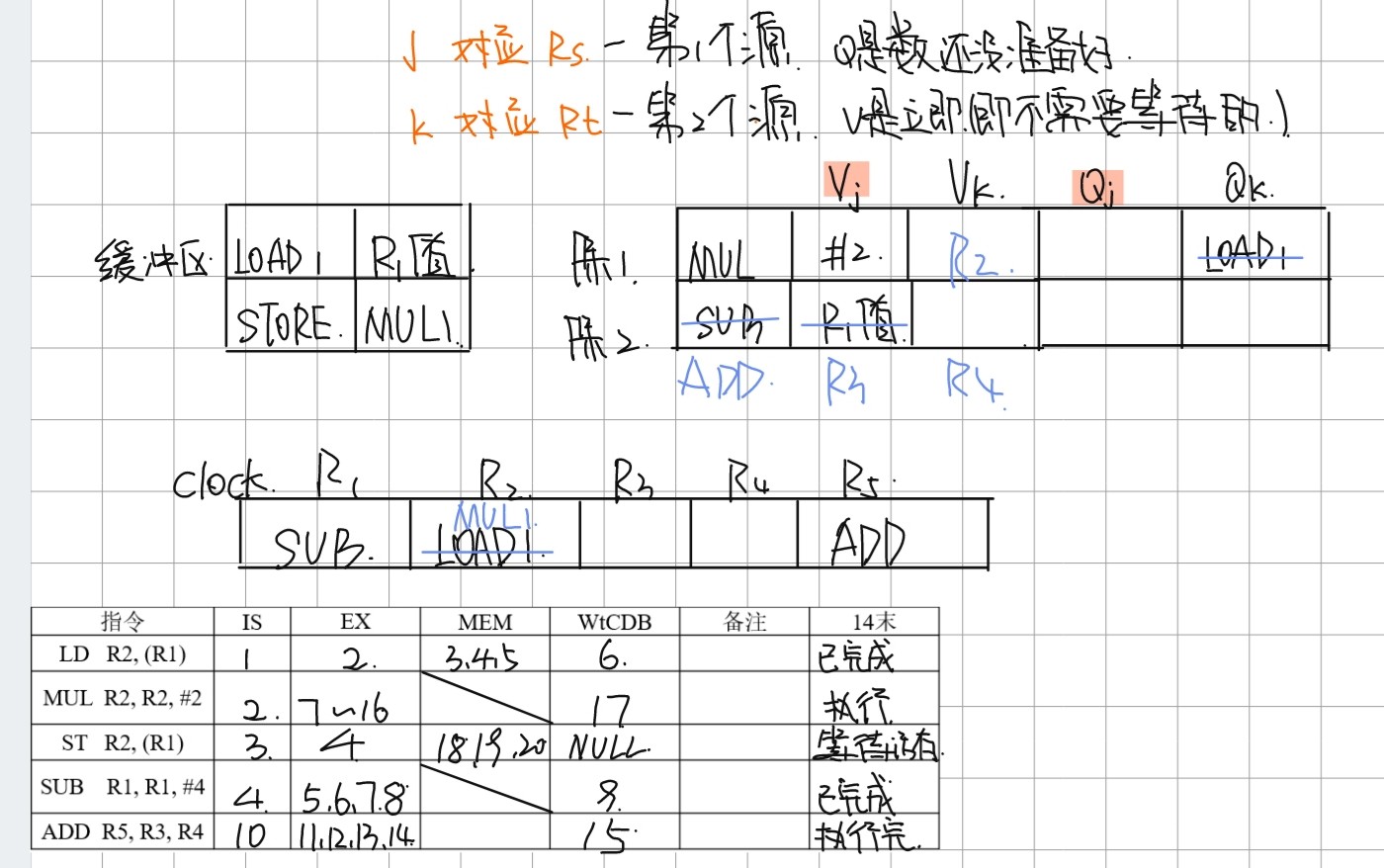

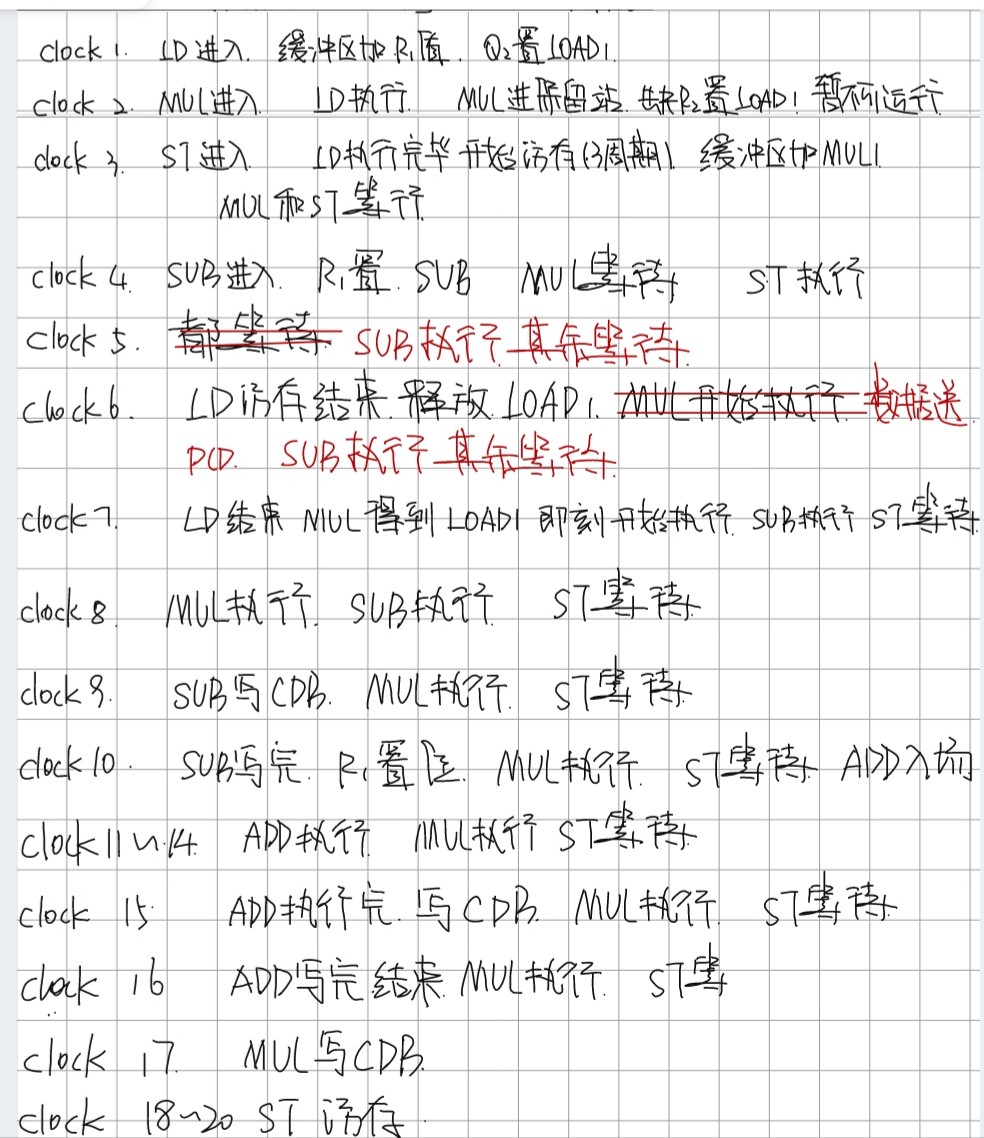

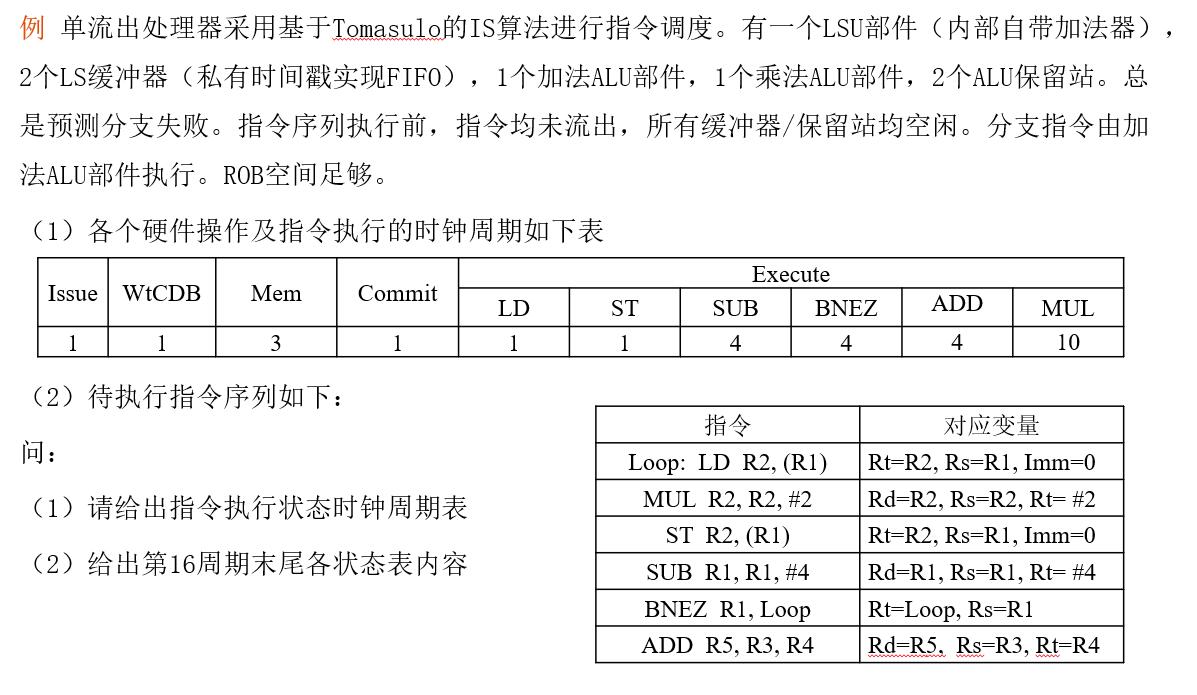

一道更为复杂的例题

要点总结

-

指令按照原有的顺序进入指令队列,并按照原有的顺序流出,但是不一定按照原有的顺序执行。

-

操作数未就绪的指令在保留站中等待,操作数就绪的指令可以先被执行。

-

通过寄存器换名消除了名相关,从而解决了RAW WAW WAR 冲突。

换名 : a. 将寄存器名字换为了产生该操作数的保留站号 b. 将寄存器的名字换为了寄存器的内容存放在保留站里面

-

不存在结构冲突

-

不可以处理分支冒险,一旦指令中出现分支指令,分支指令后面的指令都需要等待,不能流出,直到分支确认

-

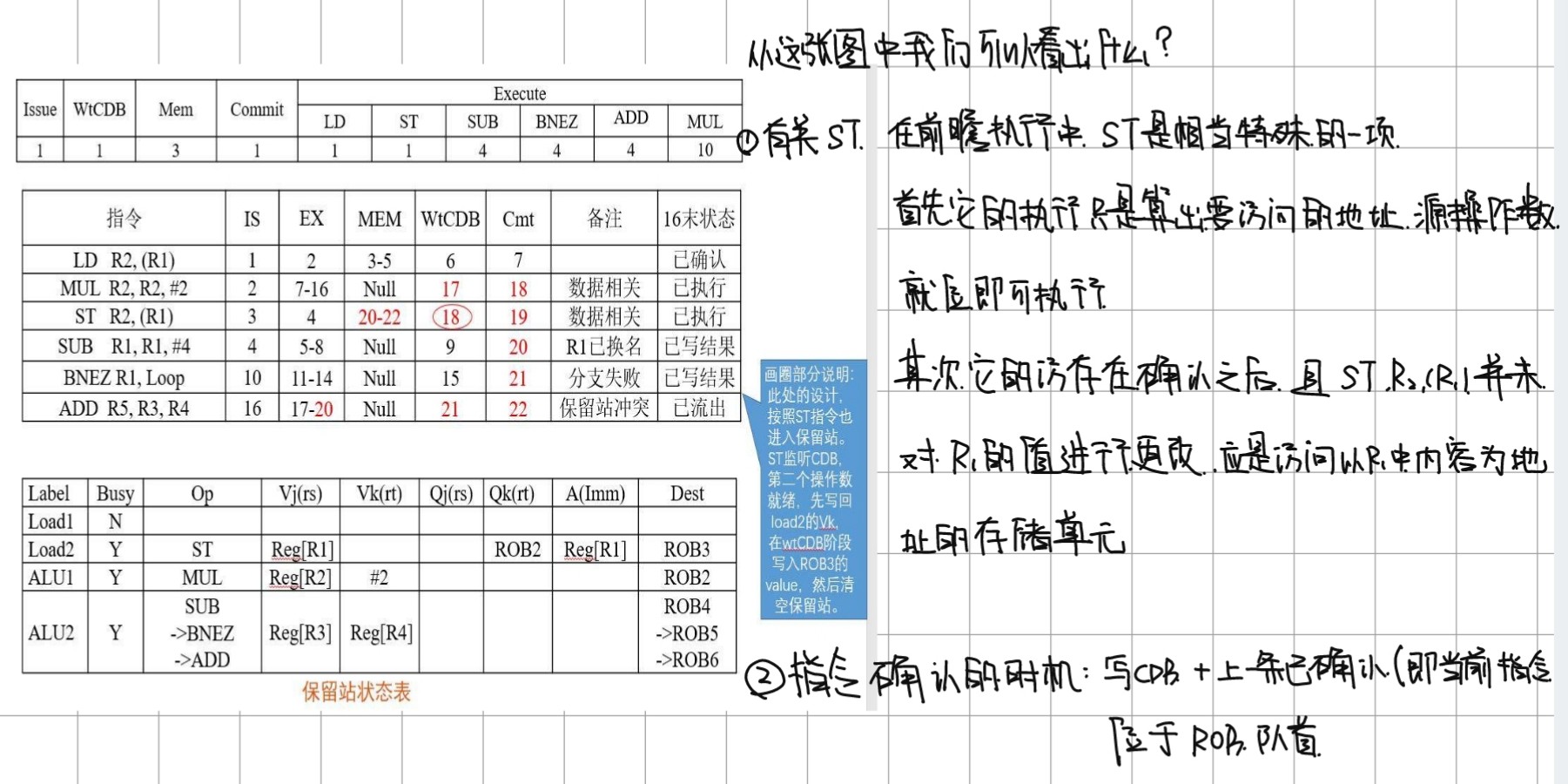

需要注意的点 : a. 一个是从Load/store指令要按照FIFO次序访存; b. store指令执行阶段和写结果阶段进入的条件。

动态调度解决控制冒险

前置概念定义

动态分支预测技术与静态分支预测技术的区别 :

静态分支预测技术所进行的操作事先预定好的,与分支的实际执行情况无关;

动态分支预测技术的方法在程序运行时根据分支执行过去的表现预测其将来的行为(如果分支行为发生了变化,预测结果也跟着改变,此外有更好的预测准确度和适应性)

什么是 “ 分支指令过去的表现 ” :

就是记录分支的历史信息。在预测错误的时候,作废已经预取和分析的指令,恢复现场,为了恢复现场,需要在执行预测之前将现场进行保存。

分支预测的有效性取决于 :

- 预测的准确性 2. 预测正确 与 预测不正确两种情况下的分支开销

采用动态分支预测技术的目的

- 预测分支是否成功 2. 尽快找到分支目标地址(或指令)

需要解决的关键问题

- 如何记录分支的历史信息 2. 如何根据这些分支的历史信息来预测分支的去向

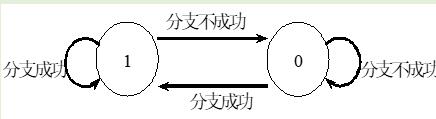

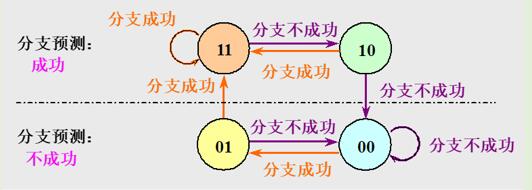

分支预测缓存器 BHT (Branch History Table)

只需要一位二进制位来记录分支最近一次的历史,结构和原理都最为简单

它还有一个进阶版,使用二位二进制数来进行预测的

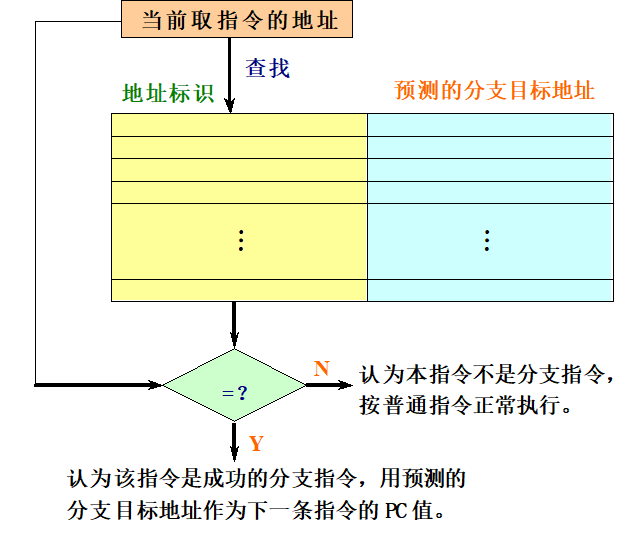

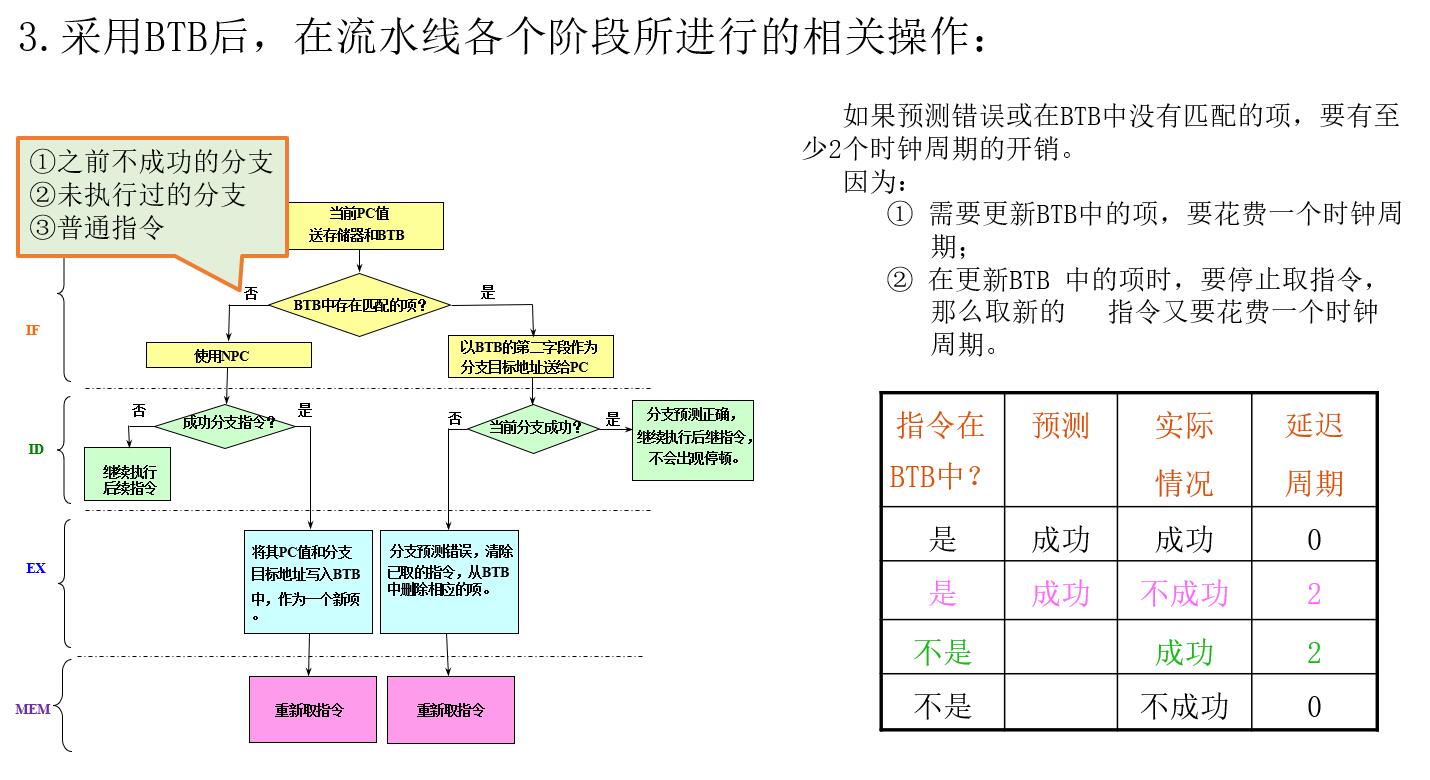

分支目标缓冲器 BTB (Branch Target Buffer)

- 结构 :

可以看作是一个硬件结构,左边是执行过的成功指令的地址(匹配标识) 、 右边是预测的分支目标地址。

- 执行 :

- BTB的另一种形式 : 在分支目标缓冲器中存放一条或者多条分支目标处的指令。

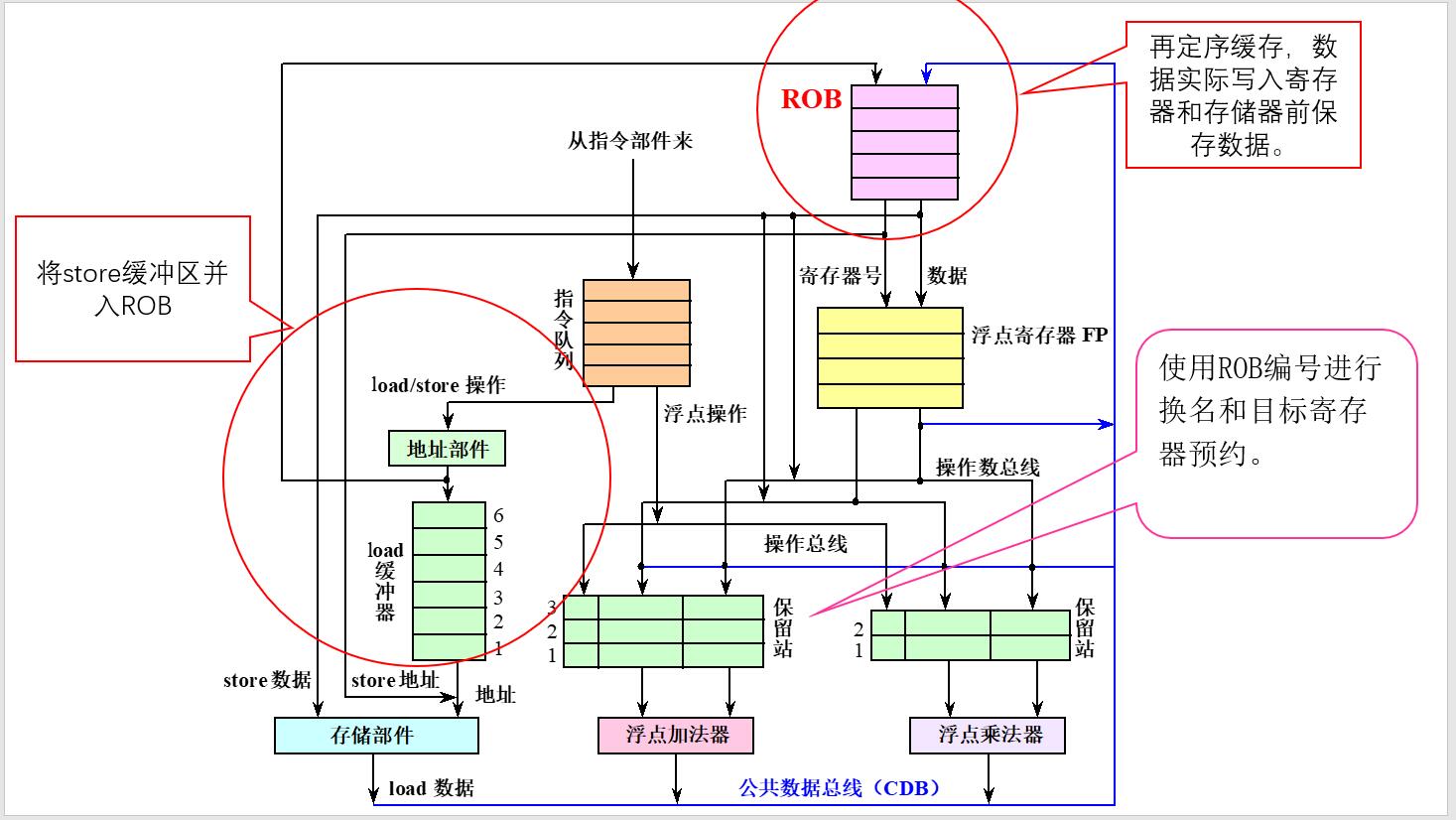

基于硬件的前瞻执行

前瞻执行的基本思想:

假设送过来的分支总是正确的,然后继续向下执行指令,执行出来的结构放入一个叫 ROB (ReOrder Buffer) 的缓冲器中。 等到相应的指令得到 “确认” 后,才将结果写入寄存器或者存储器。

前瞻执行的目的 :

利用 Tomasulo 算法消除了数据相关和名相关 , 再利用外加硬件的方式 , 避免了不可恢复的写操作。

前瞻执行的实质 :

实质是数据流执行(data flow execution):只要操作数有效,指令就执行。

前瞻执行所需的硬件结构 :

ROB 的内部结构:

指令类型 : 指出该指令是分支指令 、 store指令 、 或者寄存器操作指令 。

目标地址 : 给出指令执行结果应写入的目标寄存器号(如果是 load 和 ALU 指令)或 存储器单元的地址(store指令)。

数据值字段 : 用来保存指令前瞻执行的结果,直到指令得到确认。

就绪字段 : 指出指令是否已经完成执行并且数据已就绪。

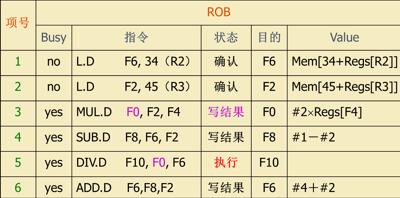

例题:

多指令流出技术

PPT和书都看不懂...

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具