8086CPU由哪两大部分组成?简述它们的主要功能。

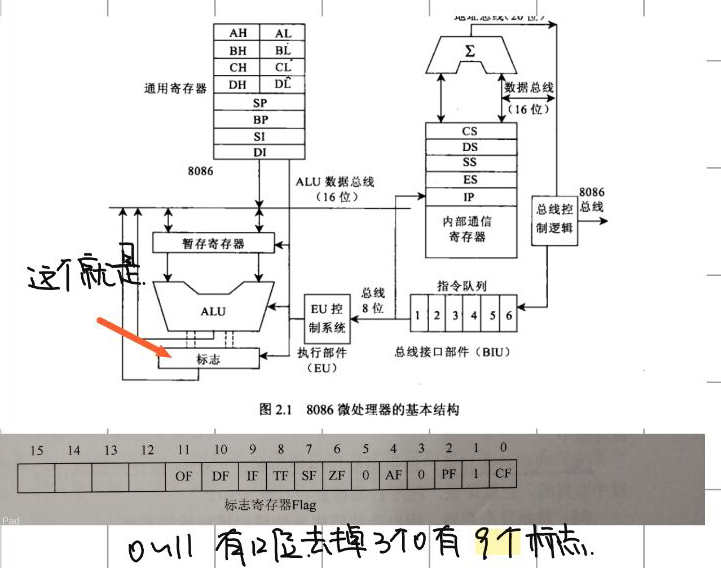

1.总线接口单元(bus interface unit BIU)

总线接口单元的组成:段寄存器(当前段的基址) + 指令指针(指令在当前代码段中的偏移地址) + 指令队列(存放预取的指令) + 地址加法器(形成物理地址) + 总线控制逻辑(内部总线与外部总线的接口)。

总线接口单元的功能:

<1> 取指令:从内存中取出指令送到指令队列中。

<2> 形成物理地址:BIU将16位段地址左移4位形成20位(相当于乘16)后,再与16位偏移地址通过地址加法器相加得到20位物理地址。

<3> 传送数据:EU在执行过程中需要内存或者I/O端口的数据时,BIU从外部取数据;或者将EU生成的数据输送到外部。或者协助EU访问外部器件。

2.执行单元(execution unit EU)

执行单元的组成:

通用寄存器(暂存计算的中间结果,可以减少微处理器访问外部存储器的频率,有利于提高信息处理速度)

标志寄存器(保存指令执行过程和执行结果特征,以及存储程序设置的一些控制位)

运算器和执行单元控制逻辑

执行单元的功能:主要功能就是完成全部指令的执行

<1> 指令译码 : 将BIU指令队列中的指令翻译为可以直接执行的微命令。

<2> 执行指令 :译码后的指令,通过EU控制逻辑向各个相关部件发出与指令一致的控制信号,完成指令的执行。

<3> 向BIU传送偏移地址信息 :计算偏移地址并传送给BIU。

<4> 管理通用寄存器和标志寄存器

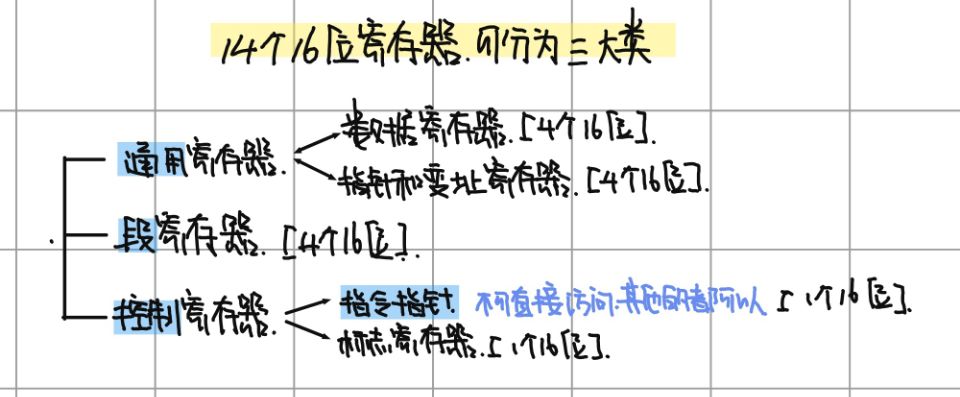

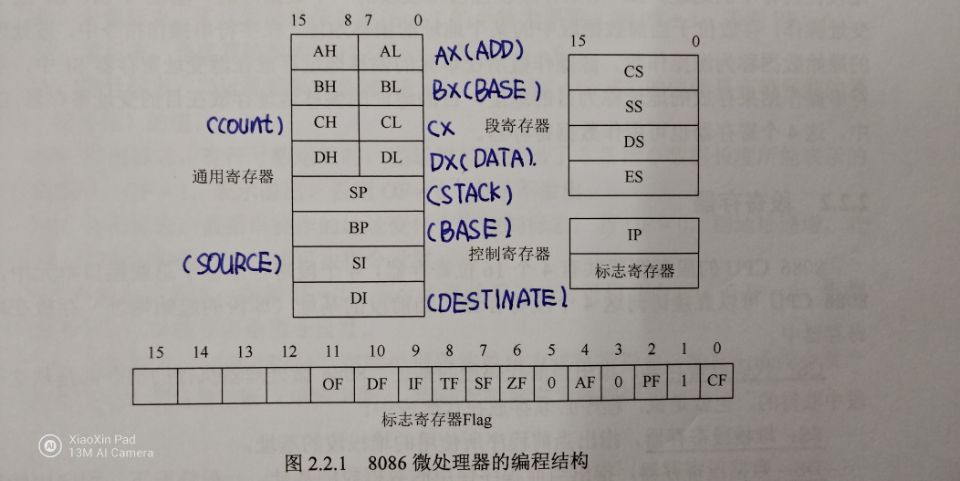

8086 CPU 有哪些类型的寄存器 ?

8086 CPU 段寄存器的作用是什么?

1.CS (code segment) : 代码段寄存器,指出当前代码段的基址,8086微处理器执行的指令都是从这个段中取得的,也就是说,程序必须存放在代码段中。

2.SS (stack segment) : 堆栈段寄存器,指出当前程序所使用的的堆栈段的基址。

3.DS (data segment) : 指出当前程序所使用的数据段的基址,一般情况下,程序中的变量存放在这个段中。

4.ES (...翻译不出来耶) : 指出当前程序使用的附加段,附加段用来存放数据或存放处理后的结果。

在通用寄存器中,八位寄存器与十六位寄存器有什么关系?

答:16位通用寄存器可以分为两个8位寄存器,即可将每个通用寄存器的高8位和低8位,作为独立的8位通用寄存器使用。

例如 : AX = 89ABH 中 AH(high) = 89H AL(low) = ABH.

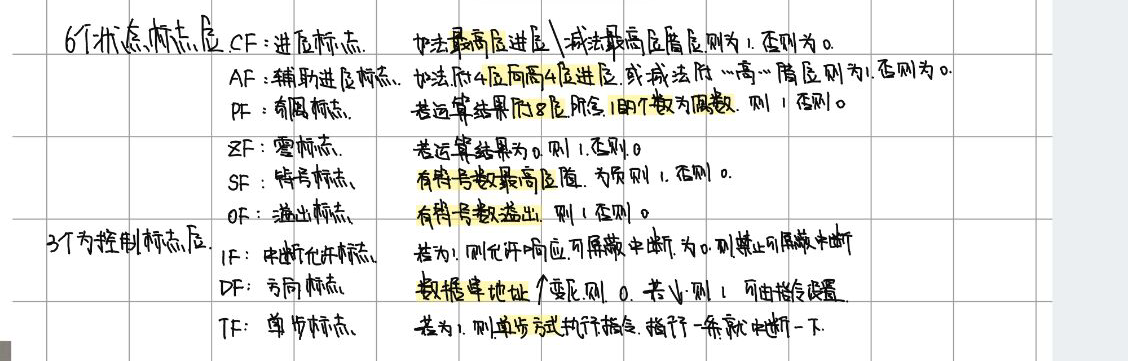

标志寄存器的各个位的作用都是什么?

指令指针的作用是什么?

还记得BIU的功能之 : 形成物理地址 嘛, IP的值就是传说中的偏移地址,BIU 就是将 CS 的值左移4位 然后通过地址加法器再加上 16位的IP值得到的实际物理地址。

举个栗子: CS 的值为 2000H IP的值为 0200H 问:下一条指令码存放的物理地址在哪里?

答 : CS左移四位 20000H + IP => 20200H

什么是物理地址、逻辑地址?逻辑地址2000:2345H 对应的物理地址是多少?

逻辑地址: 段地址和段内偏移量组成的二维地址,这种在编程结构中使用的地址称为逻辑地址,表示为 段地址 : 段内偏移地址 。

物理地址: 通过地址线给出的在1MB地址空间中每一个存储单元的唯一20位地址,称为物理地址,计算公式为 : (段寄存器) * 16 + 偏移量。

对应的物理地址为 : 22345H

在这里引申一下 : 1KB = 1024B (2^10B) 1MB = 1024KB(2^20B) 1GB = 1024MB(2^30B)

8086 CPU 最大模式最小模式有什么区别 ? 为什么设置不同的模式 ?

当组成小型的微型计算机系统时,8086微处理器处于一种最小结构下,称为最小模式。

当组成大型的微型计算机系统时,8086微处理器处于一种最大结构下,称为最大模式。

设计的目的是为了适用不同环境下使用微型计算机系统。(感觉这就像没答一样...)

最大最小模式如何切换? : 若将8086微处理器的引脚 MN/M-N-(M非N非) 接 +5V 则组成最小模式微型计算机系统,如果将该引脚接地则组成最大模式。

两种模式有什么相同的地方? : 8086微处理器外部采用40引脚双列直插式封装,在两种模式下有32个引脚的功能都是相同的。在这里提及 RESET 复位信号输入引脚 : 维持4个时钟周期起到复位效果,复位后标志寄存器、IP、DS、SS、ES、等寄存器清零,指令队列清空,CS设置为FFFFH,所以复位后(CPU启动时) 指向的地址为: FFFF0H。

两种模式有什么不同的地方? : 24 ~ 31共8个引脚的名称及功能在最小模式、最大模式下是不同的。这导致了最大最小状态的总线周期不同,主要差别在于控制信号线。最小模式的所有控制信号直接由微处理器对应的引脚输出,最大模式的控制信号由S0^- S1^- S2^- 输出的信号经总线控制器8288产生。

细节上:

24 25 两引脚在最小模式下都表示了各一种功能,而在最大模式下,两引脚构成QS1 QS0组合表示了指令队列的四种状态。

26 27 28三个引脚在最小模式下表示各一种功能,而在最大模式下,三个引脚构成 S0^- S1^- S2^- 组合表示了总线周期的7种状态(注意111无作用)

什么是时钟周期、总线周期、指令周期?它们有什么关系?

总线周期:总线周期是一个过程,是微处理器外部总线执行信息的输入\输出过程。总线读操作 包括取指令、读存储器、读I/O端口。写操作 包括写存储器、写I/O端口。

时钟周期:时钟脉冲信号循环一次的时间称为一个时钟周期。一个时钟周期是微处理器工作的最小时间单位。

指令周期:指令周期是执行一条指令所需的时间。

它们之间的关系: 指令周期中包含了总线周期,总线周期中包含了时钟周期。

8086一个总线周期包含了哪些时钟状态? 什么时候插入等待时钟Tw?

总线周期至少由4个时钟周期组成,每个时钟周期称为一个T状态,用T1\T2\T3\T4来表示。

T1 : 将存储器地址或I\O端口地址送上地址总线。(送上地址)

T2 : 进行读写准备,地址与数据、状态复用的信号在此期间切换,读写控制信号有效。 (切换状态,启动读写操作)

T3 : 微处理器检测存储器或I\O端口是否就绪,若存储器或I\O端口未就绪,则插入等待状态Tw。

T4 : 完成数据读写,结束总线操作,并使所有的引脚处于无效状态。微处理器的读或写是在 T4 周期进行的,这时数据线上的数据已经达到稳定状态。

在T3周期如果监测到 存储器或者I\O端口没有准备就绪,则插入等待周期 Tw 。

简述DRAM SRAM。

DRAM:主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit)是1还是0。因为晶体管会有漏电的现象,所以对DRAM要周期性的进行充电,这就是DRAM的刷新。DRAM用作内存比较多

SRAM:利用触发器存储信息,不需要考虑刷新的问题,但在电源掉电的时候,存储的信息也会丢失。SRAM用作cache比较多。SRAM更快。

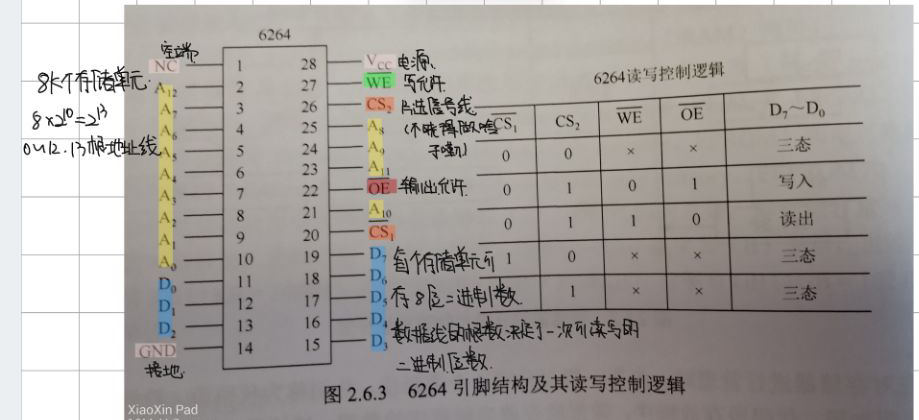

一个SRAM芯片一般有哪些类型的引脚? 一个8K*8位的存储器芯片有几条数据线?几条地址线?

数据线 8 条 (8K8 的那个8) 地址线13条(8K8 的 8K)

什么叫中断? 在微型计算机系统中为什么要使用中断?

在CPU正常执行当前程序的时,由某个实践引起CPU暂停正在执行的程序,转而去执行请求暂停的相应事件的服务程序,等服务程序处理完毕后又返回继续执行被暂时停止的程序,这个过程叫做中断。

中断是确保在运行过程中能够实时处理内外部设备的各种服务或处理异常和故障而采用的一种措施。

什么叫做中断源? 中断嵌套的含义是什么?

凡是能够提出中断请求的设备或异常故障,均成为中断源。

可以被分为:

1.I\O设备 : 如键盘、打印机等。

2.数据通道: 如磁带、磁盘等。

3.实时时钟 : 如定时器芯片8253等。(完全没概念...)

4.硬件故障 : 如电源掉电、RAM奇偶校验错误等。

5.软件故障 : 如执行除数为 0 的除法运算、地址越界、使用非法指令等。

6.软件设置 : 如在程序中用中断指令而产生的中断。

中断嵌套就是在中断处理的过程中又发生了中断。这部分在操作系统中讲解的更为详细一些。

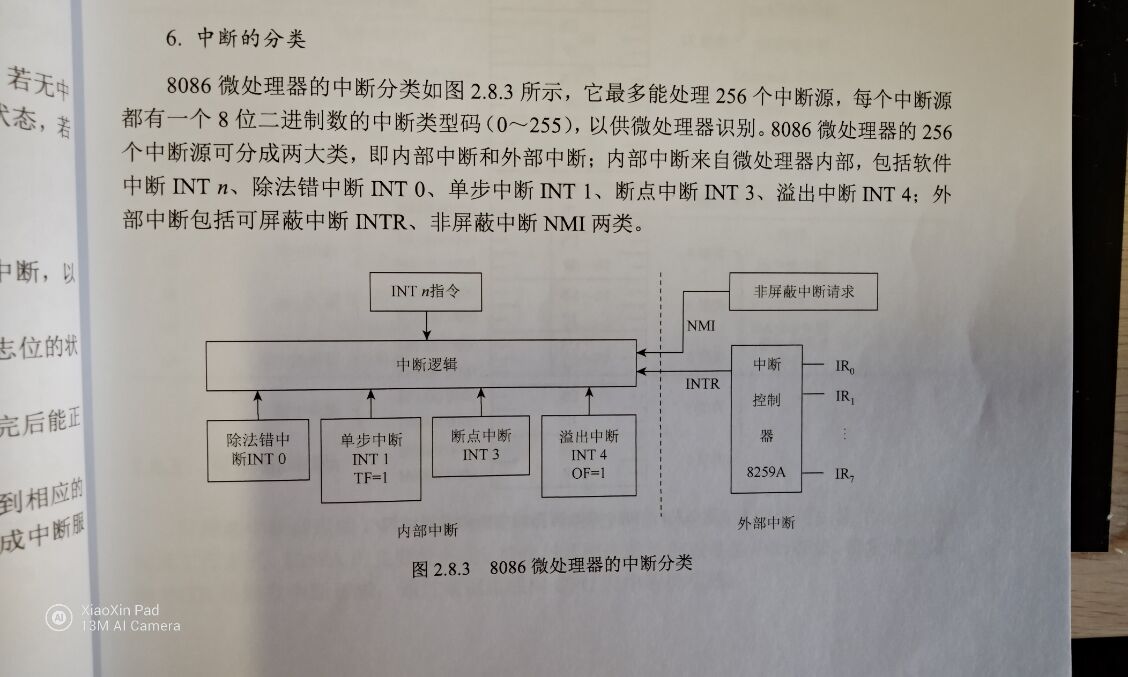

8086微处理器内部有哪几类中断? 简要说明各类的特点。

INT21 为80x86系统中 DOS系统功能调用

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具