单价1.2亿美元的EUV光刻机杂谈

单价1.2亿美元的EUV光刻机杂谈

光刻机为何被称为半导体设备上的明珠?它到底有多重要?

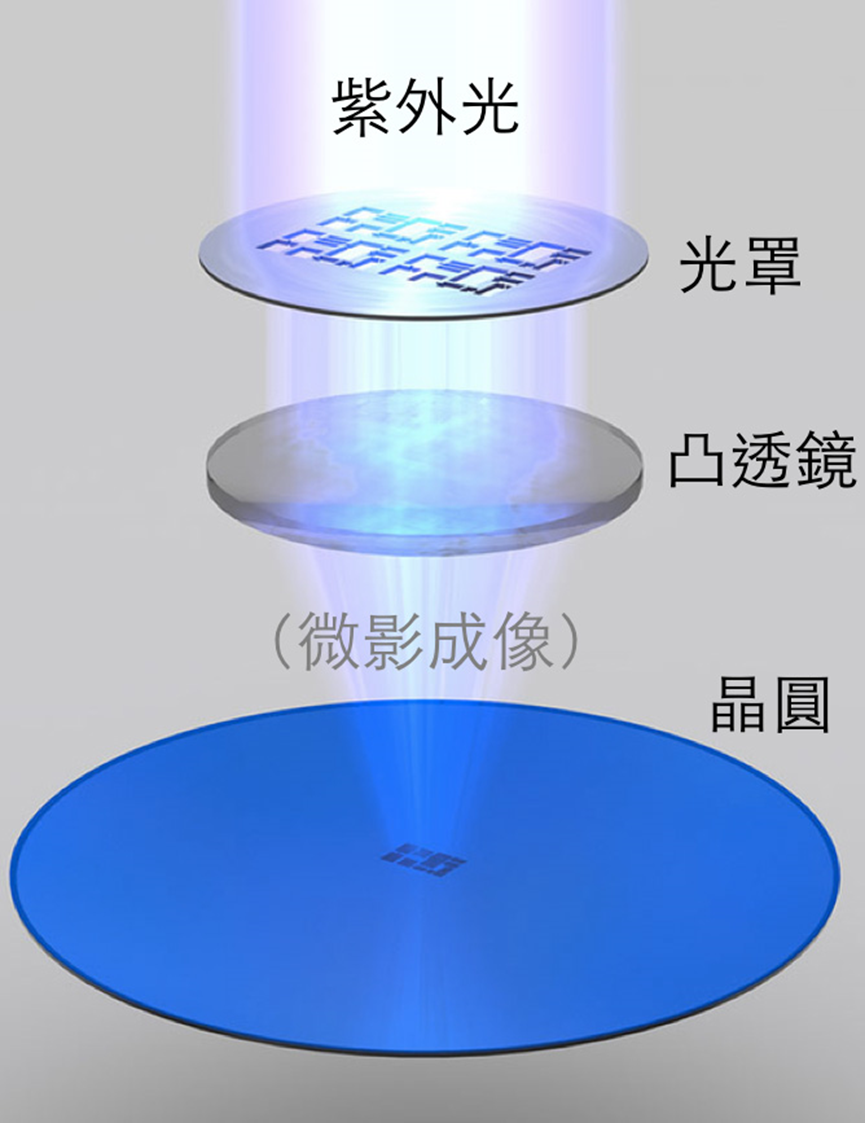

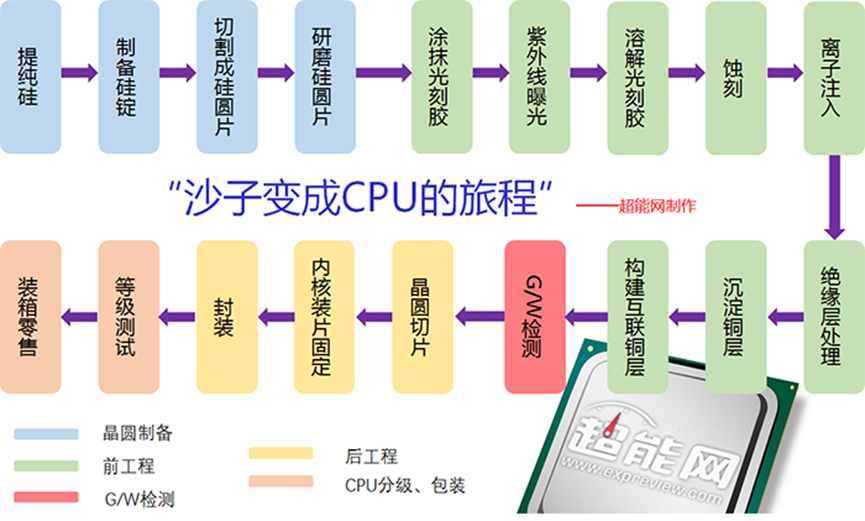

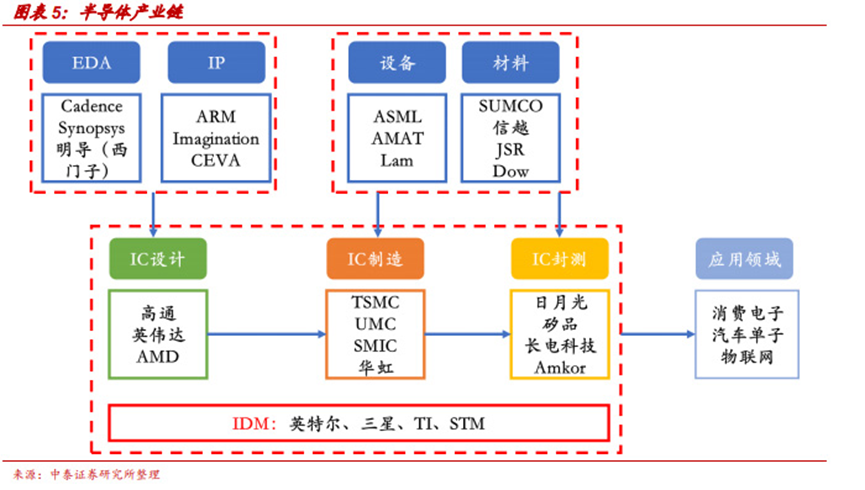

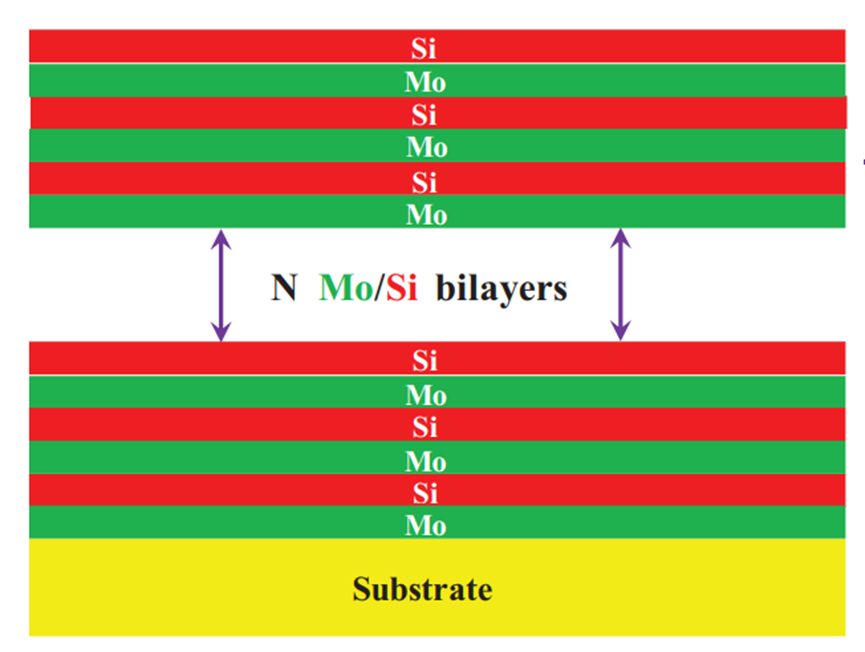

其实简单的流程图并不能反映出光刻在芯片制造过程中的重要性的,我们再来一个更简单、直接的有关芯片是如何研发、生产的,来看下面的示意图:

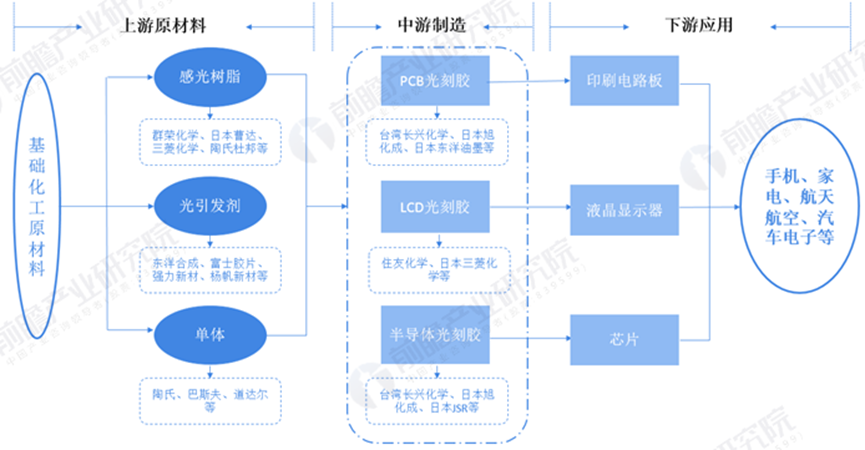

如果AMD/NVIDIA/高通要研发新一代CPU/GPU芯片,他们会使用到Cadence、Synospsys提供的EDA工具来辅助设计芯片,期间会用到各种IP核心,有的是来自ARM等第三方公司授权,也有的是公司自己研发的,设计完成之后他们会把芯片交给TSMC台积电、UMC联电、SMIC中芯国际等晶圆代工厂,这些代工厂的生产设备则来自ASML、AMAT应用材料、Lam等,8寸、12英寸硅片则是来自日本信越、Sumco胜高等公司公司,当然半导体制造中使用的材料还有很多,比如光刻胶、清洗剂等等,这些都可以归类于半导体材料行业中。

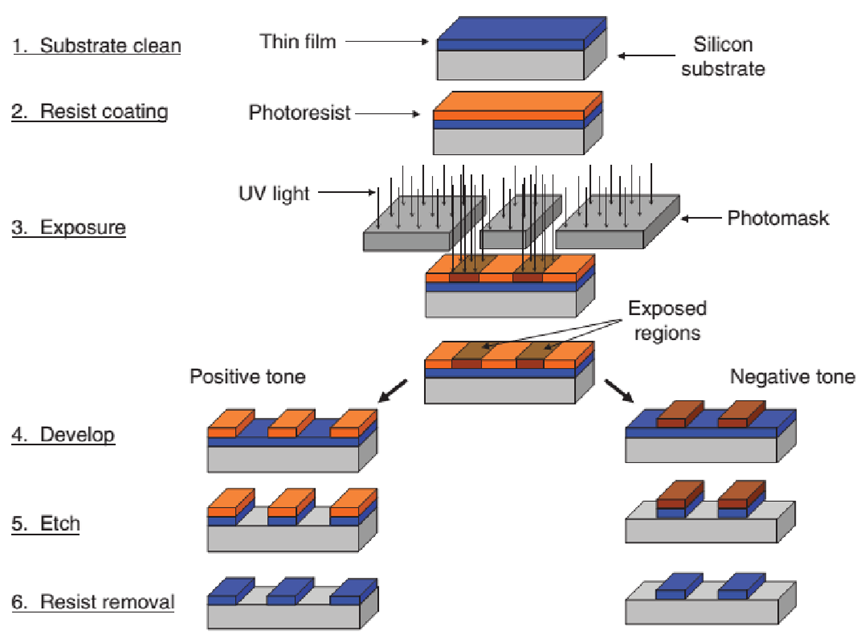

之前看到过一个好笑但也很有趣的悟空问答,有人问台积电能给AMD、NVIDIA、高通等公司代工处理器,难道不怕台积电偷偷学习他们的芯片然后自己生产吗?先不说这么做的法律风险,单从技术上来说代工厂复制芯片设计也没普通人想象的那么容易,因为IC设计公司并不是把芯片设计图给代工厂,代工厂是通过他们制作好的光罩或者说光掩膜版(mask)来生产芯片的。

如上图所示,台积电等晶圆代工厂做的工作实际上就是将IC设计公司做好的光罩通过光刻工艺复制一遍到买来的晶圆上,所以这也是他们为什么被称为晶圆代工厂的原因,做的就是帮助别人加工成芯片的工作。

这些话说来简单,但半导体芯片的实际制造过程非常复杂,如今的半导体芯片越来越强大,从28nm节点开始已经不是一次光刻就能实现的了,所以出现了多重曝光这样的技术,就是多次光刻处理,工艺越先进,芯片越复杂,所需的光刻次数就会越多,但需要多次消耗光刻胶及多次清洗,这样就会增加芯片生产的时间,提高了生产的复杂度,带来的后果就是芯片成本越来越高。

半导体芯片在整个生产过程中可能需要20-30次的光刻,耗时占到了生产环节的一半,成本能占到三分之一。

光刻不仅是影响代工厂的生产效率及成本,更主要的是光刻机的技术水平决定了芯片的制程工艺,这个才是最关键的,这也是光刻机最重要的功能。

·光刻机的原理及结构,堪称人类最精密的设备之一

光刻在芯片生产过程中如此重要,这也奠定了光刻机在半导体制造设备中的地位——没有先进的光刻机,其他过程都是舍本逐末。

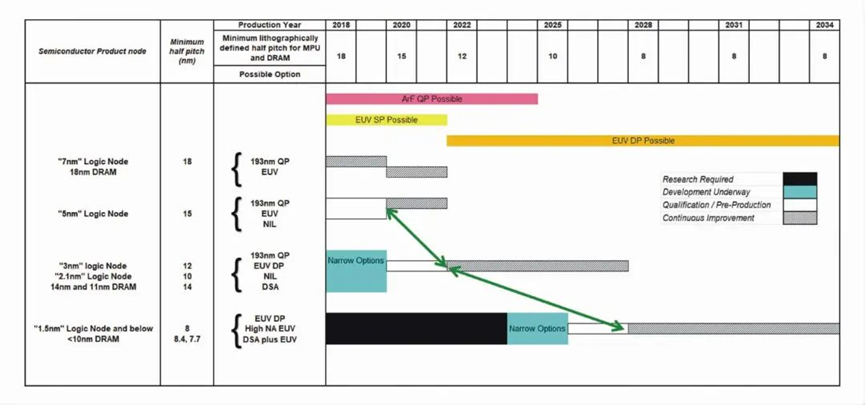

光刻机,按照不同的用途及光源有多种分类,现在大家说的主要是紫外光刻机,我们这里提到的主要有DUV深紫外光及EUV极紫外光,DUV光刻机是目前大量应用的光刻机,波长是193nm,光源是ArF(氟化氩)准分子激光器,从45nm到10nm工艺都可以使用这种光刻机,而EUV极紫外光波长是13.5nm,波长为何影响制程工艺后面再说,EUV光刻机主要用于7nm及以下节点。

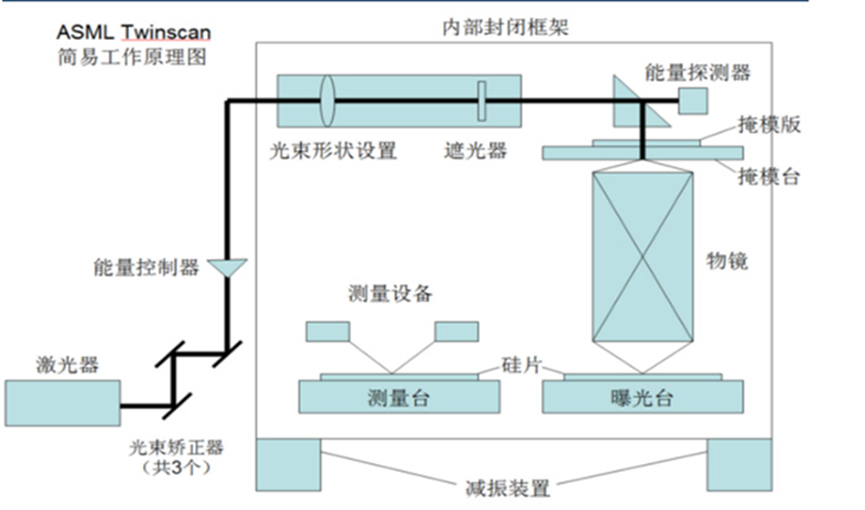

ASML光刻机工作原理图

以ASML典型的沉浸式步进扫描光刻机为例来看下光刻机是怎么工作的——首先是激光器发光,经过矫正、能量控制器、光束成型装置等之后进入光掩膜台,上面放的就设计公司做好的光掩膜,之后经过物镜投射到曝光台,这里放的就是8寸或者12英寸晶圆,上面涂抹了光刻胶,具有光敏感性,紫外光就会在晶圆上蚀刻出电路。

同样地,这个过程说起来很简单,实际上超级复杂,ASML的光刻机靠着沉浸式及双机台等技术打败了原本由日本佳能、尼康公司占据的光刻机市场,别的不说,光是双机台技术就不知道有多高的要求了,芯片生产是nm级别的精度,两个机台的精度控制需要极高的工艺水平,也许差了几nm就可能导致报废。

从这里也可以看出光刻机的结构也很复杂,其中最重要的部分主要有激光器、物镜及工作台,其中激光器负责光源产生,而光源对制程工艺是决定性影响的,而且激光的产生过程需要耗费能量,这也是光刻机需要消耗大量电力的根源。

还有物镜系统,光刻机里面的光学镜片不是一两片,而是一套多达数十个光学镜片组成的系统,视不同结构,镜片数量可能达到20片以上,而且面积很大,有如锅盖一般大小,不仅制作复杂,还需要精确的反射控制,玩单反的爱好者就知道镜头设计是多么复杂的了,更何况光刻机使用的是超大、超多组镜片了。

还有就是工作机台,双机台大幅提高了晶圆生产的效率,可以一边测量一边曝光,但是双机台的控制又提高了复杂度,对工艺要求非常高。

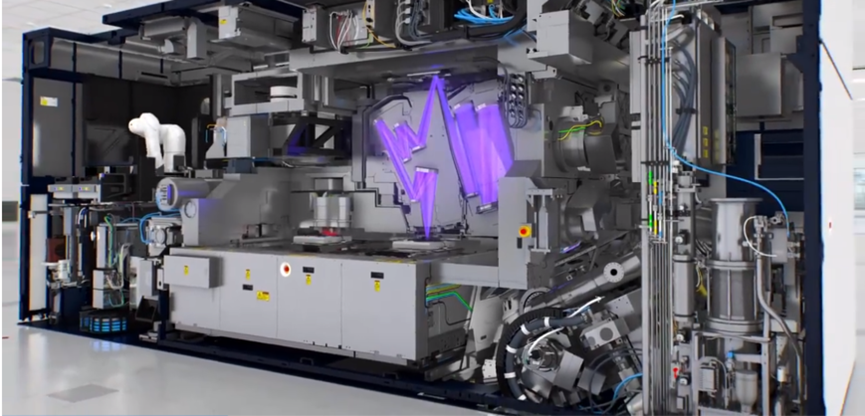

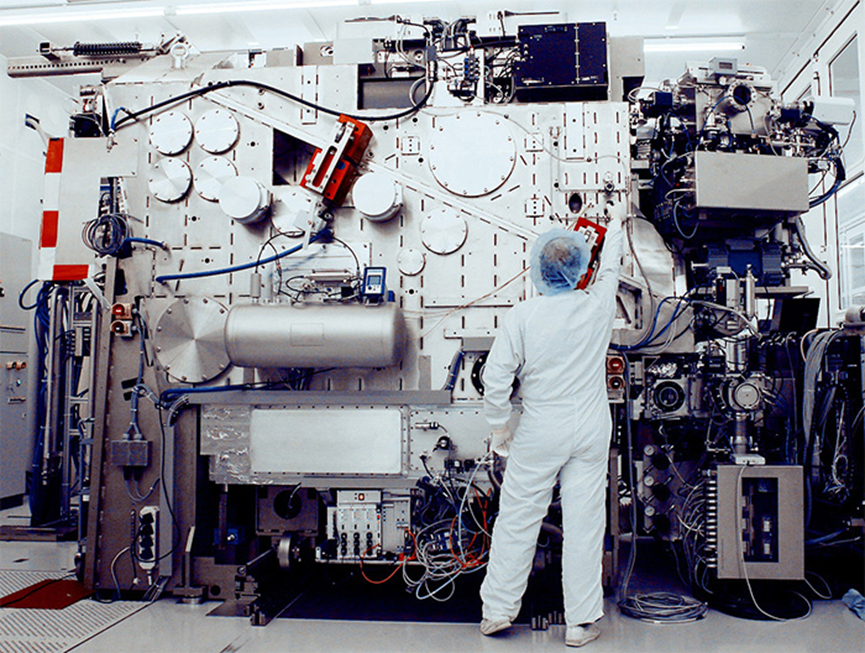

2006年全球首台EUV光刻机原型

如果只看光刻机的示意图,大家同样不会理解光刻机这货到底有多大,上图是ASML公布过的一张光刻机真身,大家可以看看光刻机到底有多大。

·为何需要EUV光刻机?先进工艺要么改光源要么改物镜

193nm的DUV光刻机已经使用多年,而且售价普遍在5000万美元,产能也高,为什么台积电、三星还要找ASML买单价不低于1.2亿美元的EUV光刻机,而且还要忍受产量低、能耗大等问题?他们显然不是吃饱了撑的,因为要想实现7nm及更先进的工艺,现有的DUV光刻机不够用了,需要13.5nm波长的EUV光刻机。

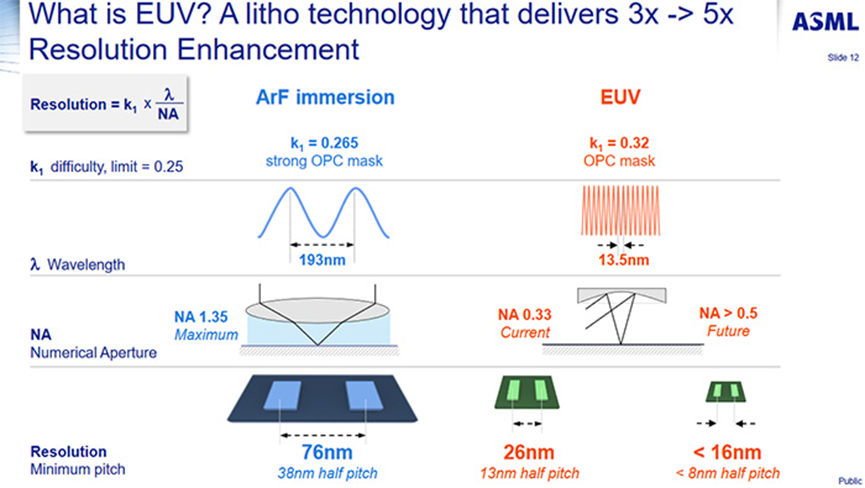

光刻机的分辨率取决于波长、NA孔径等

前面说了,光刻机决定了半导体工艺的制程工艺,光刻机的精度跟光源的波长、物镜的数值孔径是有关系的,有公式可以计算:

光刻机分辨率=k1*λ/NA

k1是常数,不同的光刻机k1不同,λ指的是光源波长,NA是物镜的数值孔径,所以光刻机的分辨率就取决于光源波长及物镜的数值孔径,波长越短越好,NA越大越好,这样光刻机分辨率就越高,制程工艺越先进。

在现有技术条件上,NA数值孔径并不容易提升,目前使用的镜片NA值是0.33,大家可能还记得之前有过一个新闻,就是ASML投入20亿美元入股卡尔·蔡司公司,双方将合作研发新的EUV光刻机,许多人不知道EUV光刻机跟蔡司有什么关系,现在应该明白了,ASML跟蔡司合作就是研发NA 0.5的光学镜片,这是EUV光刻机未来进一步提升分辨率的关键,不过高NA的EUV光刻机至少是2025-2030年的事了,还早着呢,光学镜片的进步比电子产品难多了。

NA数值一时间不能提升,所以光刻机就选择了改变光源,用13.5nm波长的EUV取代193nm的DUV光源,这样也能大幅提升光刻机的分辨率。

但是EUV光刻机的研制并不容易,不要以为只是换个光源,从DUV换到EUV对整个光刻机的结构都有重大影响,ASML公司研发EUV光刻机已经十几年甚至二十年的历史了,期间英特尔、台积电及三星都给ASML提供支持,先后投资数十亿美元给ASML(不过ASML业绩转好之后基本上都卖出了股票)输血,即便是这样,现在的EUV光刻机依然谈不上完全成熟。

首先EUV极其耗电,因为13.5nm的紫外光容易被吸收,导致转换效率非常低,据说只有0.02%,目前ASML的EUV光刻机输出功率是250W,工作一天就要耗电3万度——考虑到这个转换率是多年前的,多年来可能会有进步,但即便ASML大幅改进了EUV光源的效率,EUV光刻机超级耗电也是跑不了的,台积电在权衡未来的3nm晶圆厂选址时,首要考虑的就是台湾是否有稳定的电力供应。

此外,即便有如此高的电力消耗,EUV光刻机现在的生产效率还不够好,目前ASML的量产型EUV光刻机NXE:3400B的生产能力是125WPH,也就是一小时处理125片晶圆,而193nm光刻机NXT:1980Di的生产能力是275WPH,其他型号也能达到250WPH,产量能相差一倍。

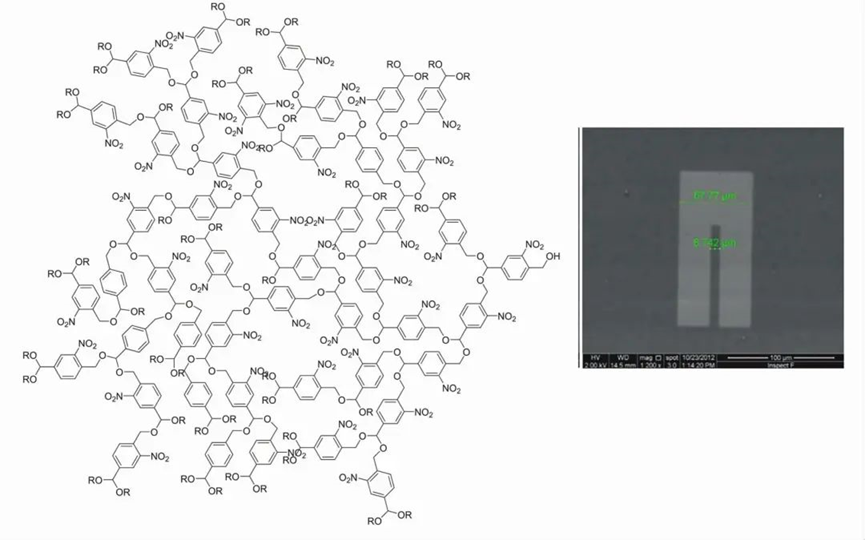

光刻胶又名“光致抗蚀剂”,是一种在紫外光等光照或辐射下,其溶解度会发生变化的薄膜材料。光刻胶的配方较为复杂,通常由增感剂、溶剂、感光树脂以及多种添加剂成分构成,是集成电路制造的关键基础材料之一,是光刻技术中涉及到最关键的功能性化学材料,广泛用于印刷电路和集成电路的制造以及半导体分立器件的微细加工等过程。光刻胶分为光聚合型、光分解型、光交联型、含硅光刻胶等种类。

另外,光刻胶与芯片息息相关。芯片制造涉及到国民经济、国家安全的方方面面,属于战略性行业。芯片主要通过光刻、刻蚀、封装等工序制作完成。芯片的成功诞生离不开设备、工艺和材料。其中光刻胶作为光刻工艺中的关键材料,直接决定加工的关键尺寸。

为匹配曝光光源和工艺的发展,达到更好的感度和分辨率,光刻胶成膜树脂从聚乙烯醇肉桂酸酯、环化橡胶、酚醛树脂、聚对羟基苯乙烯发展到聚丙烯酸酯、金属氧化物等。

光刻技术

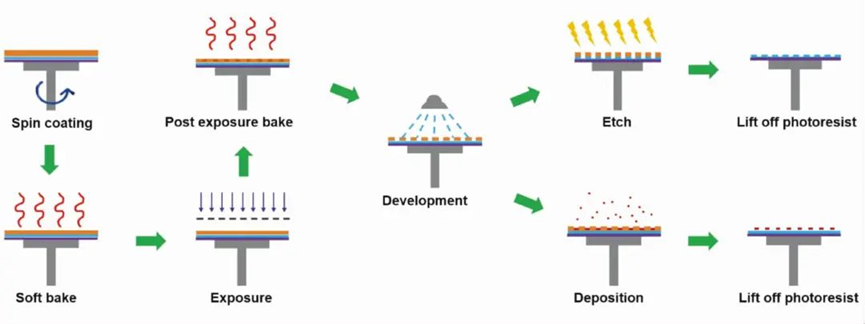

光刻技术在整个芯片制造中占据重要地位,是实现光刻胶和衬底图案化的关键工序:首先将光刻胶涂覆在衬底上,烘烤除去溶剂,然后通过掩膜版曝光或电子束直写,诱导曝光部分发生化学反应,最后用显影液洗去可溶部分,得到3D光刻胶图形。曝光部分溶解的,光刻胶图形与掩膜版图形一致,称为正性光刻胶;未曝光部分溶解的,光刻胶图形与掩膜版图形相反,称为负性光刻胶。

综合评述

先进光刻技术:导向自组装

导向自组装(Directed Self-Assembly,DSA)光刻技术是一种极具发展潜力的新型图形化工艺,已被国际器件与系统路线图(International Roadmap for Devices and Systems,IRDS)列为下一代光刻技术的主要候选方案。

光刻胶成膜剂:发展与未来

随着集成电路制程向着3 nm乃至1 nm推进,光刻胶作为集成电路制造中最为繁杂的光刻工艺所需的重要耗材,愈发显示其重要性及挑战性。

g-线/i-线光刻胶研究进展

针对g-线(436 nm)和i-线(365 nm)光刻胶进行了总结,按照其组成不同,将其分为酚醛树脂/重氮萘醌、化学放大胶和分子玻璃等类型,并分别进行介绍。

193 nm化学放大光刻胶研究进展

从光刻胶的成分出发介绍193 nm化学放大胶的研究进展,概述目前应用及研究中出现的代表性193 nm化学放大胶,总结其优缺点及未来可能的发展方向。

光敏聚酰亚胺光刻胶研究进展

近年来,光敏聚酰亚胺(PSPI)在先进封装、微机电系统和有机发光二极管(OLED)显示等新兴领域的需求牵引下得到了快速发展。在基础研究、应用研究以及产业化方面,PSPI的进展都引起了广泛关注。

高分辨率极紫外光刻胶的研究进展

自集成电路芯片诞生半个多世纪以来,芯片尺寸在不断减少,以极紫外光刻为代表的光刻技术也有了显著的发展。同时,实现更高精度的光刻图案需要更加先进的光刻胶材料。

面向极紫外:光刻胶的发展回顾与展望

随着半导体加工的光源不断进步,从g线、i线到KrF(248 nm)再到ArF(193 nm),与之匹配的光刻胶也在不断变化,以满足灵敏度、透光性以及抗刻蚀等需求。如今,极紫外(EUV)光刻已经成为公认的下一代光刻技术,然而与之对应的光刻胶还面临着不少挑战。

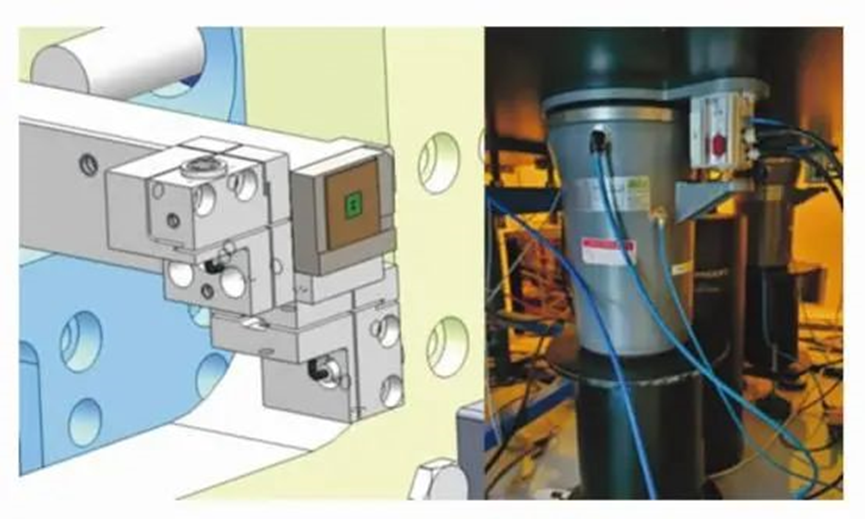

上海光源极紫外光刻胶检测平台

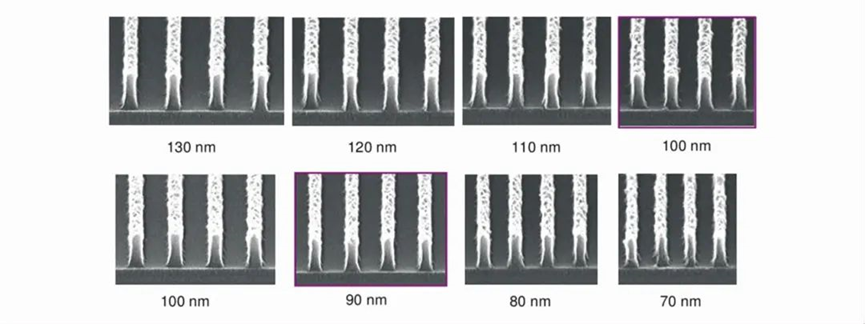

基于同步辐射的极紫外干涉光刻技术是目前最适合开展的一种用于极紫外光刻胶性能检测的方法。目前检测平台的曝光分辨率测试水平已能达到20 nm以下,基本满足极紫外光刻7 nm工艺节点的相应要求。

研究论文

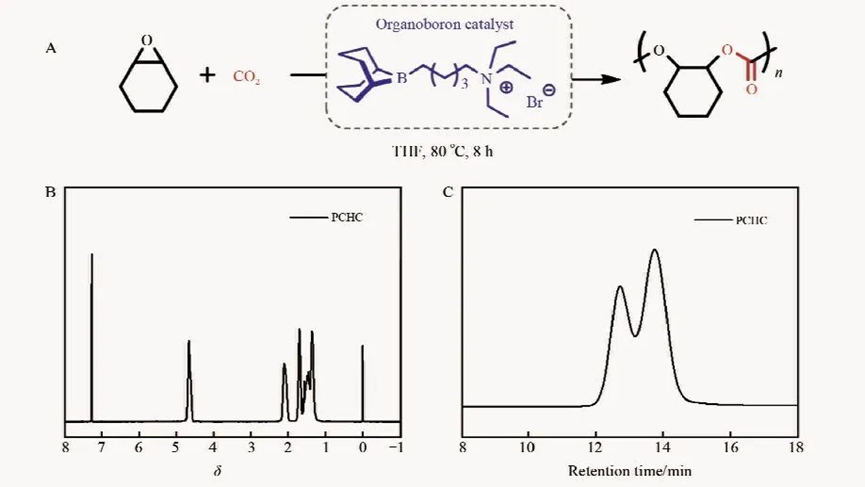

在前期开发出的二氧化碳基聚碳酸酯电子束光刻胶的基础上,进一步探究了正性聚碳酸环己撑酯(PCHC)胶的显影条件对电子束光刻性能的影响,在最优条件下,PCHC的灵敏度和对比度分别为208 μC/cm2和3.06,并实现了53 nm的分辨率,超过了当下广泛使用的PMMA-950k电子束光刻胶。

量子点光刻技术及其显示应用

量子点显示器件具有高光谱纯度、宽色域、高亮度等优势,被认为是显示行业未来的一个重要发展方向。发展量子点高精度光刻图案化技术对实现其在显示领域的应用具有重要的意义。

参考文献链接

https://mp.weixin.qq.com/s/pMH800RBFGk8q0KoseHYAQ

https://www.zhihu.com/question/339355431

https://www.expreview.com/62908.html

https://mp.weixin.qq.com/s/BFxufmHhGnDy3CIP9ACqCQ