TPU原理技术与xPU

TPU原理技术与xPU

CPU、GPU、DPU、TPU、NPU……

人工智能的发展离不开算力的支持,算力又是依附于各种硬件设备的,没有了算力设备的加持,就好比炼丹少了丹炉一样,可想而知,人工智能智能也就无用武之地了。以深度学习为主的人工智能方向的发展更是离不开强大的算力支持。随着深度学习的不断发展,各种各样的芯片也逐渐抛头露面,见过的,没见过的,听过的没有听过的都出现在眼前,一下有些眼花缭乱,一时竟不知选择哪个?当然前提是不差钱。

本学徒在打杂的时候就发现了众多的XPU,例如GPU, TPU, DPU, NPU, BPU……,各种不同的XPU还分不同等级的系列,价格也大不相同,要起钱来一个比一个凶猛。突然觉得这玩意根本就不是这些穷人玩的,虽然当时看的头晕目眩,内心波涛汹涌,但是仍然还要表现的波澜不惊才行,毕竟做为一名资深的炼丹学徒,还是要有最基本的心里素质的。

参考文献链接

https://baijiahao.baidu.com/s?id=1706639922409916892&wfr=spider&for=pc

https://www.nextplatform.com/2022/05/11/google-stands-up-exascale-tpuv4-pods-on-the-cloud/

https://mp.weixin.qq.com/s/sOPhPJhhniMTIlZX3HaSUA

https://mp.weixin.qq.com/s/e8zOrmiIidy8IoV1yMfdKg

https://mp.weixin.qq.com/s/VEDxfx3il-d_zMPCSntsVg

https://mp.weixin.qq.com/s/305V7bDTJb8jOInz9l_xTA

首先介绍一下这些常见的XPU的英文全称:

CPU全称:Central Processing Unit, 中央处理器;

GPU全称:Graphics Processing Unit, 图像处理器;

TPU全称:Tensor Processing Unit, 张量处理器;

DPU全称:Deep learning Processing Unit, 深度学习处理器;

NPU全称:Neural network Processing Unit, 神经网络处理器;

BPU全称:Brain Processing Unit, 大脑处理器。

下面就来科普一下这些所谓的“XPU”

CPU

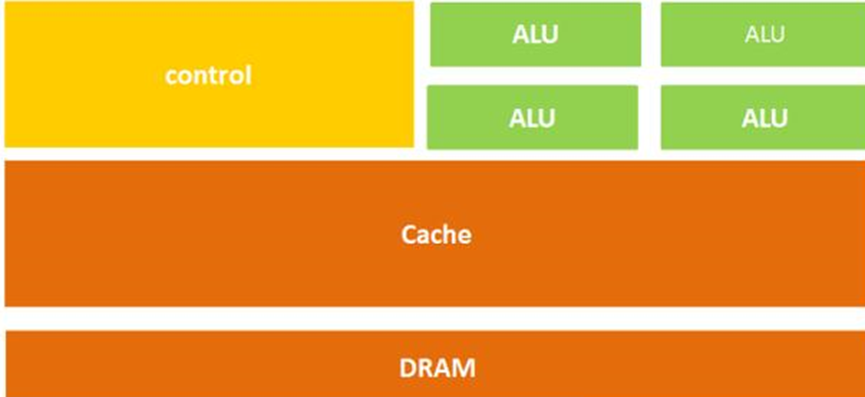

CPU( Central Processing Unit, 中央处理器)一般是指的设备的“大脑”,是整体布局、发布执行命令、控制行动的总指挥。

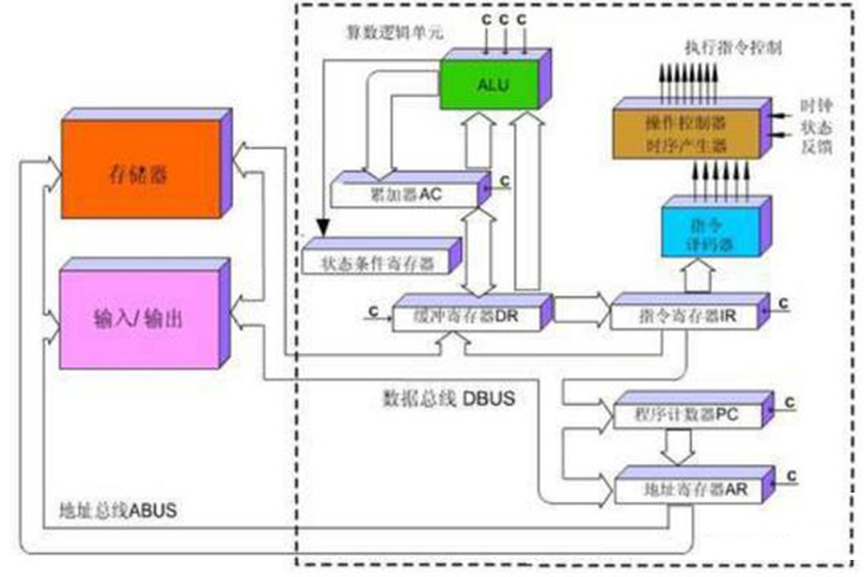

CPU主要包括运算器(ALU, Arithmetic and Logic Unit)和控制单元(CU, Control Unit),除此之外还包括若干寄存器、高速缓存器和之间通讯的数据、控制及状态的总线。CPU遵循的是冯诺依曼架构,即存储程序、顺序执行。一条指令在CPU中执行的过程是:读取到指令后,通过指令总线送到控制器中进行译码,并发出相应的操作控制信号。然后运算器按照操作指令对数据进行计算,并通过数据总线将得到的数据存入数据缓存器。因此,CPU需要大量的空间去放置存储单元和控制逻辑,相比之下计算能力只占据了很小的一部分,在大规模并行计算能力上极受限制,而更擅长于逻辑控制。

简单一点来说CPU主要就是三部分:计算单元、控制单元和存储单元,其架构如下图所示:

图:CPU微架构示意图

什么?这个架构太复杂,记不住?来,那么换一种表示方法:

图:CPU微架构示意图

大概就是这个意思。

从字面上也很容易理解,上面的计算单元主要执行计算机的算术运算、移位等操作以及地址运算和转换;而存储单元主要用于保存计算机在运算中产生的数据以及指令等;控制单元则对计算机发出的指令进行译码,并且还要发出为完成每条指令所要执行的各个操作的控制信号。

所以在CPU中执行一条指令的过程基本是这样的:指令被读取到后,通过控制器(黄色区域)进行译码被送到总线的指令,并会发出相应的操作控制信号;然后通过运算器(绿色区域)按照操作指令对输入的数据进行计算,并通过数据总线将得到的数据存入数据缓存器(大块橙色区域)。过程如下图所示:

图:CPU执行指令图

这个过程看起来是不是有点儿复杂?没关系,这张图可以不用记住,只需要知道,CPU遵循的是冯诺依曼架构,其核心就是:存储计算程序,按照顺序执行。

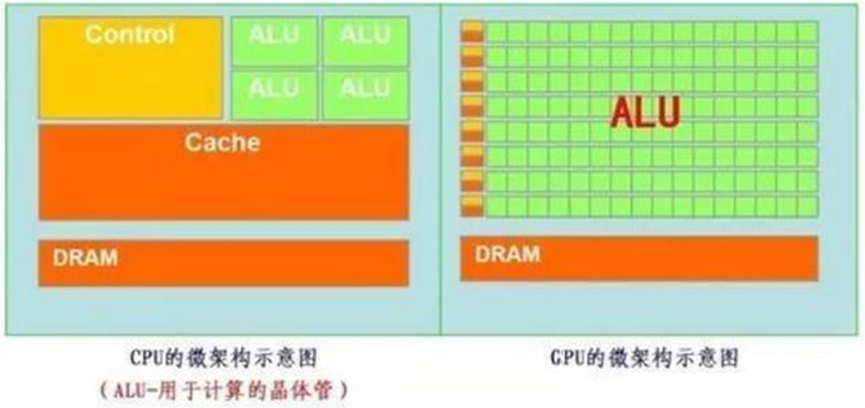

讲到这里,有没有看出问题,没错——在上面的这个结构图中,负责计算的绿色区域占的面积似乎太小了,而橙色区域的缓存Cache和黄色区域的控制单元占据了大量空间。

高中化学有句老生常谈的话叫:结构决定性质,放在这里也非常适用。

因为CPU的架构中需要大量的空间去放置存储单元(橙色部分)和控制单元(黄色部分),相比之下计算单元(绿色部分)只占据了很小的一部分,所以在大规模并行计算能力上极受限制,而更擅长于逻辑控制。

另外,因为遵循冯诺依曼架构(存储程序,顺序执行),CPU就像是个一板一眼的管家,人们吩咐事情总是一步一步来做,当做完一件事情才会去做另一件事情,从不会同时做几件事情。但是随着社会的发展,大数据和人工智能时代的来临,人们对更大规模与更快处理速度的需求急速增加,这位管家渐渐变得有些力不从心。

于是,大家就想,能不能把多个处理器都放在同一块芯片上,让一起来做事,相当于有了多位管家,这样效率不就提高了吗?

没错,就是这样的,使用的GPU便由此而诞生了。

GPU

在正式了解GPU之前,还是先来了解一下上文中提到的一个概念——并行计算。

并行计算(Parallel Computing)是指同时使用多种计算资源解决计算问题的过程,是提高计算机系统计算速度和数据处理能力的一种有效手段。基本思想是用多个处理器来共同求解同一个问题,即将被求解的问题分解成若干个部分,各部分均由一个独立的处理机来并行计算完成。

并行计算可分为时间上的并行和空间上的并行。

时间上的并行是指流水线技术,比如说工厂生产食品的时候分为四步:清洗-消毒-切割-包装。

如果不采用流水线,一个食品完成上述四个步骤后,下一个食品才进行处理,耗时且影响效率。但是采用流水线技术,就可以同时处理四个食品。这就是并行算法中的时间并行,在同一时间启动两个或两个以上的操作,大大提高计算性能。

图:流水线示意图

空间上的并行是指多个处理机并发的执行计算,即通过网络将两个以上的处理机连接起来,达到同时计算同一个任务的不同部分,或者单个处理机无法解决的大型问题。

比如小李准备在植树节种三棵树,如果小李1个人需要6个小时才能完成任务,植树节当天他叫来了好朋友小红、小王,三个人同时开始挖坑植树,2个小时后每个人都完成了一颗植树任务,这就是并行算法中的空间并行,将一个大任务分割成多个相同的子任务,来加快问题解决速度。

所以说,如果让CPU来执行这个种树任务的话,就会一棵一棵的种,花上6个小时的时间,但是让GPU来种树,就相当于好几个人同时在种。

为了解决CPU在大规模并行运算中遇到的困难, GPU应运而生,GPU全称为Graphics Processing Unit,中文为图形处理器,就如名字一样,图形处理器,GPU最初是用在个人电脑、工作站、游戏机和一些移动设备(如平板电脑、智能手机等)上运行绘图运算工作的微处理器。

GPU采用数量众多的计算单元和超长的流水线,善于处理图像领域的运算加速。但GPU无法单独工作,必须由CPU进行控制调用才能工作。CPU可单独作用,处理复杂的逻辑运算和不同的数据类型,但当需要大量的处理类型统一的数据时,则可调用GPU进行并行计算。近年来,人工智能的兴起主要依赖于大数据的发展、算法模型的完善和硬件计算能力的提升。其中硬件的发展则归功于GPU的出现。

为什么GPU特别擅长处理图像数据呢?这是因为图像上的每一个像素点都有被处理的需要,而且每个像素点处理的过程和方式都十分相似,也就成了GPU的天然温床。

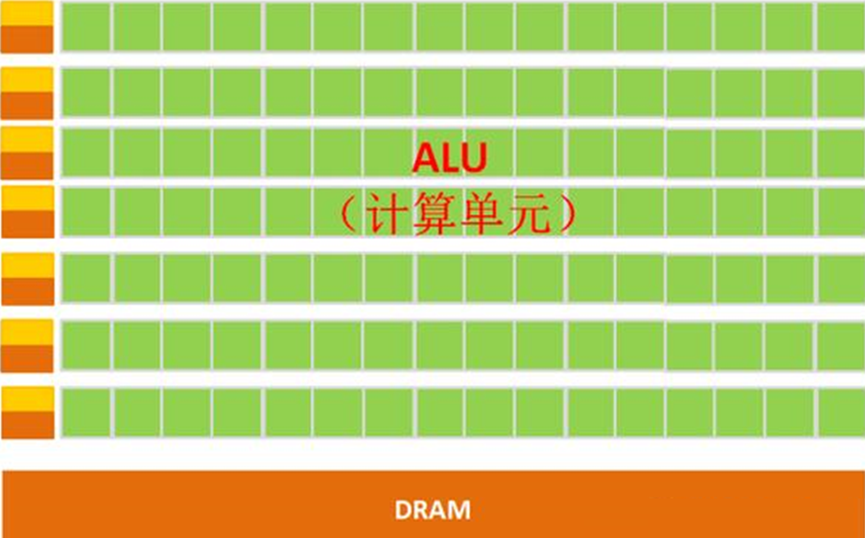

GPU简单架构如下图所示:

图:GPU微架构示意图

从架构图就能很明显的看出,GPU的构成相对简单,有数量众多的计算单元和超长的流水线,特别适合处理大量的类型统一的数据。

但GPU无法单独工作,必须由CPU进行控制调用才能工作。CPU可单独作用,处理复杂的逻辑运算和不同的数据类型,但当需要大量的处理类型统一的数据时,则可调用GPU进行并行计算。

注:GPU中有很多的运算器ALU和很少的缓存cache,缓存的目的不是保存后面需要访问的数据的,这点和CPU不同,而是为线程thread提高服务的。如果有很多线程需要访问同一个相同的数据,缓存会合并这些访问,然后再去访问dram。

再把CPU和GPU两者放在一张图上看下对比,就非常一目了然了。

GPU的工作大部分都计算量大,但没什么技术含量,而且要重复很多很多次。

借用知乎上某大神的说法,就像有个工作需要计算几亿次一百以内加减乘除一样,最好的办法就是雇上几十个小学生一起算,一人算一部分,反正这些计算也没什么技术含量,纯粹体力活而已;而CPU就像老教授,积分微分都会算,就是工资高,一个老教授能顶二十个小学生,要是富士康雇哪个?

GPU就是用很多简单的计算单元去完成大量的计算任务,纯粹的人海战术。这种策略基于一个前提,就是小学生A和小学生B的工作没有什么依赖性,是互相独立的。

但有一点需要强调,虽然GPU是为了图像处理而生的,但是通过前面的介绍可以发现,在结构上并没有专门为图像服务的部件,只是对CPU的结构进行了优化与调整,所以现在GPU不仅可以在图像处理领域大显身手,还被用来科学计算、密码破解、数值分析,海量数据处理(排序,Map-Reduce等),金融分析等需要大规模并行计算的领域。

所以GPU也可以认为是一种较通用的芯片。

TPU

按照上文所述,CPU和GPU都是较为通用的芯片,但是有句老话说得好:万能工具的效率永远比不上专用工具。

随着人们的计算需求越来越专业化,人们希望有芯片可以更加符合自己的专业需求,这时,便产生了ASIC(专用集成电路)的概念。

ASIC是指依产品需求不同而定制化的特殊规格集成电路,由特定使用者要求和特定电子系统的需要而设计、制造。当然这概念不用记,简单来说就是定制化芯片。

因为ASIC很“专一”,只做一件事,所以就会比CPU、GPU等能做很多件事的芯片在某件事上做的更好,实现更高的处理速度和更低的能耗。但相应的,ASIC的生产成本也非常高。

而TPU(Tensor Processing Unit, 张量处理器)就是谷歌专门为加速深层神经网络运算能力而研发的一款芯片,其实也是一款ASIC。

人工智能旨在为机器赋予人的智能,机器学习是实现人工智能的强有力方法。所谓机器学习,即研究如何让计算机自动学习的学科。TPU就是这样一款专用于机器学习的芯片,是Google于2016年5月提出的一个针对Tensorflow平台的可编程AI加速器,其内部的指令集在Tensorflow程序变化或者更新算法时也可以运行。TPU可以提供高吞吐量的低精度计算,用于模型的前向运算而不是模型训练,且能效(TOPS/w)更高。在Google内部,CPU,GPU,TPU均获得了一定的应用,相比GPU,TPU更加类似于DSP,尽管计算能力略有逊色,但是其功耗大大降低,而且计算速度非常的快。然而,TPU,GPU的应用都要受到CPU的控制。

图:谷歌第二代TPU

一般公司是很难承担为深度学习开发专门ASIC芯片的成本和风险的,但谷歌是谁,人家会差钱吗?

开个玩笑。更重要的原因是谷歌提供的很多服务,包括谷歌图像搜索、谷歌照片、谷歌云视觉API、谷歌翻译等产品和服务都需要用到深度神经网络。基于谷歌自身庞大的体量,开发一种专门的芯片开始具备规模化应用(大量分摊研发成本)的可能。

如此看来,TPU登上历史舞台也顺理成章了。

原来很多的机器学习以及图像处理算法大部分都跑在GPU与FPGA(半定制化芯片)上面,但这两种芯片都还是一种通用性芯片,所以在效能与功耗上还是不能更紧密的适配机器学习算法,而且Google一直坚信伟大的软件将在伟大的硬件的帮助下更加大放异彩,所以Google便想,可不可以做出一款专用机机器学习算法的专用芯片,TPU便诞生了。

据称,TPU与同期的CPU和GPU相比,可以提供15-30倍的性能提升,以及30-80倍的效率(性能/瓦特)提升。初代的TPU只能做推理,要依靠Google云来实时收集数据并产生结果,而训练过程还需要额外的资源;而第二代TPU既可以用于训练神经网络,又可以用于推理。

看到这里可能会问了,为什么TPU会在性能上这么牛逼呢?TPU是怎么做到如此之快呢?

(1)深度学习的定制化研发:TPU 是谷歌专门为加速深层神经网络运算能力而研发的一款芯片,其实也是一款 ASIC(专用集成电路)。

(2)大规模片上内存:TPU 在芯片上使用了高达 24MB 的局部内存,6MB 的累加器内存以及用于与主控处理器进行对接的内存。

(3)低精度 (8-bit) 计算:TPU 的高性能还来源于对于低运算精度的容忍,TPU 采用了 8-bit 的低精度运算,也就是说每一步操作 TPU 将会需要更少的晶体管。

嗯,谷歌写了好几篇论文和博文来说明这一原因,所以仅在这里抛砖引玉一下。

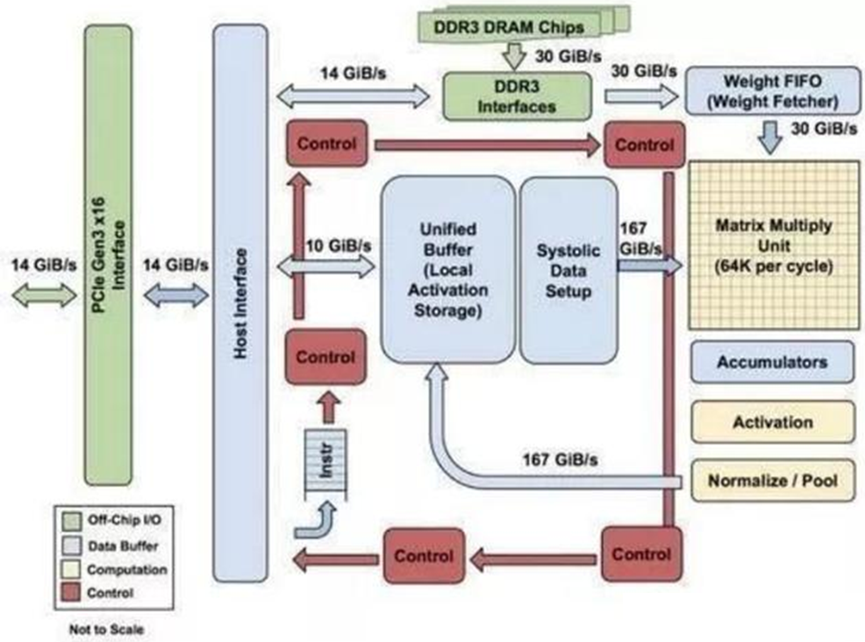

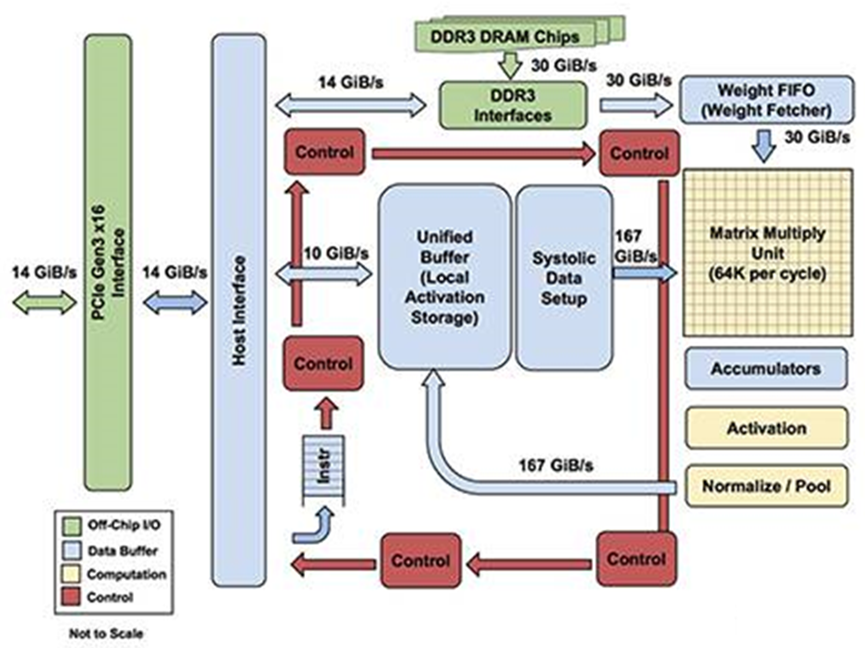

图:TPU 各模块的框图

图:TPU芯片布局图

如上图所示,TPU在芯片上使用了高达24MB的局部内存,6MB的累加器内存以及用于与主控处理器进行对接的内存,总共占芯片面积的37%(图中蓝色部分)。

这表示谷歌充分意识到了片外内存访问是GPU能效比低的罪魁祸首,因此不惜成本的在芯片上放了巨大的内存。相比之下,英伟达同时期的K80只有8MB的片上内存,因此需要不断地去访问片外DRAM。

另外,TPU的高性能还来源于对于低运算精度的容忍。研究结果表明,低精度运算带来的算法准确率损失很小,但是在硬件实现上却可以带来巨大的便利,包括功耗更低、速度更快、占芯片面积更小的运算单元、更小的内存带宽需求等...TPU采用了8比特的低精度运算。

其它更多的信息可以去翻翻谷歌的论文。

到目前为止,TPU其实已经干了很多事情了,例如机器学习人工智能系统RankBrain,是用来帮助Google处理搜索结果并为用户提供更加相关搜索结果的;还有街景Street View,用来提高地图与导航的准确性的;当然还有下围棋的计算机程序AlphaGo!

NPU

讲到这里,相信大家对这些所谓的“XPU”的套路已经有了一定了解,接着来。

所谓NPU(Neural network Processing Unit), 即神经网络处理器。神经网络处理器(NPU)采用“数据驱动并行计算”的架构,特别擅长处理视频、图像类的海量多媒体数据。NPU处理器专门为物联网人工智能而设计,用于加速神经网络的运算,解决传统芯片在神经网络运算时效率低下的问题。

在GX8010中,CPU和MCU各有一个NPU,MCU中的NPU相对较小,习惯上称为SNPU。NPU处理器包括了乘加、激活函数、二维数据运算、解压缩等模块。乘加模块用于计算矩阵乘加、卷积、点乘等功能,NPU内部有64个MAC,SNPU有32个。

激活函数模块采用最高12阶参数拟合的方式实现神经网络中的激活函数,NPU内部有6个MAC,SNPU有3个。二维数据运算模块用于实现对一个平面的运算,如降采样、平面数据拷贝等,NPU内部有1个MAC,SNPU有1个。解压缩模块用于对权重数据的解压。为了解决物联网设备中内存带宽小的特点,在NPU编译器中会对神经网络中的权重进行压缩,在几乎不影响精度的情况下,可以实现6-10倍的压缩效果。

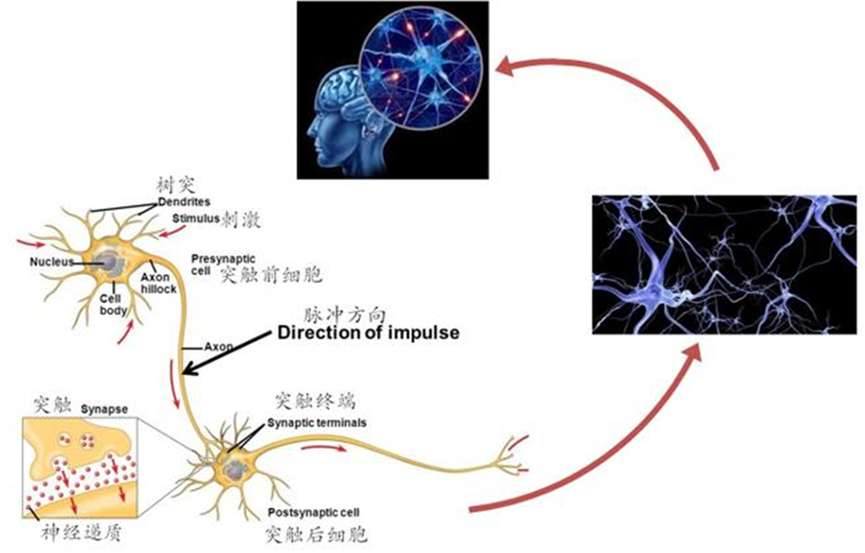

既然叫神经网络处理器,顾名思义,这家伙是想用电路模拟人类的神经元和突触结构啊!

怎么模仿?那就得先来看看人类的神经结构——生物的神经网络由若干人工神经元结点互联而成,神经元之间通过突触两两连接,突触记录了神经元之间的联系。

高中生物还记得吗?

如果想用电路模仿人类的神经元,就得把每个神经元抽象为一个激励函数,该函数的输入由与其相连的神经元的输出以及连接神经元的突触共同决定。

为了表达特定的知识,使用者通常需要(通过某些特定的算法)调整人工神经网络中突触的取值、网络的拓扑结构等。该过程称为“学习”。

在学习之后,人工神经网络可通过习得的知识来解决特定的问题。

这时不知道大家有没有发现问题——原来,由于深度学习的基本操作是神经元和突触的处理,而传统的处理器指令集(包括x86和ARM等)是为了进行通用计算发展起来的,其基本操作为算术操作(加减乘除)和逻辑操作(与或非),往往需要数百甚至上千条指令才能完成一个神经元的处理,深度学习的处理效率不高。

这时就必须另辟蹊径——突破经典的冯·诺伊曼结构!

神经网络中存储和处理是一体化的,都是通过突触权重来体现。 而冯·诺伊曼结构中,存储和处理是分离的,分别由存储器和运算器来实现,二者之间存在巨大的差异。当用现有的基于冯·诺伊曼结构的经典计算机(如X86处理器和英伟达GPU)来跑神经网络应用时,就不可避免地受到存储和处理分离式结构的制约,因而影响效率。这也就是专门针对人工智能的专业芯片能够对传统芯片有一定先天优势的原因之一。

2016年6 月 20 日,中星微数字多媒体芯片技术 国家重点实验室在北京宣布,已研发成功了中国首款嵌入式神经网络处理器(NPU)芯片,成为全球首颗具备深度学习人工智能的嵌入式视频采集压缩编码系统级芯片,并取名“星光智能一号”。

NPU的典型代表还有国内的寒武纪芯片和IBM的TrueNorth。以中国的寒武纪为例,DianNaoYu指令直接面对大规模神经元和突触的处理,一条指令即可完成一组神经元的处理,并对神经元和突触数据在芯片上的传输提供了一系列专门的支持。

用数字来说话,CPU、GPU与NPU相比,会有百倍以上的性能或能耗比差距——以寒武纪团队过去和Inria联合发表的DianNao论文为例——DianNao为单核处理器,主频为0.98GHz,峰值性能达每秒4520亿次神经网络基本运算,65nm工艺下功耗为0.485W,面积3.02平方毫米mm。

华为mate10中所用的麒麟970芯片,就集成了寒武纪的NPU,NPU是麒麟970处理器的最大特征,专业来说,相当于是设立了一个专门的AI硬件处理单元—NPU,主要用来处理海量的AI数据。NPU是麒麟970芯片中,搭载的一颗用于神经元计算的独立处理单元,英文名 Neural Network Processing Unit,简称 NPU,中文含义为“神经元网络”,功能主要是「A new brain in your mobile」,简单地说,借助这个玩意儿,手机或许会变得更聪明一些。

简单地说,由于神经元分布是网状结构,因此能够实现发散式的信息处理及存储,使得处理与存储的效率大大提高,并有助于机器学习(啊,手机都开始认真学习了),没错和平时所说的「发散性思维」有些像。

由于神经网络算法及机器学习需要涉及海量的信息处理,而当下的 CPU / GPU 都无法达到如此高效的处理能力,所以需要有一个独立的处理芯片来做这个事,麒麟 970 芯片中的这个 NPU 便是这样的一个角色。

华为mate10的手机有了NPU,才可以实现所谓的照片优化功能,以及保证手机用了很长时间后还能不卡(当然也得真正用了才能知道有没有宣传的这么好)。

另外,以往手机无法知道一张图片里,除了脸之外,还有些什么,而如今借助 NPU 这类芯片,手机能够知道在哪里拍了什么照片,照片中有什么著名的建筑或者哪条街,同时猫啊狗啊也能帮分析出来,甚至为设一个照片专辑。

当然,经过长期与大量的学习后,手机便能在拍摄的过程中实时分析拍摄场景,并分别针对不同的场景进行相机参数的设置,从而实现「随手拍出好照片」

还可以通过了解用户经常会在哪些地方做什么事情,来分析用户的使用习惯,目的是在经过一段时间的学习之后,自动为用户在某些场景实现某些功能。此外,还能分析出机主的用户画像,并针对性地做系统资源优化(如电量、性能、运存等),让手机真正达到越用越贴心。

PS,中星微电子的“星光智能一号”虽说对外号称是NPU,但其实只是DSP,仅支持网络正向运算,无法支持神经网络训练。

在了解了以上这些知识的基础上,再来理解BPU和DPU就更容易了。

BPU

Brain Processing Unit (大脑处理器)。地平线机器人(Horizon Robotics)以 BPU 来命名自家的 AI 芯片。地平线是一家成立于 2015 年的 start-up,总部在北京,目标是“嵌入式人工智能全球领导者”。地平线的芯片未来会直接应用于自己的主要产品中,包括:智能驾驶、智能生活和智能城市。地平线机器人的公司名容易让人误解,以为是做“机器人”的,其实不然。地平线做的不是“机器”的部分,是在做“人”的部分,是在做人工智能的“大脑”,所以,其处理器命名为 BPU。相比于国内外其他 AI 芯片 start-up 公司,第一代是高斯架构,第二代是伯努利架构,第三代是贝叶斯架构。目前地平线已经设计出了第一代高斯架构,并与英特尔在2017年CES展会上联合推出了ADAS系统(高级驾驶辅助系统)。BPU主要是用来支撑深度神经网络,比在CPU上用软件实现更为高效。然而,BPU一旦生产,不可再编程,且必须在CPU控制下使用。BPU 已经被地平线申请了注册商标,其他公司就别打 BPU 的主意了。

Biological Processing Unit。一个口号“21 世纪是生物学的世纪”忽悠了无数的有志青年跳入了生物领域的大坑。其实,这句话需要这么理解,生物学的进展会推动 21 世纪其他学科的发展。比如,对人脑神经系统的研究成果就会推动 AI 领域的发展,SNN 结构就是对人脑神经元的模拟。不管怎么说,随着时间的推移,坑总会被填平的。不知道生物处理器在什么时间会有质的发展。

Bio-Recognition Processing Unit。生物特征识别现在已经不是纸上谈兵的事情了。指纹识别已经是近来智能手机的标配,电影里的黑科技虹膜识别也上了手机,声纹识别可以支付了 ... 不过,除了指纹识别有专门的 ASIC 芯片外,其他生物识别还基本都是 sensor 加通用 cpu/dsp 的方案。不管怎样,这些芯片都没占用 BPU 或 BRPU 这个宝贵位置。

D 是 Deep Learning 的首字母,以 Deep Learning 开头来命名 AI 芯片是一种很自然的思路。

DPU

Deep-Learning Processing Unit(深度学习处理器)。DPU 并不是哪家公司的专属术语。在学术圈,Deep Learning Processing Unit(或 processor)被经常提及。例如 ISSCC 2017 新增的一个 session 的主题就是 Deep Learning Processor。以 DPU 为目标的公司如下。

Deephi Tech(深鉴) 深鉴是一家位于北京的 start-up,初创团队有很深的清华背景。深鉴将其开发的基于 FPGA 的神经网络处理器称为 DPU。到目前为止,深鉴公开发布了两款 DPU:亚里士多德架构和笛卡尔架构,分别针对 CNN 以及 DNN/RNN。虽然深鉴号称是做基于 FPGA 的处理器开发,但是从公开渠道可以看到的招聘信息以及非公开的业内交流来看,其做芯片已成事实。

TensTorrent 一家位于 Toronto 的 start-up,研发专为深度学习和智能硬件而设计的高性能处理器,技术人员来自 NVDIA 和 AMD。

Deep Learning Unit。深度学习单元。Fujitsu(富士通)最近高调宣布了自家的 AI 芯片,命名为 DLU。名字虽然没什么创意,但是可以看到 DLU 已经被富士通标了“TM”,虽然 TM 也没啥用。在其公布的信息里可以看到,DLU 的 ISA 是重新设计的,DLU 的架构中包含众多小的 DPU(Deep Learning Processing Unit)和几个大的 master core(控制多个 DPU 和 memory 访问)。每个 DPU 中又包含了 16 个 DPE(Deep-Learning Processing Element),共 128 个执行单元来执行 SIMD 指令。富士通预计 2018 财年内推出 DLU。

Deep Learning Accelerator。深度学习加速器。NVIDA 宣布将这个 DLA 开源,给业界带来了不小的波澜。大家都在猜测开源 DLA 会给其他 AI 公司带来什么。参考这篇吧"从 Nvidia 开源深度学习加速器说起"

Dataflow Processing Unit。数据流处理器。创立于 2010 年的 wave computing 公司将其开发的深度学习加速处理器称为 Dataflow Processing Unit(DPU),应用于数据中心。Wave 的 DPU 内集成 1024 个 cluster。每个 Cluster 对应一个独立的全定制版图,每个 Cluster 内包含 8 个算术单元和 16 个 PE。其中,PE 用异步逻辑设计实现,没有时钟信号,由数据流驱动,这就是其称为 Dataflow Processor 的缘由。使用 TSMC 16nm FinFET 工艺,DPU die 面积大概 400mm^2,内部单口 sram 至少 24MB,功耗约为 200W,等效频率可达 10GHz,性能可达 181TOPS。前面写过一篇他家 DPU 的分析,见传输门 AI 芯片|浅析 Yann LeCun 提到的两款 Dataflow Chip。

Digital Signal Processor。数字信号处理器。芯片行业的人对 DSP 都不陌生,设计 DSP 的公司也很多,TI,Qualcomm,CEVA,Tensilica,ADI,Freescale 等等,都是大公司,此处不多做介绍。相比于 CPU,DSP 通过增加指令并行度来提高数字计算的性能,如 SIMD、VLIW、SuperScalar 等技术。面对 AI 领域新的计算方式(例如 CNN、DNN 等)的挑战,DSP 公司也在马不停蹄地改造自己的 DSP,推出支持神经网络计算的芯片系列。在后面 VPU 的部分,会介绍一下针对 Vision 应用的 DSP。和 CPU 一样,DSP 的技术很长时间以来都掌握在外国公司手里,国内也不乏兢兢业业在这方向努力的科研院所,如清华大学微电子所的 Lily DSP(VLIW 架构,有独立的编译器),以及国防科大的 YHFT-QDSP 和矩阵 2000。但是,也有臭名昭著的“汉芯”。

国际上,Wave Computing最早提出DPU。在国内,DPU最早是由深鉴科技提出,是基于Xilinx可重构特性的FPGA芯片,设计专用深度学习处理单元,且可以抽象出定制化的指令集和编译器,从而实现快速的开发与产品迭代。

以为到这里就完了吗?

不,据说每过18天,集成电路领域就会多出一个XPU,直到26个字母被用完。

这被戏称为AI时代的XPU版摩尔定律。

据不完全统计,已经被用掉的有:

APU

Accelerated Processing Unit, 加速处理器,AMD公司推出加速图像处理芯片产品。

BPU

Brain Processing Unit,大脑处理器, 地平线公司主导的嵌入式处理器架构。

CPU

Central Processing Unit 中央处理器, 目前PC core的主流产品。

DPU

Deep learning Processing Unit, 深度学习处理器,最早由国内深鉴科技提出;另说有Dataflow Processing Unit 数据流处理器, Wave Computing 公司提出的AI架构;Data storage Processing Unit,深圳大普微的智能固态硬盘处理器。

EPU

Emotion Processing Unit 情感处理器,Emoshape 并不是这两年才推出 EPU 的,号称是全球首款情绪合成(emotion synthesis)引擎,可以让机器人具有情绪。但是,从官方渠道消息看,EPU 本身并不复杂,也不需要做任务量巨大的神经网络计算,是基于 MCU 的芯片。结合应用 API 以及云端的增强学习算法,EPU 可以让机器能够在情绪上了解所读或所看的内容。结合自然语言生成(NLG)及 WaveNet 技术,可以让机器个性化的表达各种情绪。例如,一部能够朗读的 Kindle,其语音将根据所读的内容充满不同的情绪状态。

FPU

Floating Processing Unit 浮点计算器,浮点单元,不多做解释了。现在高性能的 CPU、DSP、GPU 内都集成了 FPU 做浮点运算。

Force Processing Unit。原力处理器,助成为绝地武士。酷!

GPU

Graphics Processing Unit, 图形处理器,采用多线程SIMD架构,为图形处理而生。

HPU

Holographics Processing Unit 全息图像处理器。Microsoft 专为自家 Hololens 应用开发的。第一代 HPU 采用 28nm HPC 工艺,使用了 24 个 Tensilica DSP 并进行了定制化扩展。HPU 支持 5 路 cameras、1 路深度传感器(Depth sensor)和 1 路动作传感器(Motion Sensor)。Microsoft 在最近的 CVPR 2017 上宣布了 HPU2 的一些信息。HPU2 将搭载一颗支持 DNN 的协处理器,专门用于在本地运行各种深度学习。指的一提的是,HPU 是一款为特定应用所打造的芯片,这个做产品的思路可以学习。据说 Microsoft 评测过 Movidius(见 VPU 部分)的芯片,但是觉得无法满足算法对性能、功耗和延迟的要求,所有才有了 HPU。

IPU

Intelligence Processing Unit,智能处理器, Deep Mind投资的Graphcore公司出品的AI处理器产品。

JPU

请原谅鄙人的词汇量,没什么新奇的想法。。。。

KPU

Knowledge Processing Unit,知识处理器。 嘉楠耘智(canaan)号称 2017 年将发布自己的 AI 芯片 KPU。嘉楠耘智要在 KPU 单一芯片中集成人工神经网络和高性能处理器,主要提供异构、实时、离线的人工智能应用服务。这又是一家向 AI 领域扩张的不差钱的矿机公司。作为一家做矿机芯片(自称是区块链专用芯片)和矿机的公司,嘉楠耘智累计获得近 3 亿元融资,估值近 33 亿人民币。据说嘉楠耘智近期将启动股改并推进 IPO。

另:Knowledge Processing Unit 这个词并不是嘉楠耘智第一个提出来的,早在 10 年前就已经有论文和书籍讲到这个词汇了。只是,现在嘉楠耘智将 KPU 申请了注册商标。

LPU

谁给点灵感?

MPU/MCU

Microprocessor/Micro controller Unit, 微处理器/微控制器,一般用于低计算应用的RISC计算机体系架构产品,如ARM-M系列处理器。

Mind Processing Unit。意念处理器,听起来不错。“解读脑电波”,“意念交流”,永恒的科幻话题。如果采集大量人类“思考”的脑电波数据,通过深度学习,再加上强大的意念处理器 MPU,不知道能否成为 mind-reader。如果道德伦理上无法接受,先了解一下家里宠物猫宠物狗的“想法”也是可以的吗。再进一步,从 mind-reader 发展为 mind-writer,持续升级之后,是不是就可以成为冰与火中的 Skinchanger?

Mobile Processing Unit。移动处理器,似乎没什么意思。

Motion Processing Unit。运动处理器。解析人类、动物的肌肉运动?

题外话:并不是所有的 xPU 都是处理器,比如有个 MPU,是 Memory Protection Unit 的缩写,是内存保护单元,是 ARM 核中配备的具有内存区域保护功能的模块。

NPU

Neural Network Processing Unit,神经网络处理器,是基于神经网络算法与加速的新型处理器总称,如中科院计算所/寒武纪公司出品的diannao系列。

OPU

Optical-Flow Processing Unit。光流处理器。有需要用专门的芯片来实现光流算法吗?不知道,但是,用 ASIC IP 来做加速应该是要的。

PPU

Physical Processing Unit。物理处理器。要先解释一下物理运算,就知道物理处理器是做什么的了。物理计算,就是模拟一个物体在真实世界中应该符合的物理定律。具体的说,可以使虚拟世界中的物体运动符合真实世界的物理定律,可以使游戏中的物体行为更加真实,例如布料模拟、毛发模拟、碰撞侦测、流体力学模拟等。开发物理计算引擎的公司有那么几家,使用 CPU 来完成物理计算,支持多种平台。但是,Ageia 应该是唯一一个使用专用芯片来加速物理计算的公司。Ageia 于 2006 年发布了 PPU 芯片 PhysX,还发布了基于 PPU 的物理加速卡,同时提供 SDK 给游戏开发者。2008 年被 NVIDIA 收购后,PhysX 加速卡产品被逐渐取消,现在物理计算的加速功能由 NVIDIA 的 GPU 实现,PhysX SDK 被 NVIDIA 重新打造。

QPU

Quantum Processing Unit。量子处理器。量子计算机也是近几年比较火的研究方向。作者承认在这方面所知甚少。可以关注这家成立于 1999 年的公司 D-Wave System。DWave 大概每两年可以将其 QPU 上的量子位个数翻倍一次。

RPU

Resistive Processing Unit。阻抗处理单元 RPU。这是 IBM Watson Research Center 的研究人员提出的概念,真的是个处理单元,而不是处理器。RPU 可以同时实现存储和计算。利用 RPU 阵列,IBM 研究人员可以实现 80TOPS/s/W 的性能。

Ray-tracing Processing Unit。光线追踪处理器。Ray tracing 是计算机图形学中的一种渲染算法,RPU 是为加速其中的数据计算而开发的加速器。现在这些计算都是 GPU 的事情了。

Radio Processing Unit, 无线电处理器, Imagination Technologies 公司推出的集合集Wifi/蓝牙/FM/处理器为单片的处理器。

SPU

Streaming Processing Unit。流处理器。流处理器的概念比较早了,是用于处理视频数据流的单元,一开始出现在显卡芯片的结构里。可以说,GPU 就是一种流处理器。甚至,还曾经存在过一家名字为“Streaming Processor Inc”的公司,2004 年创立,2009 年,随着创始人兼董事长被挖去 NVIDIA 当首席科学家,SPI 关闭。

Speech-Recognition Processing Unit。语音识别处理器,SPU 或 SRPU。这个缩写还没有公司拿来使用。现在的语音识别和语义理解主要是在云端实现的,比如科大讯飞。科大讯飞最近推出了一个翻译机,可以将语音传回云端,做实时翻译,内部硬件没有去专门了解。和语音识别相关的芯片如下。

启英泰伦(chipintelli) 于 2015 年 11 月在成都成立。该公司的 CI1006 是一款集成了神经网络加速硬件来做语音识别的芯片,可实现单芯片本地离线大词汇量识别。

MIT 项目。今年年初媒体爆过 MIT 的一款黑科技芯片,其实就是 MIT 在 ISSCC2017 上发表的 paper 里的芯片,也是可以实现单芯片离线识别上 k 个单词。可以参考阅读“分析一下 MIT 的智能语音识别芯片”。

云知声(UniSound)。云知声是一家专攻智能语音识别技术的公司,成立于 2012 年 6 月,总部在北京。云知声刚刚获得 3 亿人民币战略投资,其中一部分将用来研发其稍早公布的 AI 芯片计划,命名“UniOne”。据官方透漏,UniOne 将内置 DNN 处理单元,兼容多麦克风、多操作系统。并且,芯片将以模组的形式提供给客户,让客户直接拥有一整套云端芯的服务。

Smart Processing Unit。聪明的处理器,听起来很 Q。

Space Processing Unit。空间处理器,高大上,有没有。全景摄像,全息成像,这些还都是处理生活空间。当面对广阔的太阳系、银河系这些宇宙空间,是不是需要新的更强大的专用处理器呢?飞向 M31 仙女座星系,对抗黑暗武士,只靠 x86 估计是不行的。

TPU

Tensor Processing Unit 张量处理器, Google 公司推出的加速人工智能算法的专用处理器。目前一代TPU面向Inference,二代面向训练。

UPU

Universe Processing Unit。宇宙处理器。和 Space Processing Unit 相比,更喜欢哪个?

VPU

Vector Processing Unit 矢量处理器,Intel收购的Movidius公司推出的图像处理与人工智能的专用芯片的加速计算核心。

Vision Processing Unit。视觉处理器 VPU 也有希望成为通用名词。作为现今最火热的 AI 应用领域,计算机视觉的发展的确能给用户带来前所未有的体验。为了处理计算机视觉应用中遇到的超大计算量,多家公司正在为此设计专门的 VPU。

Movidius(已被 Intel 收购)。Movidius 成立于 2006 年,总部位于硅谷的 San Mateo,创始人是两个爱尔兰人,所以在爱尔兰有分部。Movidius 早期做的是将旧电影转为 3D 电影的业务,后期开始研发应用于 3D 渲染的芯片,并开始应用于计算机视觉应用领域(这说明:1,芯片行业才是高技术含量、高门槛、高价值的行业;2,初创公司要随着发展调整自己的战略)。Movidius 开发的 Myriad 系列 VPU 专门为计算机视觉进行优化,可以用于 3D 扫描建模、室内导航、360°全景视频等更前沿的计算机视觉用途。例如,2014 年,谷歌的 Project Tango 项目用 Myriad 1 帮助打造室内三维地图;2016 年,大疆的“精灵 4”和“御”都采用了 Movidius 的 Myriad 2 芯片。采用 TSMC 28nm 工艺的 Myriad2 中集成了 12 个向量处理器 SHAVE (Streaming Hybrid Architecture Vector Engine)。按照 Movidius 的说法,SHAVE 是一种混合型流处理器,集成了 GPU、 DSP 和 RISC 的优点,支持 8/16/32 bit 定点和 16/32 bit 浮点计算,而且硬件上支持稀疏数据结构。此外,Myriad2 中有两个 RISC 核以及 video 硬件加速器。据称,Myriad2 可以同时处理多个视频流。

Inuitive 一家以色列公司,提供 3D 图像和视觉处理方案,用于 AR/VR、无人机等应用场景。Inuitive 的下一代视觉处理器 NU4000 采用 28nm 工艺,选择使用 CEVA 的 XM4 DSP,并集成了深度学习处理器(自己开发?或者购买 IP?)和深度处理引擎等硬件加速器。

DeepVision 一家总部位于 Palo Alto 的 start-up,为嵌入式设备设计和开发低功耗 VPU,以支持深度学习、CNN 以及传统的视觉算法,同时提供实时处理软件。

Visual Processing Unit。这里是 visual,不是 vision。ATI 一开始称自家显卡上的芯片为 VPU,后来见贤思齐,都改叫 GPU 了。

Video Processing Unit。视频处理器。处理动态视频而不是图像,例如进行实时编解码。

Vector Processing Unit。向量处理器。标量处理器、向量处理器、张量处理器,这是以处理器处理的数据类型进行的划分。现在的 CPU 已经不再是单纯的标量处理器,很多 CPU 都集成了向量指令,最典型的就是 SIMD。向量处理器在超级计算机和高性能计算中,扮演着重要角色。基于向量处理器研发 AI 领域的专用芯片,也是很多公司的选项。例如,前面刚提到 Movidius 的 Myriad2 中,就包含了 12 个向量处理器。

Vision DSP。针对 AI 中的计算机视觉应用,各家 DSP 公司都发布了 DSP 的 Vision 系列 IP。简单罗列如下。

CEVA 的 XM4,最新的 XM6 DSP。除了可以连接支持自家的硬件加速器 HWA(CEVA Deep Neural Network Hardware Accelerator ),也可以支持第三方开发的 HWA。前面提到的 Inuitive 使用了 XM4。可以参考“处理器 IP 厂商的机器学习方案 - CEVA”。

Tensilica(2013 年被 Cadence 以 3.8 亿美元收购)的 P5、P6,以及最新的 C5 DSP。一个最大的特色就是可以用 TIE 语言来定制指令。前面微软的 HPU 中使用他家的 DSP。可以参考“神经网络 DSP 核的一桌麻将终于凑齐了”。

Synopsys 的 EV5x 和 EV6x 系列 DSP。可以参考“处理器 IP 厂商的机器学习方案 - Synopsys”。

Videantis 的 v-MP4 系列。Videantis 成立于 1997 年,总部位于德国汉诺顿。v-MP4 虽然能做很多机器视觉的任务,但还是传统 DSP 增强设计,并没有针对神经网络做特殊设计。

WPU

Wearable Processing Unit, 可穿戴处理器,一家印度公司Ineda Systems公司推出的可穿戴片上系统产品,包含GPU/MIPS CPU等IP。

Ineda Systems 在 2014 年大肆宣传了一下针对 IOT 市场推出的 WPU 概念,获得了高通和三星的注资。Ineda Systems 研发的这款“Dhanush WPU”分为四个级别,可适应普通级别到高端级别的可穿戴设备的运算需求,可以让可穿戴设备的电池达到 30 天的持续续航、减少 10x 倍的能耗。但是,一切似乎在 2015 年戛然而止,没有了任何消息。只在主页的最下端有文字显示,Ineda 将 WPU 申请了注册商标。有关 WPU 的信息只有大概结构,哦,对了,还有一个美国专利。

Wisdom Processing Unit。智慧处理器。这个 WPU 听起来比较高大上,拿去用,不谢。不过,有点“脑白金”的味道。

XPU

百度与Xilinx公司在2017年Hotchips大会上发布的FPGA智能云加速,含256核。

百度公开了其 FPGA Accelerator 的名字,就叫 XPU。

YPU

Y?没想法,大家加油抢注名字了。

ZPU

Zylin Processing Unit, 由挪威Zylin 公司推出的一款32位开源处理器。

挪威公司 Zylin 的 CPU 的名字。为了在资源有限的 FPGA 上能拥有一个灵活的微处理器,Zylin 开发了 ZPU。ZPU 是一种 stack machine(堆栈结构机器),指令没有操作数,代码量很小,并有 GCC 工具链支持,被称为“The worlds smallest 32 bit CPU with GCC toolchain”。Zylin 在 2008 年将 ZPU 在 opencores 上开源。有组织还将 Arduino 的开发环境进行了修改给 ZPU 用。

其他非 xPU 的 AI 芯片

寒武纪科技(Cambricon) 中科院背景的寒武纪并没有用 xPU 的方式命名自家的处理器。媒体的文章既有称之为深度学习处理器 DPU 的,也有称之为神经网络处理器 NPU 的。陈氏兄弟的 DianNao 系列芯片架构连续几年在各大顶级会议上刷了好几篇 best paper,为其公司的成立奠定了技术基础。寒武纪 Cambricon-X 指令集是其一大特色。目前其芯片 IP 已扩大范围授权集成到手机、安防、可穿戴设备等终端芯片中。据流传,2016 年就已拿到一亿元订单。在一些特殊领域,寒武纪的芯片将在国内具有绝对的占有率。最新报道显示,寒武纪又融了 1 亿美元。

Intel Intel 在智能手机芯片市场的失利,让其痛定思痛,一改当年的犹豫,在 AI 领域的几个应用方向上接连发了狠招。什么狠招呢,就是三个字:买,买,买。在数据中心 / 云计算方面,167 亿美金收购的 Altera,4 亿美金收购 Nervana;在移动端的无人机、安防监控等方面,收购 Movidius(未公布收购金额);在 ADAS 方面,153 亿美金收购 Mobileye。Movidius 在前面 VPU 部分进行了介绍,这里补充一下 Nervana 和 Mobileye(基于视觉技术做 ADAS 方案,不是单纯的视觉处理器,所以没写在 VPU 部分)。

Nervana Nervana 成立于 2014 年,总部在 SanDiego,以提供 AI 全栈软件平台 Nervana Cloud 为主要业务。和硬件扯上关系的是,Nervana Cloud 除了支持 CPU、GPU 甚至 Xeon Phi 等后台硬件外,还提供有自家定制的 Nervana Engine 硬件架构。根据 The Next Platform 的报道“Deep Learning Chip Upstart Takes GPUs to Task”,Nervana Engine 使用 TSMC 28nm 工艺,算力 55 TOPS。报道发布不到 24 小时,就被 Intel 收购了,全部 48 位员工并入 Intel。Intel 以 Nervana Engine 为核心打造了 Crest Family 系列芯片。项目代码为“Lake Crest”的芯片是第一代 Nervana Engine,“Knights Crest”为第二代。哦,对了,Nervana 的 CEO 在创立 Nervana 之前,在高通负责一个神经形态计算的研究项目,就是上面提到的 Zeroth。

Mobileye 一家基于计算机视觉做 ADAS 的以色列公司,成立于 1999 年,总部在耶路撒冷。Mobileye 为自家的 ADAS 系统开发了专用的芯片——EyeQ 系列。2015 年,Tesla 宣布正在使用 Mobileye 的芯片(EyeQ3)和方案。但是,2016 年 7 月,Tesla 和 Mobileye 宣布将终止合作。随后,Mobile 于 2017 年被 Intel 以$153 亿收入囊中,现在是 Intel 的子公司。Mobileye 的 EyeQ4 使用了 28nm SOI 工艺,其中用了 4 个 MIPS 的大 CPU core 做主控和算法调度以及一个 MIPS 的小 CPU core 做外设控制,集成了 10 个向量处理器(称为 VMP,Vector Microcode Processor)来做数据运算(有点眼熟,回去看看 Movidius 部分)。Mobileye 的下一代 EyeQ5 将使用 7nm FinFET 工艺,集成 18 个视觉处理器,并且为了达到自动驾驶的 level 5 增加了硬件安全模块。

比特大陆 Bitmain 比特大陆设计的全定制矿机芯片性能优越,让其大赚特赚。在卖矿机芯片之余,比特大陆自己也挖挖矿。总之,芯片设计能力非凡、土豪有钱的比特大陆对标 NVIDIA 的高端 GPU 芯片,任性地用 16nm 的工艺开启了自家的 AI 芯片之路。芯片测试已有月余,据传功耗 60W 左右,同步在招揽产品、市场人员。最近的推文爆出了这款 AI 芯片的名字:“智子(Sophon)”,来自著名的《三体》,可见野心不小,相信不就即将正式发布。

华为&海思 市场期待华为的麒麟 970 已经很长时间了,内置 AI 加速器已成公开的秘密,据传用了寒武纪的 IP,就等秋季发布会了。还是据传,海思的 HI3559 中用了自己研发的深度学习加速器。

苹果 苹果正在研发一款 AI 芯片,内部称为“苹果神经引擎”(Apple Neural Engine)。这个消息大家并不惊讶,大家想知道的就是,这个 ANE 会在哪款 iphone 中用上。

高通 高通除了维护其基于 Zeroth 的软件平台,在硬件上也动作不断。收购 NXP 的同时,据传高通也一直在和 Yann LeCun 以及 Facebook 的 AI 团队保持合作,共同开发用于实时推理的新型芯片。

还有一些诸如 Leapmind、REM 这样的 start-up,就不一一列举。

目前三位数的xpu还剩俩仨个(抓紧抢注啊!),等三位数的XPU被用完后,即将会出现XXPU,XXXPU,XXXXPU......,并且会以更快的发展速度带来更长的名字,最后是更难记住。

突然感觉还是现在的这些XPU的名字听起来顺口啊,毕竟只有三个字母。

当然,将来的事情等到将来再说,过好当下才是重要的事情。

不说了,回去打扫卫生了,老板丹炉里的灰还等着去掏呢。

谷歌第四代TPU芯片更多细节曝光

Google I/O 2022的 TPUv4 矩阵数学引擎进行架构深入研究。

这家搜索引擎和广告巨头是这个星球上最大的人工智能创新者之一,因为需要使用大量的数据,确实也在大会上提供了更多关于 TPUv4 处理器和使用的更多信息。

谷歌还表示,正在俄克拉荷马州梅斯县的数据中心安装 8 个 TPUv4 系统Pods,该数据中心正在接近 9 exaflops的总计算能力,供其谷歌云部门使用,这样研究人员和企业就可以访问相同的类型和谷歌必须自己进行内部人工智能开发和生产的计算能力。

自 2007 年以来,谷歌一直在塔尔萨东北部的梅斯县运营数据中心,自那时以来已投资 44 亿美元用于设施建设。位于美国的地理中心——就在南边和西边——这使得很有用,因为对美国大部分地区的延迟相对较短。现在,根据定义,梅斯县拥有世界上最大的铁矿之一来推动人工智能工作量。(如果八个 TPUv4 pod 联网在一起并且可以同时工作,可能会毫不含糊地说“最大的”......谷歌肯定做到了,正如将在下面的引用中看到的那样。)

在他的主题演讲中,谷歌及其母公司 Alphabet 的首席执行官 Sundar Pichai 顺便提到,TPUv4 pod 正在其云上进行预览。

“今天分享的所有进步都是可能的,因为基础设施不断创新,”Pichai 谈到一些非常有趣的自然语言和沉浸式数据搜索引擎增强功能时说,已经将这些功能融入到各种应用中。“最近,宣布计划在美国各地的数据中心和办事处投资 95 亿美元。最先进的数据中心之一位于俄克拉荷马州的梅斯县,很高兴地宣布,将为所有的 Google Cloud 客户推出全球最大的公开机器学习中心。这个机器学习中心有 8 个 Cloud TPU v4 pod,是在为 Google 最大的神经模型提供支持的同一网络基础设施上定制构建的。总共提供近 9 exaflops 的计算能力,为客户带来前所未有的运行复杂模型和工作负载的能力。希望这将推动从医药到物流再到可持续发展等各个领域的创新。”

Pichai 补充说,这个基于 TPUv4 Pods的人工智能中心已经有

90% 的电力来自可持续的无碳资源。(他没有说风能、太阳能或水电有多少。)

在了解 TPUv4 芯片和

Pod 的速度和馈送之前,可能值得指出的是,据所知,Google 已经在其面向内部的数据中心中拥有 TPUv5 Pod,而且可能拥有更大的集合的 TPU 来驱动自己的模型并使用 AI 算法和例程增强自己的应用程序。那将是 Google 做事的老方法:在销售N-1代产品时谈论N代产品,并且已经转移到N+1代产品来处理其内部工作负载。

情况似乎并非如此。在Google Cloud 副总裁兼基础设施总经理 Sachin Gupta 和 Cloud TPU 产品经理 Max Sapozhnikov文章中,去年构建 TPUv4 系统时,Google 向

Cohere 的研究人员提供了早期访问权限、LG AI Research、Meta AI 和 Salesforce Research,此外,还补充说,TPUv4 系统用于创建 Pathways 语言模型 (PaLM),该模型支持作为今天主题演讲核心的自然语言处理和语音识别创新。具体来说,PaLM

是在两个 TPUv4 pod 上开发和测试的,每个 pod 都有 4,096 个 TPUv4 矩阵数学引擎。

如果谷歌最闪亮的新模型是在 TPUv4 上开发的,那么可能没有隐藏在某个数据中心的 TPUv5 舰队。虽然会添加,但如果 TPUv5 机器被隐藏在距离办公室西南 26.7 英里处的 Lenoir 数据中心,那就太好了。

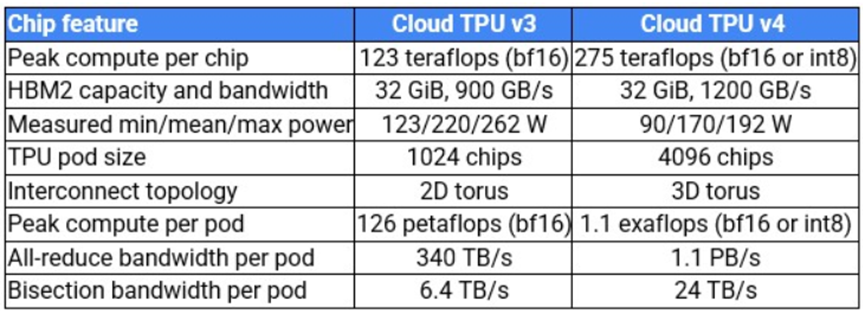

让谈谈一些反馈和速度。最后,这里是一些将 TPUv4 与

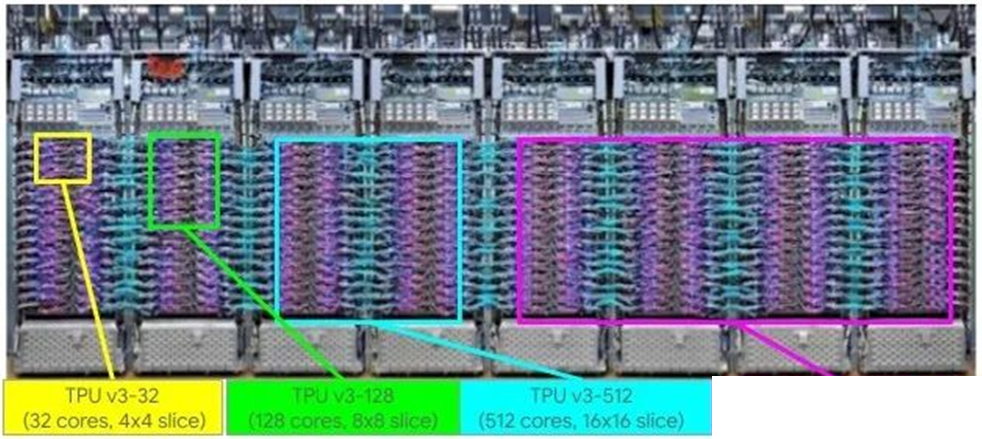

TPUv3 进行比较的容量:

当 Pichai 暗示 TPUv4 时,猜测谷歌正在为这一代 TPU 转向 7 纳米工艺,但考虑到非常低的功耗,看起来可能是使用 5 纳米工艺蚀刻的。(假设谷歌试图保持功率包络不变,显然想减少。)还猜测正在将核心数量增加一倍,从 TPUv3 上的两个核心移动到 TPUv4 上的四个核心,这谷歌没有确认或否认。

在内核翻倍的同时将性能翻倍将使 TPUv4 达到每芯片 246 teraflops,从 16 纳米到 7 纳米将允许在大致相同的功率包络和大约相同的时钟速度下翻倍。转向 5 纳米可以使芯片更小,运行速度更快,同时降低功耗——随着 5 纳米工艺的成熟,芯片更小,成品率可能更高。平均功耗下降了 22.7%,考虑到二换工艺节点从 TPUv3 跳转到 TPUv4,时钟速度提高了 11.8%。

该表和 Google 在此博客中所做的声明中有一些非常有趣的内容。

除了 TPUv4 的芯片制造过程带来的 2X 内核和轻微的时钟速度增加之外,有趣的是,谷歌将内存容量保持在 32 GB,并且没有转移到 Nvidia 与“Hopper”一起使用的 HBM3 内存GH100 GPU 加速器。Nvidia 痴迷于设备上的内存带宽,并且通过其 NVLink 和 NVSwitch 扩展,节点内的内存带宽以及现在跨节点的内存带宽,单个映像中最多有

256 个设备。

Google 并不担心专有 TPU 互连、设备内存带宽或设备内存容量上的内存原子(据所知)。TPUv4 具有与 TPUv3 相同的

32 GB 容量,使用相同的 HBM2 内存,并且速度仅提高了

33%,低于 1.2 TB/秒。Google 感兴趣的是 TPU Pods互连的带宽,正在转向 3D 环面设计,该设计将 64 个 TPUv4 芯片与“环绕连接”紧密耦合——这是与 TPUv3

Pods一起使用的 2D 环面互连无法实现的。环面互连尺寸的增加允许将更多 TPU 拉入更紧密的子网以进行集体操作。(这引出了一个问题,为什么不是 4D、5D 或 6D 环面呢?)

TPUv4 pod 的 TPU 芯片数量是之前的4 倍——高达4,096个 ,TPU 内核的数量则高达16,384 ,是之前的两倍;相信 Google 已将 MXU 矩阵数学单元的数量保持在每个内核两个,但这只是一种预感。

Google 可以保持 TPU 核心数量相同,并将 MXU 单元增加一倍,并获得相同的原始性能;不同之处在于需要在这些 MXU 上完成多少前端标量/矢量处理。无论如何,在 Google 的 DeepMind 部门创建的 16 位 BrainFloat (BF16) 浮点格式下,TPUv4 pod 提供 1.1 exaflops算力,而 BF16 仅提供 126 petaflops。原始计算量增加了 8.7 倍,与整个 pod 的

all-to-all 缩减带宽增加了 3.3 倍以及整个

pod 的 TPUv4 互连的对分带宽增加了 3.75 倍相平衡。

博客中的这句话引起了兴趣:“每个 Cloud TPU v4 芯片的峰值 FLOP 比 Cloud TPU v3 多约 2.2 倍,每美元的峰值 FLOP 多约 1.4 倍。” 如果根据该声明进行计算,这意味着使用 TPUv4 在 Google Cloud 上租用 TPU 的价格上涨了 60%,但工作量是原来的2.2 倍。这种定价和性能飞跃与 Google 期望从其为其数据中心购买的交换机 ASIC 中获得的那种价格/性能改进完全一致,这些交换机通常以 1.3 到 1.5 倍的成本提供 2 倍的带宽。TPUv4 有点贵,但有更好的网络来运行更大的模型,这也有成本。

TPUv4 pod 可以在 Google Cloud 上的 VM 中运行,大小从低至四个芯片到“数千个芯片”不等,认为这意味着包括整个

pod。

谷歌长文总结四代TPU打造经验:里程碑式的TPUv4是怎样炼成的?

TPUv1 到 TPUv4,谷歌有哪些想要分享的经验?

作为图灵奖得主、计算机架构巨擘,David Patterson 在 2016 年从伯克利退休后,以杰出工程师的身份加入了谷歌大脑团队,为几代 TPU 的研发做出了卓越贡献。

几个月前谷歌强势推出了 TPUv4,并撰写论文讲述了研发团队的设计思路和从前几代 TPU 中吸取的经验。

论文链接:https://www.gwern.net/docs/ai/2021-jouppi.pdf

当前,深度神经网络在商用领域的特定架构(DSA)已初步建立。该论文回顾了四代 DSA 的演变历程。生产经验推动了新设计的诞生,不再受限于 CPU 的缓慢发展和摩尔定律的衰退。

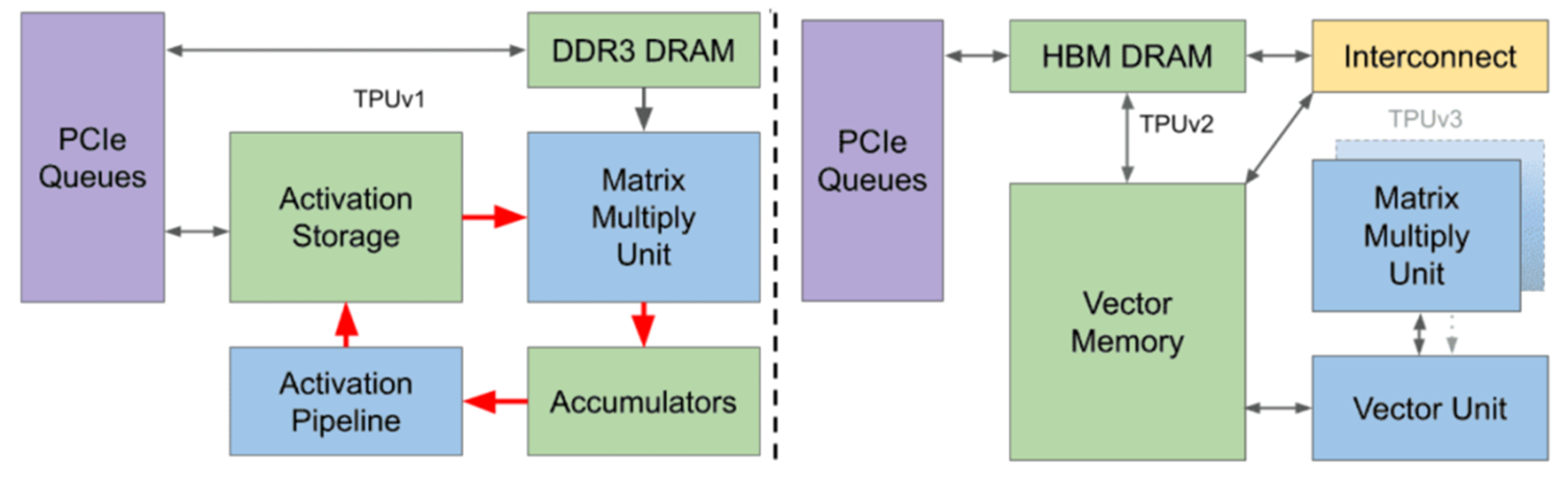

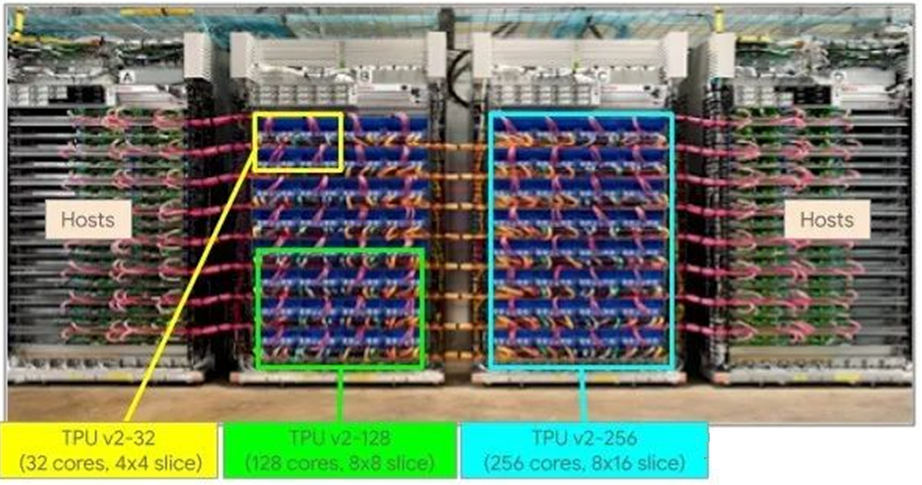

图 1:从 2015 年开始部署在谷歌数据中心的 3 个 TPU 的框图。

下表展示了几代 TPU 的关键特性,其中 TPUv4i 中 i 代表的是「推理」。

TPUv1 是谷歌第一代 DNN DSA(图 1 左),能够处理推理任务。近年来,模型训练的规模逐渐增大,所以一种新的改进是添加一个片到片的定制互连结构 ICI,使得搭载 TPUv2 的超级计算机芯片数量可多达 256 个。

与 TPUv1 不同,TPUv2 每个芯片有两个 TensorCore。芯片上的全局线不会随着特征尺寸的缩小而缩小 ,因此相对延迟会增加。每个芯片有两个较小的核,以避免单个大型全芯片核的过度延迟。谷歌并没有继续增加核的数量,因为相信两个强大的核比许多不够强的核更易于高效地编译程序。

TPUv3 则在 TPUv2 的基础上微调了设计,采用相同的技术,拥有 2 倍的 MXU 和 HBM 容量,并将时钟频率、内存带宽和 ICI 带宽提高至 1.3 倍。一台

TPUv3 超级计算机可以扩展到 1024 个芯片。TPUv3

在使用 16 位浮点(bfloat16 vs IEEE

fp16 时与 Volta GPU 相当。然而,Volta 需要使用 IEEE fp32 来训练谷歌的生产工作负载,因此 TPUv3 快了 5 倍以上。一些扩展到 1024 个芯片的应用程序可以获得 97%-99% 的完美线性加速。

2015 年以来的十大经验

1. 逻辑、线路、SRAM 和 DRAM 的发展不平衡

Horowitz 对操作功耗的见解启发了许多 DSA 的设计。表 2 显示 7 nm 相对于 45 nm

的平均增益是 2.6 倍,但并不均匀:

- SRAM 访问只提高了 1.3 - 2.4 倍,部分原因是 SRAM 的密度扩展速度比之前慢。65 nm 与 7 nm 相比, SRAM 每平方毫米的容量密度仅约为理想扩展的 1/5;

- 得益于封装的革新,DRAM 访问量提高了 6.3 倍。HBM 将短 DRAM dies 栈放置在宽总线上靠近 DSA 的位置;

- 但每单位长度线路的功耗提高不到 2 倍(表 2 未显示这一点)。较差的线路延迟缩放导致 TPUv2/v3 相比于 TPUv1,从使用 1 个较大核变为使用 2 个较小核。

逻辑方面的改进速度比线路和 SRAM 快得多。HBM 比 GDDR6 和 DDR DRAM 更节能,且 HBM 的每 GB/s 的带宽成本最低。

2. 利用预先的编译器优化

自 20 世纪 80 年代以来,新架构的命运与编译器的质量密切相关。事实上,编译器问题可能会破坏安腾(Itanium)的 VLIW 架构,但许多 DSA 依赖于 VLIW,包括 TPU。

架构师希望在模拟器上开发出出色的编译器,然而大部分进展发生在硬件可用之后,因为这样编译器编写者能够测量代码所花费的实际时间。因此,如果能够利用预先的编译器优化而不是从头开始重新编写,那么快速实现架构的全部潜力会容易得多。

3. 性能 / TCO 和性能 / CapEx 的设计

CapEx 指的是一个项目的价格。OpEx 指的是运营成本,包括电力消耗和电力供应。标准的会计处理方法是在 3-5 年内摊销计算机 CapEx,因此 3 年的 TCO = CapEx + 3 ✕ OpEx。

谷歌等大多数公司更关心生产应用程序的性能 / TCO (perf/TCO),而不是基准的原始性能或性能 / CapEx (perf/CapEx) 。虽然 TCO 是谷歌在产品设计过程中优化的主要变量,但资本支出仍然会影响一些业务决策。

4. 支持向后 ML 兼容

一些 DNN 具有上市时间限制,因为及时性可能会带来经济价值。在这种情况下,向后 ML 兼容性成为一种原则。新 CPU 的目标是相同的,即应该获得完全相同的结果,包括相同的异常行为和相关性能,从 TPUv2 开始,训练和围绕TPU生成的服务都是按照这种情况设计的。

5. 推理 DSA 需要全局范围的风冷

75W TPUv1 和 280W TPUv2 采用风冷,但 450W 功率的 TPUv3 使用了液冷。液冷需要将 TPU 放置在几个相邻的机架中,以分摊冷却基础设施。这种放置限制对于训练已经由几个相邻机架组成的超级计算机来说不是问题。此外,将训练限制在拥有更多空间的几个数据中心的缺点是很小的,因为没有必要进行广泛部署。

6. 一些推理应用程序需要浮点运算

DNN 量化旨在维持使用整数下的实时推理模型质量,即使所有训练都是在浮点下完成的。量化计算可以节省面积和功耗,但这需要和质量降低、延迟部署进行权衡,并且一些应用程序在量化时不能很好地工作。

7. 生产推理通常需要多租户模式

与 CPU 一样,DSA 应该支持多租户(multi-tenancy)模式。如果应用程序使用许多模型,共享则可以降低成本并减少延迟。例如,翻译 DNN 需要许多语言对,而语音 DNN 必须处理多种方言。多租户模式还支持多种批大小,以权衡吞吐量和延迟。另一方面,采用良好的软件工程实践方式也是很重要的,例如面向一小部分客户尝试新功能,或缓慢部署新版本以减少出现问题的机会。表 3 显示了超过 80% 的生产推理工作负载需要多租户。

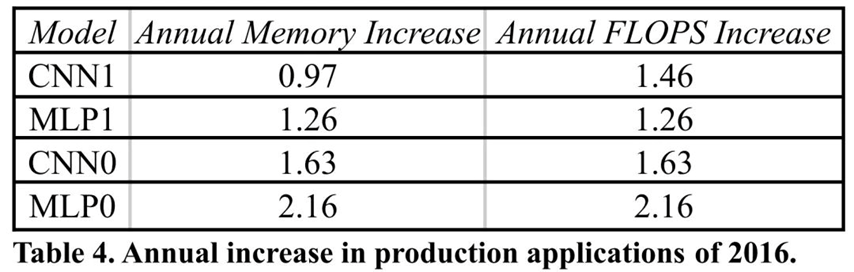

8. DNN 的内存和计算需求每年约增长 1.5 倍

与基准测试不同,程序员不断改进生产应用程序,这通常会增加内存大小和计算需求。表 4 跟踪了仍然在 TPUv1/v2/v3 上运行的四个原始生产推理应用程序的内存大小和计算量的年均增长。生产 DNN 每年约增长 1.5 倍,增长速度与摩尔定律一样快,就像早期的 PC 软件一样。这个比率表明架构师应该提供空间,以便 DSA 可以在其整个生命周期内保持有用。

9. DNN 工作负载随着 DNN 的突破而发展

表 3 中的 DNN 约占谷歌 2020 年推理工作负载的 100%。2016 年的 MLP 和 CNN 仍然很受欢迎,尽管一些应用程序从 MLP 切换到 BERT DNN (28%)。BERT 出现于 2018 年,但已经占了 28% 的工作负载。为了提高质量,transformer编码器加上 LSTM 解码器 (RNN0) 和 Wave RNN (RNN1) 取代了 LSTM (29%)。这个经验说明了可编程性和灵活性对于推理DSA的重要性。

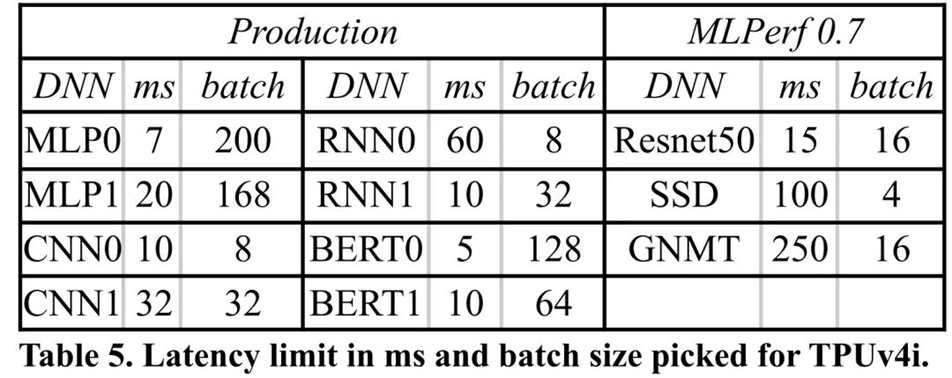

10. 推理 SLO 的限制是 P99 延迟,而不是批大小

近来 DSA 的论文根据批大小重新定义了延迟限制,通常设置为

1。表 5 给出了生产应用程序的 P99 时间 SLO 和 MLPerf 推理基准测试,并显示了近来符合 SLO 的 TPU 的最大批。显然,数据中心应用程序限制了延迟,而不是批大小。未来的 DSA 应该利用更大的批大小。

这十条经验如何塑造了现在的 TPUv4i?

鉴于利用预先的编译器优化和向后 ML 兼容性的重要性,再加上重用早期硬件设计的好处,TPUv4i 沿袭了 TPUv3 的一些设计。该论文集中讨论了 TPUv3 和下一代的不同之处,谷歌重新考虑了构建单个芯片的策略,使芯片既能优化训练,又能用于推理。

编译兼容,而不是二进制兼容。鉴于 TPUv2 和 TPUv3 共享

322 位 VLIW 指令包长度,传统架构思想是 TPUv4i

和 TPUv4 尝试保持向后的二进制兼容性,但谷歌选择了编译兼容。

在片上SRAM存储中增加了普通内存CMEM。DSA 在编译之后首先考虑的是内存系统。限制内存开销可以提高 perf/CapEx,但是可能会影响 perf/TCO。除了推理之外,多租户、快速增长的 DNN 和 HBM 的高能效,都促使 TPUv4i 继续使用类似于 TPUv3 的 HBM。

四维张量 DMA。内存系统架构对于任何

DNN 加速器都是至关重要的,因此应被设计为满足常用情况工作负载的最大性能,同时对于其他模型足够灵活。TPUv4i 包含张量 DMA 引擎,分布在整个芯片的非核心部分,以减轻互连延迟和线路扩展的影响。

自定义片上互连(OCI)。快速增长和不断发展的 DNN 工作负载促使 TPU 的非核心具备更大的灵活性。过去 TPU 设计的每个组件都是点对点连接的(如图 1 所示),随着内存带宽的增加和组件数量的增加,点对点方法变得过于昂贵,需要大量路由资源和 die area。还需要预先选择支持哪种通信模式,这限制了未来软件使用芯片的方式。

因此 TPUv4i 增加了一个共享的片上互连 OCI,连接了 die 上所有的部件,并且可以基于当前的部件来扩展拓扑。OCI 对于增加 CMEM 来说特别重要,在 HBM、CMEM 和 VEM 之间进行分配和数据传输的方式会持续进化。

运算改进。另一个重要变化是运算单元。需要量化的风险和 ML 向后兼容性的重要性意味着,尽管要进行推理,仍然要保留 TPUv3 中的 bf16 和 fp32。谷歌还希望对

TPUv1 的应用程序进行量化,以便轻松地将其移植到 TPUv4i,TPUv4i 也支持 int8。

时钟速率和 TDP。用于推理的风冷和减少 TCO 导致时钟频率变为 1.05 GHz,芯片 TDP 为 175W,再次接近

TPUv1(75W)而不是 TPUv3(450W)。

ICI 扩展。为了给未来的 DNN 增长提供空间,TPUv4i 有 2 个 ICI 链路,这样每块板上的 4 个芯片可以通过模型分区快速访问附近的芯片内存(TPUv3 使用 4 个 ICI 链路)。随着软件的成熟和 DNN 的增长,应用程序可能会用到这些扩展。

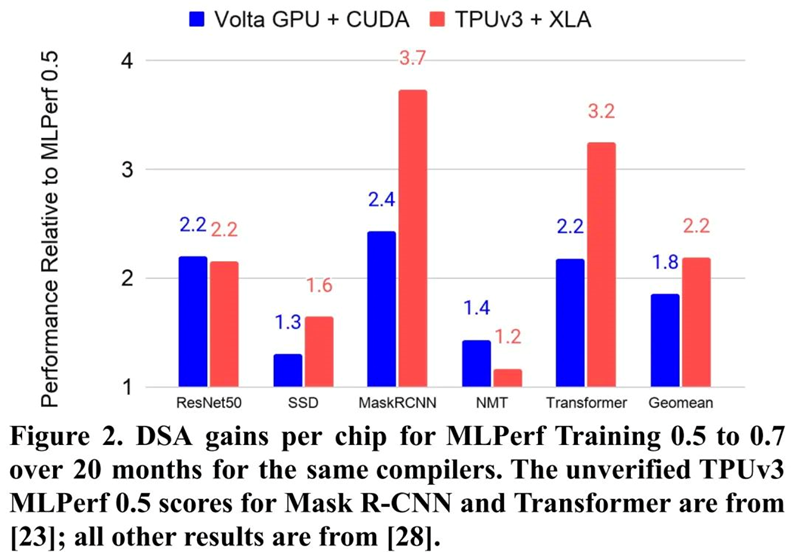

工作负载分析特征。基于 TPUv1 的经验,TPUv4i 包含了大量的追踪和性能计数器硬件特征,特别是在非核心部分。被软件堆栈用于测量和分析用户工作负载中的系统级瓶颈,并指导持续的编译级和应用级优化,如下图2所示。这些特征增加了设计时间和面积,但这种尝试是值得的。随着 DNN 工作负载的增加和发展,这些特征可以显著提升系统级性能,并提高产品在整个生命周期中的生产力(如表 4 所示)。

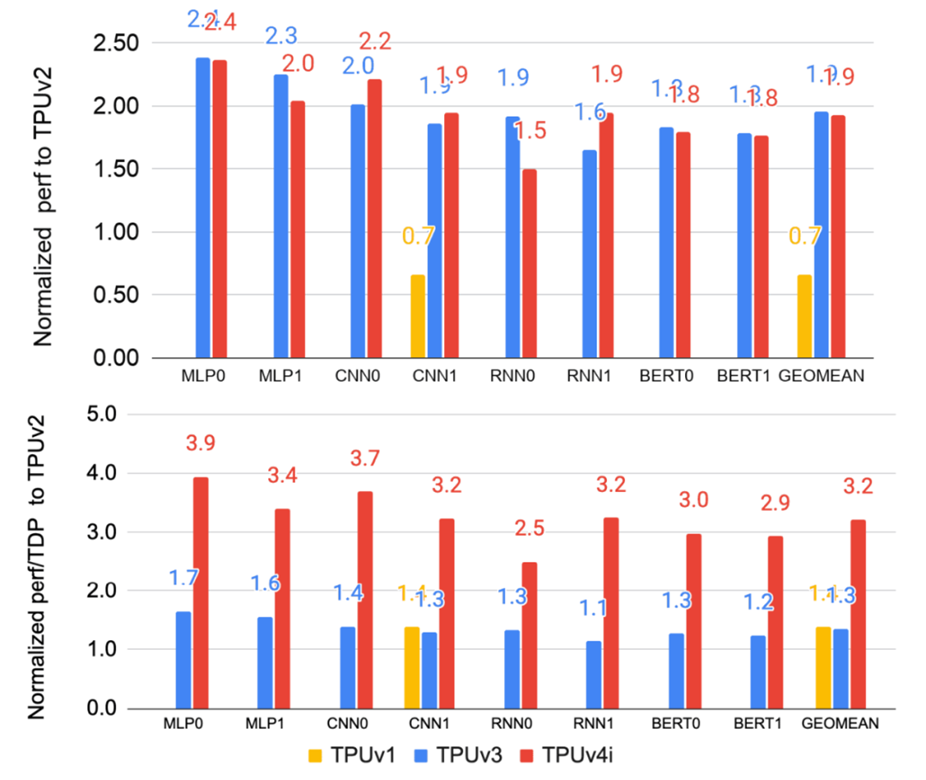

TPUv4i 性能分析

下图比较了TPUv1、TPUv3和TPUv4i在生产推理应用上相对于TPUv2的性能和perf/TDP。TPUv3 和 TPUv4i 都比 TPUv2 快 1.9 倍以上,TPUv1 的速度大概是 TPUv2 的 70% 左右。更大、更热的 TPUv2/v3 芯片有两个内核,而较小的 TPUv4i 芯片有一个内核,这使 TPUv4i 芯片在 perf/TCO 和部署方面更胜一筹。

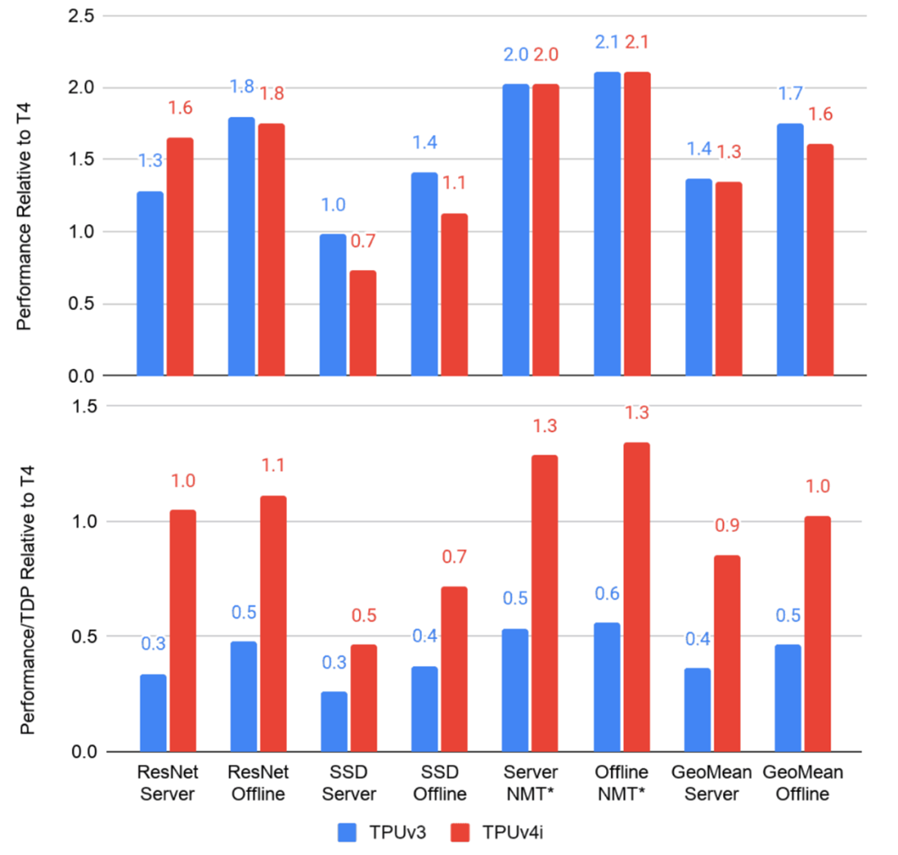

下图使用 MLPerf 推理 0.5-0.7 版本基准测试比较了 TPUv3 和 TPUv4i 相比于 NVIDIA T4 的性能和 perf/(system)TDP。

更深度的性能表现:CMEM

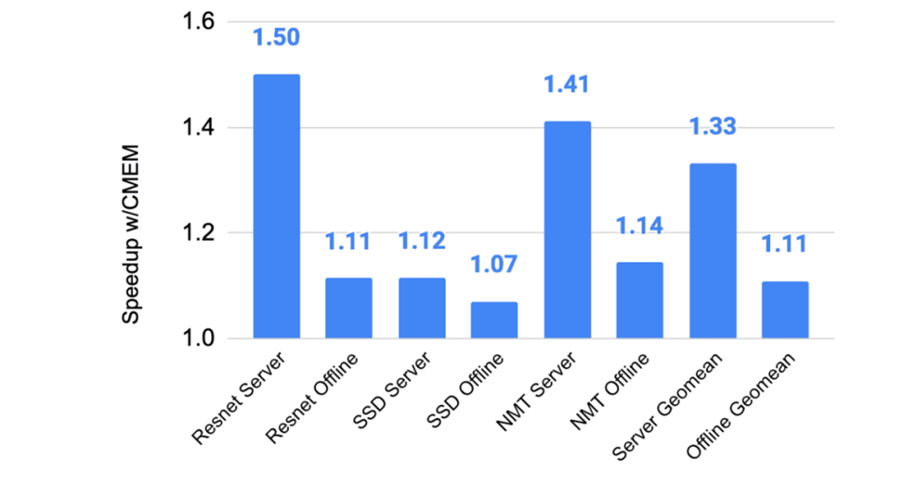

下图展示了 TPUv4i 增加 CMEM 给 MLPerf 推理 0.5-0.7 基准测试带来的收益。由于延迟和延迟受限服务性能之间的关系在某些效用点上是非线性的,因此离线的平均收益只有 1.1 倍,而服务的平均收益是 1.3 倍。

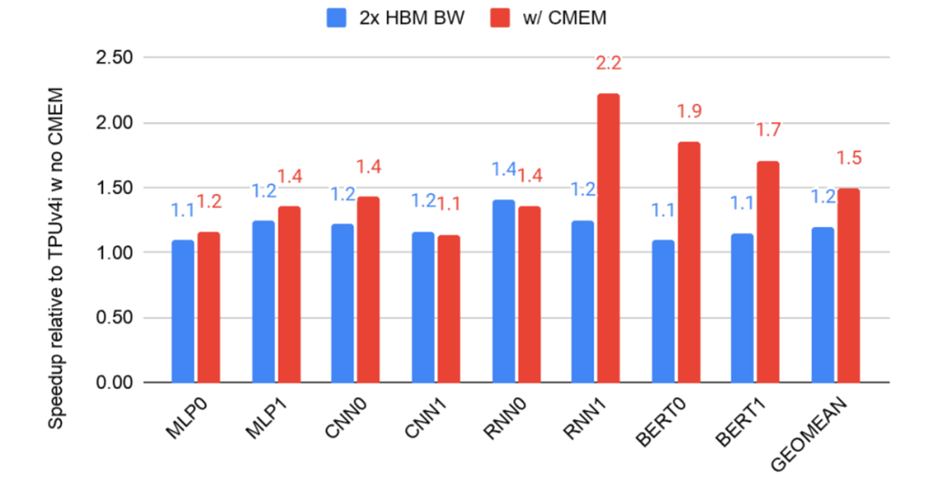

为了理解 CMEM 对生产应用的影响,下图比较了启用 CMEM 的双倍 HBM 带宽与启用 CMEM 的标准 HBM 带宽的性能。通过编译标志来禁用 CMEM,同时在 TPUv4 运行时禁用一个内核,使得一个内核的 HBM 带宽增加了一倍。

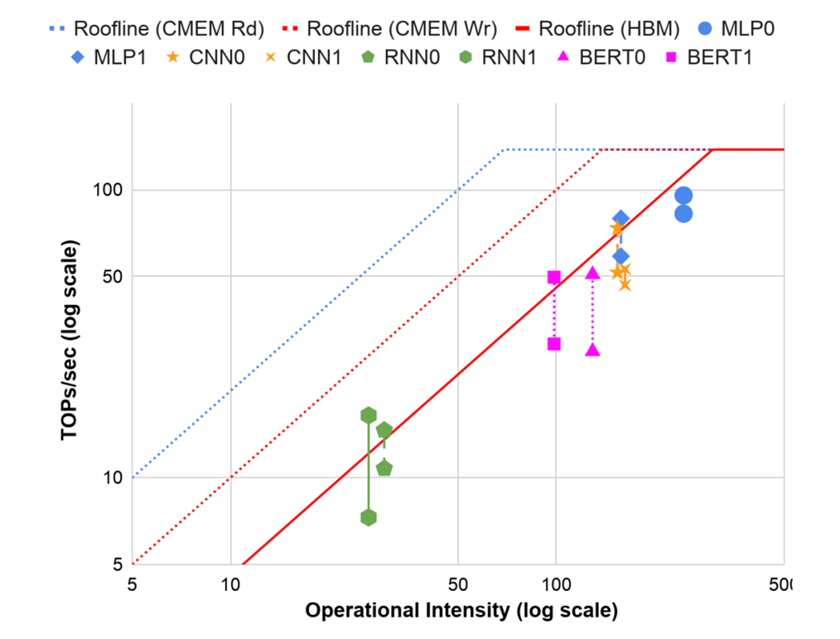

下图是借助 Roofline 模型解释内在原理。将应用程序划分为计算受限或内存受限,使用操作强度来确定应用程序相对于其 Roofline 的位置。

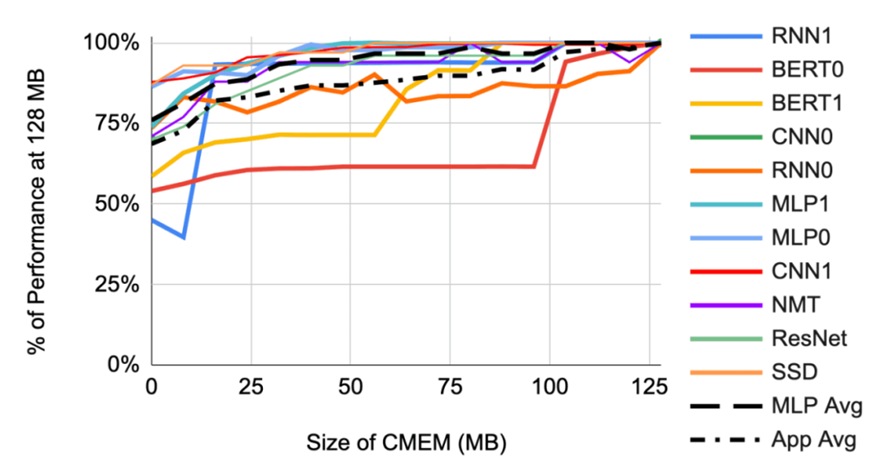

最后,下图展示了小于 128 MB 的 CMEM 对应用程序和 MLPerf 服务基准测试的影响。

谷歌TPU的更多细节

Google最近谈论了将如何致力于推动行业在SoC级别进行创新,并设计了自己的计算引擎,但该公司仍在构建自己的Tensor处理单元(简称TPU),以支持其TensorFlow机器学习框架及其在Google内部驱动应用程序,并为Google Cloud客户提供服务。

如果希望在本周的Google I / O 2021会议上从搜索引擎巨头和机器学习先驱那里获得有关TPUv4架构的重大启示,那么像一样,无疑会非常失望。

在他两个小时的主题演讲中,谷歌首席执行官Sundar Pichai、也是谷歌母公司Alphabet的首席执行官只是简短地谈论了由谷歌设计并可能由台湾制造的TPUv4定制ASIC。顾名思义,TPUv4芯片是Google的第四代Bfloat机器学习处理“野兽”,与主机系统和网络结合在一起,构成了定制的超级计算机。

Pichai在主题演讲中解释说:“这是在Google上部署的最快的系统,对来说是一个历史性的里程碑。” “以前要获得exaflops,需要构建一台定制的超级计算机。但是今天已经部署了许多此类设备。很快数据中心将拥有数十个TPUv4 Pods,其中许多Pods将以90%或接近90%的无碳能源运行。TPUv4 Pods将于今年晚些时候提供给云客户。

看到这种创新步伐,真是太令人兴奋了。”

首先,无论Pichai说什么,当Google在其数据中心中安装TPU Pod来运行自己的AI工作负载并允许其他人使用Google Cloud及其AI平台堆栈运行时,谷歌正在构建的服务绝对是定制的超级计算机。实际上,这是定制超级计算机的定义。

Pichai对于TPUv4架构并没有多说什么,但是可以从他所说的内容中推断出一些东西。

如上图,这会让某些人感到困惑。

如果这只是一个实际的技术演示,Pichai可能会说,由于制程缩小,TPUv4以相同的时钟速度运行的计算单元是原来的两倍,因此每个TPU插槽可以拥有两倍的计算元素-大概是至少两倍的HBM2内存和至少两倍的聚合带宽来平衡。但是Pichai没有说任何话。

但是实际上,这就是认为Google所做的事情。坦率地说,这不是太大的扩展,从技术上讲,如果这是所有谷歌已经完成从TPUv3移动到TPUv4。希望还有更多。

也许有必要进行一些审查,然后将解决“快2倍以上”的意思。前两代TPU和现在推出的TPU是标量/矢量处理器,带有一堆128×128

Bfloat16矩阵数学引擎,一些HBM2内存用于数学单元。

以下图表总结了先前的TPUv2和TPUv3单元以及采用服务器主板:

基本的TPU核心是标量/向量单元-鉴于英特尔,AMD,Power和Arm处理器都具有这些元素的组合,因此如今将其称为CPU-具有Bfloat矩阵数学单元,Google将其称为MXU 。TPU芯片上有两个内核。MXU可以每个时钟处理16384个Bfloat格式的浮点运算,并且使用TPUv2内核可以驱动23 teraflops的Bfloat操作,每个芯片可以达到46 teraflops。

从来不知道时钟速度,但是猜想就像GPU一样在1 GHz以上和2 GHz以下的某个地方。实际上,对TPUv2的猜测是1.37 GHz,而对于TPUv3,猜测约为1.84 GHz。TPUv3的瓦特估算值非常低。认为TPUv2是在20纳米工艺中蚀刻的,而TPUv3是在16纳米或12纳米工艺中蚀刻的,猜测Google已将TPUv4缩小到了7纳米,并且仍然保持在每个socket中450瓦的散热范围内,需要TPUv3 Pods。认为TPUv4没有太多的散热空间可以提高时钟速度。如果照原样,增加的内存可能会将其推到500瓦。

无论如何,借助TPUv3,制程缩减,使Google可以将两个MXU放在标量/矢量单位上,从而使每个内核在恒定频率下的原始性能提高了一倍;怀疑Google还能提高时钟速度。TPUv3每个芯片有两个内核,并将内存增加了一倍,每个内核高达16 GB的HBM2,而TPUv2芯片则为每个内核8 GB。

因此认为Google已经把TPU推进到7纳米,并且在芯片上获得了四个内核。可能是通过创建单片TPUv4芯片来实现的,或者可能正在尝试使用Chiplet,并创建了将两个或四个小芯片相互链接到一个插槽中的互连。这实际上取决于Socket对延迟敏感的工作负载的程度。因为HBM2内存挂在MXU上,所以只要MXU都具有自己的HBM2控制器,真的认为这没什么大不了的。

因此,如果这样做,并且希望提高TPUv4芯片的良率并降低芯片成本(但要在小芯片封装上付一些钱),将采用四个TPUv3内核并将分成小芯片来制造一个TPUv4 Socket。但看起来Google坚持采用整体设计。

还将尽可能提高功耗。TPUv2为280瓦,而TPUv3则以高达450瓦,以驱动123 teraflops的性能。(从TPUv2到TPUv3的时钟速度提高了33.7%,但为此付出了60.7%的功耗增加,从280瓦增加到450瓦来支付。)

认为TPUv4设备上的HBM内存增加了一倍,但每个内核的HBM2内存可能相同,每个内核为16 GB。每个设备将是64 GB,这很多。(是的,知道Nvidia可以为每台设备提供80 GB的存储空间。)。Google很有可能将其推高到每台设备128 GB或每核32 GB的存储空间。这实际上取决于散热和成本。但是确实知道,谷歌和其他AI研究人员确实希望这些设备上有更多的HBM2内存。认为TPUv4器件的时钟速度极不可能提高很多。谁想要600瓦的零件?

现在,让谈谈上面的“快2倍以上”的评论。去年7月,Google发布了一些早期数据,将MLPerf AI基准套件上的TPUv4性能与TPUv3设备进行了比较。看一看:

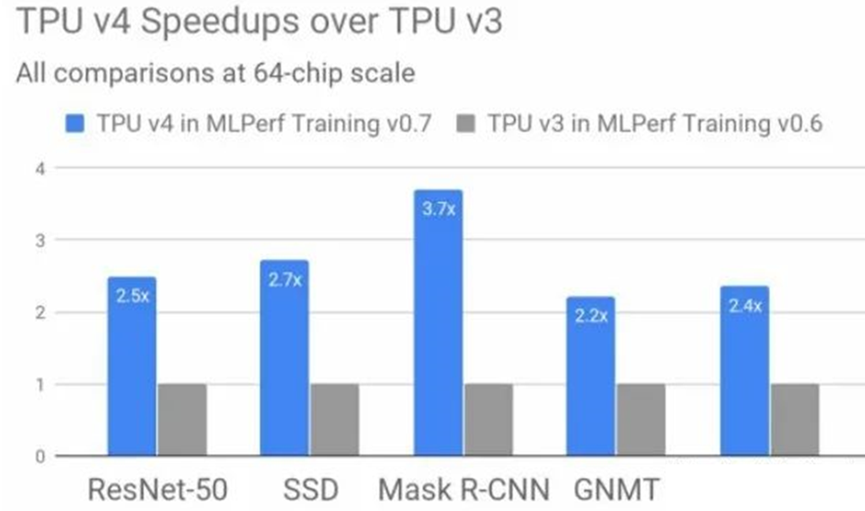

在MLPerf机器学习培训基准测试的各个组件上,从具有64个芯片(128核)的TPUv3机器到也具有64个芯片(和128核)的TPUv4机器,其性能提高范围从2.2倍至3.7倍,平均约为2.7倍对于这五个测试。因此,这可能是Pichai所说的“快2倍以上”。但这不是他的图表所显示的。2X硬件峰值性能容量和MLPerf性能平均提高2.7X之间的差异是-可以猜到-软件优化。

TPU Pods几乎按照以下方式设计而成。这是TPUv2 Pod:

这是TPUv3 Pod:

最大的TPUv2映像是512核心和4 TB的HBM2内存,最大的TPUv3映像是2,048核心和32 TB的内存。

现在,Pichai说TPUv4

Pod将具有“ 4,096芯片”,并且假设他不是核心,那可能意味着具有4,096个插槽,每个插槽都具有单片芯片。这与Pichai所说的相符,并以Bfloat16精度使TPUv4 pod达到了1 exaflops以上。(相比之下,TPUv2 Pods只能扩展到256芯片和11.8 petaflops,而TPUv3 Pods只能扩展到1,024芯片和125.9 petaflops。)1 exaflops假定TPUv4插槽的时钟速度和散热量大致相同。TPUv3套接字和Google将socket增加了三倍。

还认为,TPU实例将能够在单个系统映像中扩展所有4,096个芯片和插槽,并具有至少64 TB的聚合HBM2内存。而且由于软件的改进,更多的峰值性能将推动工作量。将在Google实际告诉更多信息时看到多少。

最后一件事:Pichai还表示,TPUv4 Plds具有“每个芯片的互连带宽在规模上是其他任何网络技术的10倍”。与上图中的TPUv3卡相比,在查看TPUv4服务器卡时,看起来每个TPUv4插槽都有自己的网络接口。TPUv3卡有四个共享两个互连的插槽。(或者,看起来像那样。不确定这是正确的。那些可能是两端口路由器芯片。)。

Google TPU内部原理

搜索、街景、照片、翻译,这些Google提供的服务,都使用了Google的TPU(张量处理器)来加速背后的神经网络计算。

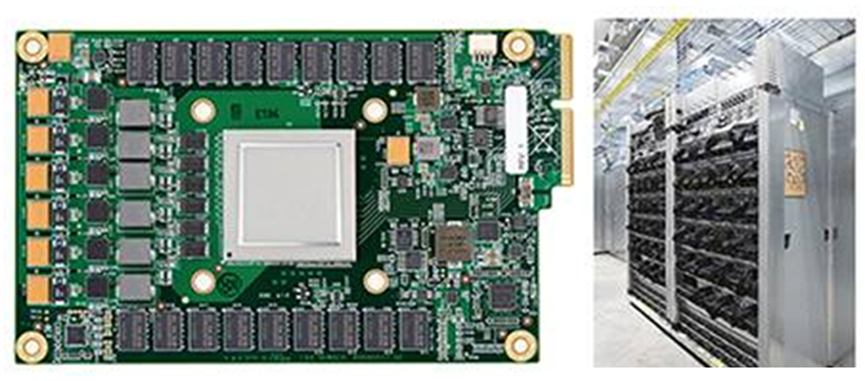

△ 在PCB板上的Google首款TPU和部署了TPU的数据中心

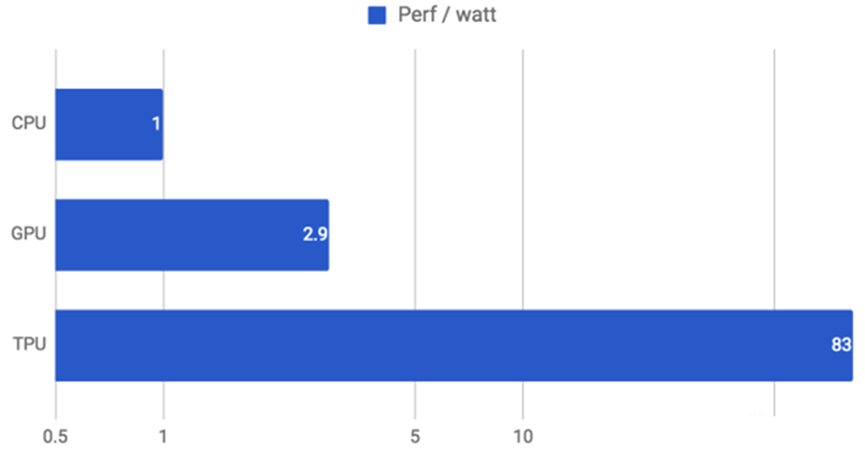

去年Google推出TPU并在近期对这一芯片的性能和架构进行了详细的研究。简单的结论是:TPU与同期的CPU和GPU相比,可以提供15-30倍的性能提升,以及30-80倍的效率(性能/瓦特)提升。

这意味着,Google的服务既可以大规模运行于最先进的神经网络,而且可以把成本控制在可接受的程度上。以下的内容,将深入解读Google TPU中的技术,并且讨论如何实现更为出色的性能。

通往TPU之路

早在2006年,Google就在考虑为神经网络构建一个专用集成电路(ASIC)。2013年这个需求变得更加紧迫,当时Google意识到快速增长的计算需求,可能意味着数据中心的数量需要翻番才能满足。

通常而言,ASIC的开发需要耗时数年。但具体到TPU而言,从设计到验证、构建和部署到数据中心里,只需要15个月。

TPU ASIC采用了28nm工艺制造,主频700MHz,功耗40W。为了尽快把TPU部署到现有的服务器中,Google选择把这个芯片打包成外部扩展加速器,然后插到SATA硬盘插槽里使用。所以TPU通过PCIe Gen3 x16总线与主机相连,也就是说12.5GB/s的有效带宽。

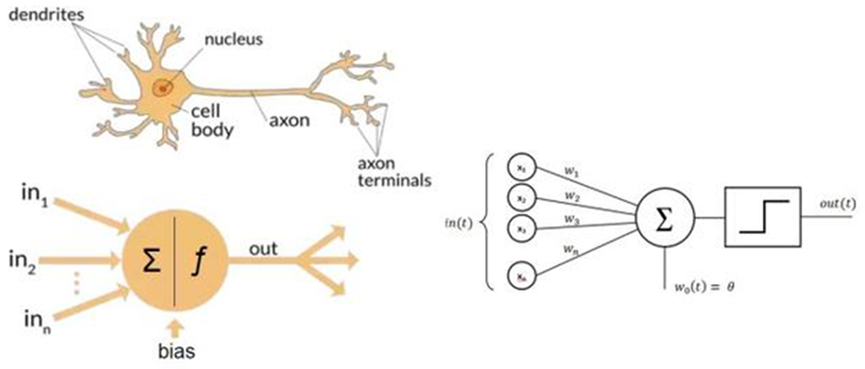

用神经网络预测

要说明TPU的设计思路,需要先来简介一下神经网络的计算。

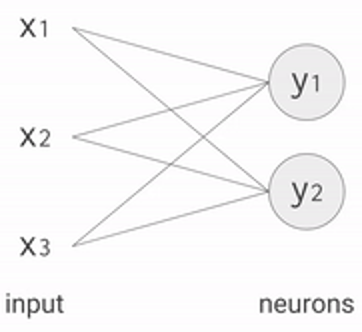

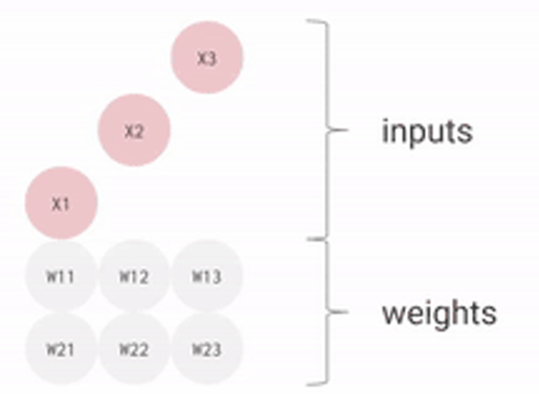

这是一个TensorFlow Playground的例子。用以训练一个神经网络,以标签对数据进行分类,或者对缺失数据进行估计,或者推断未来的数据。对于推断来说,神经网络中的每个神经元都进行如下计算:

- 输入数据(x)乘以权重(w)以表示信号强度

- 乘积加总,成为代表神经元状态的唯一值

- 应用激活函数(f),例如ReLU、Sigmoid等调节神经元

△ 神经网络把输入数据与权重矩阵相乘,并输入激活函数

例如,对于有三个输入数据和两个全连接神经元的单层神经网络而言,需要把输入和权重进行六次相乘,并得出两组乘积之和。这个乘法和加法序列,可以写成一个矩阵乘法,然后通过激活函数进一步处理矩阵的输出。

在更复杂的神经网络架构中,乘法矩阵通常也是计算量最大的部分。

实际业务中需要多少次乘法运算?2016年7月,Google团队调查了实际业务中,六个有代表性的神经网络应用,结果如下表所示:

如上表所示,每个神经网络中的权重数量从500万到1亿不等。每一个预测,都需要许多步的输入数据和权重矩阵相乘,并输入到激活函数中。

总而言之,计算量超大。作为优化的第一步,Google应用了一种称为量化的技术进行整数运算,而不是在CPU或者GPU上对所有数学工作进行32位或者16位浮点运算。这能减少所需的内存容量和计算资源。

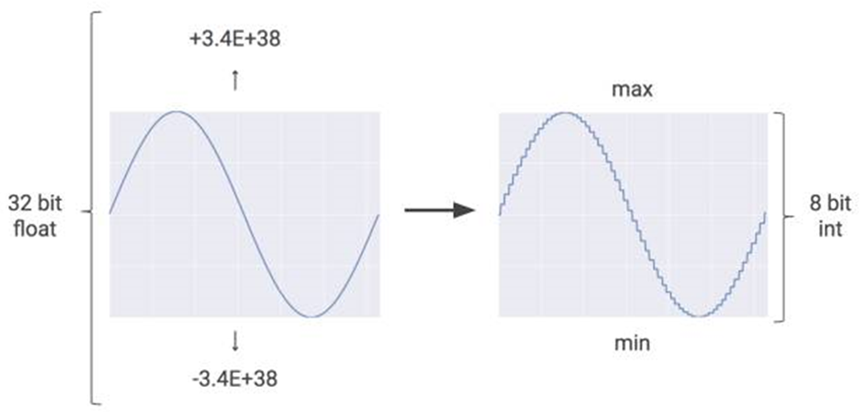

神经网络中的量化

通常而言,神经网络的预测不需要32位或16浮点计算精度,通过一些方法,可以用8位整数对神经网络进行预测,并保持适当的准确度。

所谓量化,就是一种使用8位整数来近似预设的最小值和最大值之间任意数值的优化技术。

△ TensorFlow中的量化

量化是降低神经网络预测成本的利器,同时带来的内存减少也很重要,特别是对于移动和嵌入式部署。举个例子,在Inception中应用量化之后,这个图像识别模型能从91MB压缩到23MB,成功瘦身四分之三。

使用整数而不是浮点计算,大大减小了TPU的硬件尺寸和功耗。一个TPU钟包含65,536个8位整数乘法器。云环境中使用的主流GPU,通常包含数千个32位浮点乘法器。只要能用8位满足精度需求,就能带来25倍以上的性能提升。

RISC,CISC和TPU指令集

可编程性是TPU的另一个重要设计目标。TPU不是设计用来运行某一种神经网络,而是要能加速许多不同类型的模型。

大多数当代CPU都采用了精简指令集(RISC)。但Google选择复杂指令集(CISC)作为TPU指令集的基础,这一指令集侧重于运行更复杂的任务。

来看看TPU的结构图。

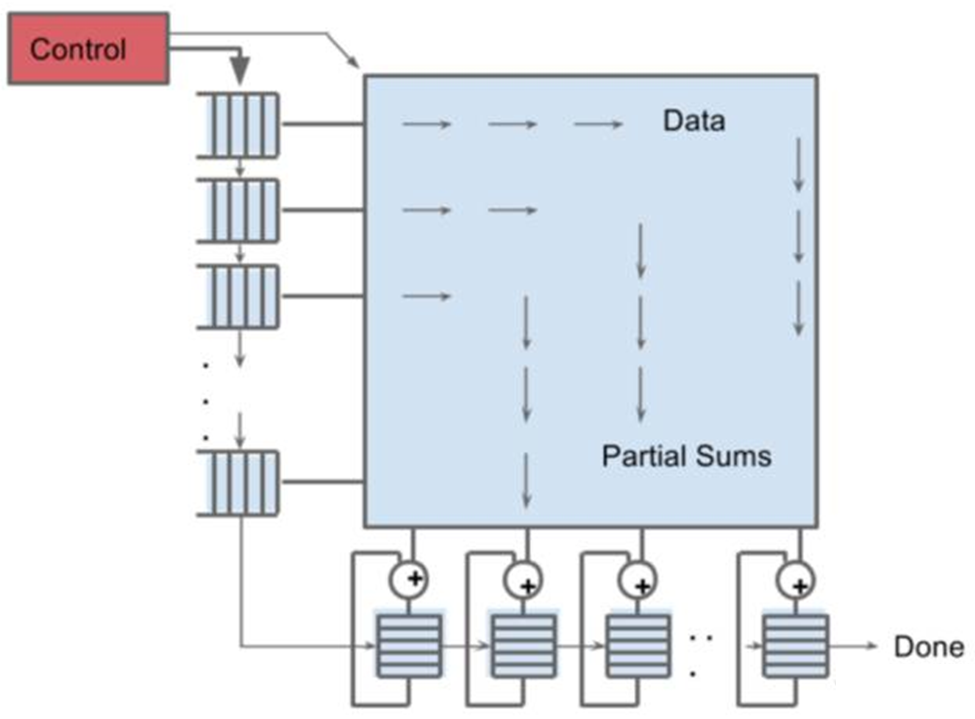

TPU包括以下计算资源:

- 矩阵乘法单元(MUX):65,536个8位乘法和加法单元,运行矩阵计算

- 统一缓冲(UB):作为寄存器工作的24MB容量SRAM

- 激活单元(AU):硬件连接的激活函数

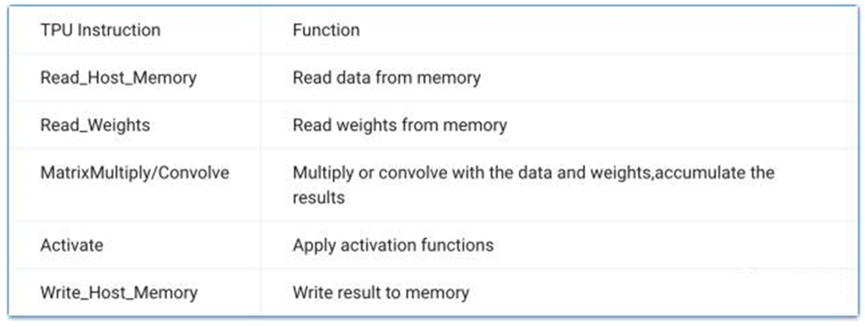

为了控制MUX、UB和AU进行计算,Google定义了十几个专门为神经网络推理而设计的高级指令。以下是五个例子。

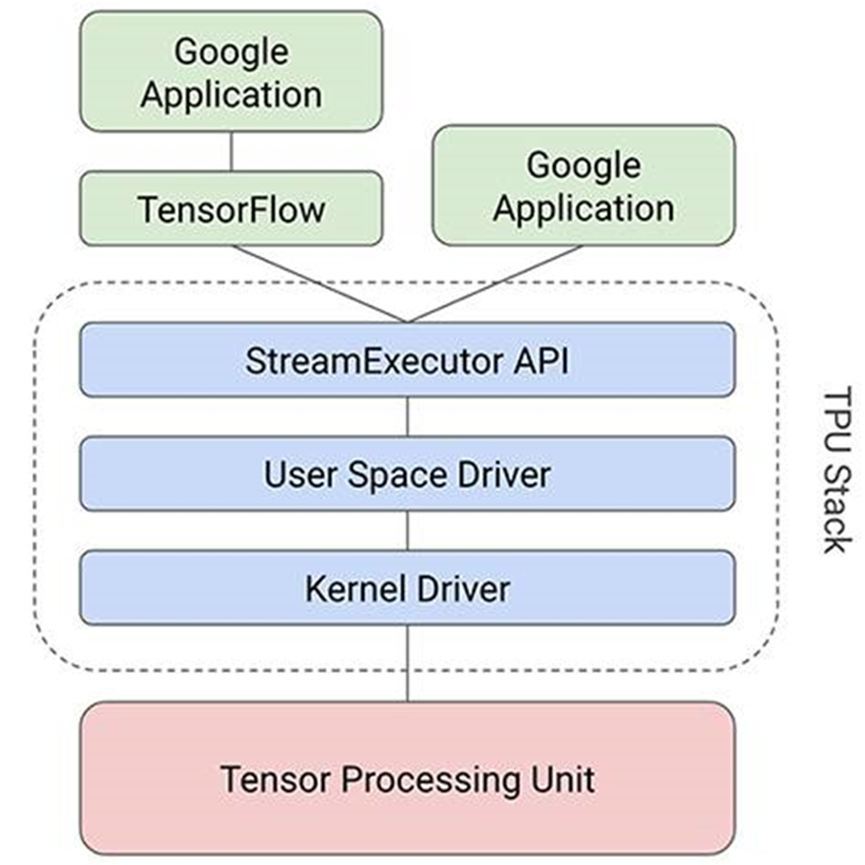

简而言之,TPU设计封装了神经网络计算的本质,可以针对各种神经网络模型进行编程。为了编程,Google还创建了一个编译器和软件栈,将来自TensorFlow图的API调用,转化成TPU指令。

△ 从TensorFlow到TPU:软件堆栈

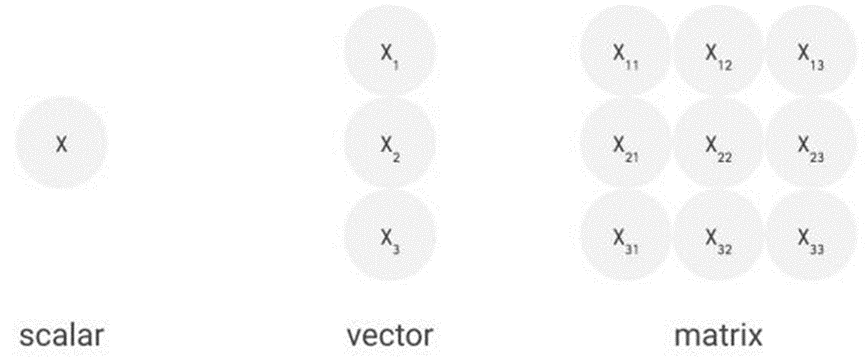

矩阵乘法单元的并行计算

典型的RISC处理器提供简单计算的指令,例如乘法或加法。这些事所谓的标量(Scalar)处理器,因为每个指令处理单一运算,即标量运算。

即使主频千兆赫兹的CPU,仍然需要很长时间才能通过一系列标量运算来完成大型矩阵的计算。改进的方法就是矢量(Vector)运算,同时针对多个数据元素执行相同的操作。

GPU的流处理器(SM)就是一种高效的向量处理器,赞单个时钟周期内,可以处理数百到数千次运算。

至于TPU,Google为其设计了MXU作为矩阵处理器,可以在单个时钟周期内处理数十万次运算,也就是矩阵(Matrix)运算。

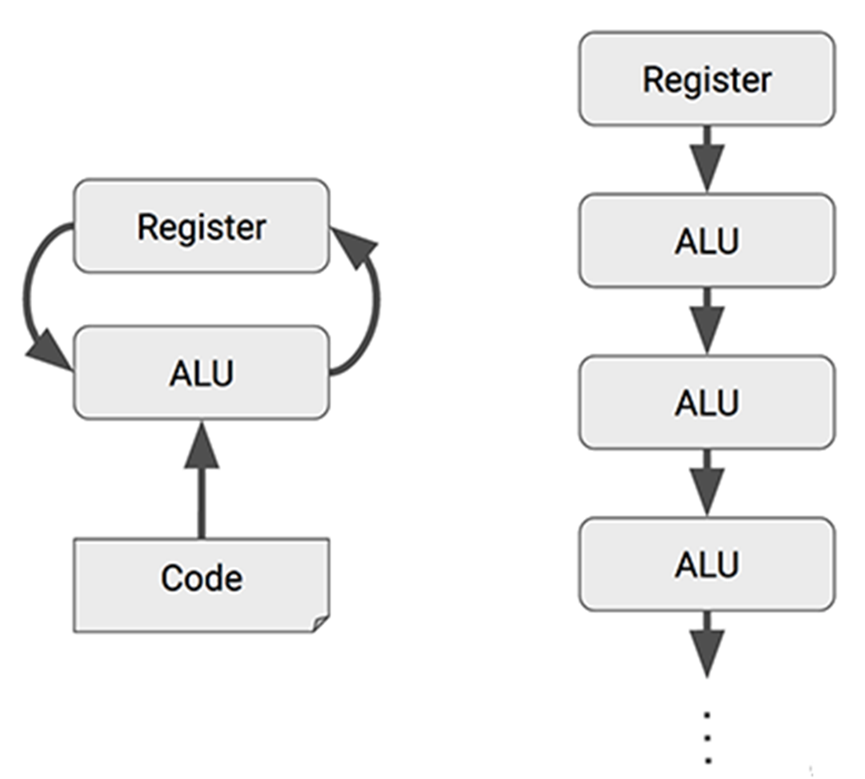

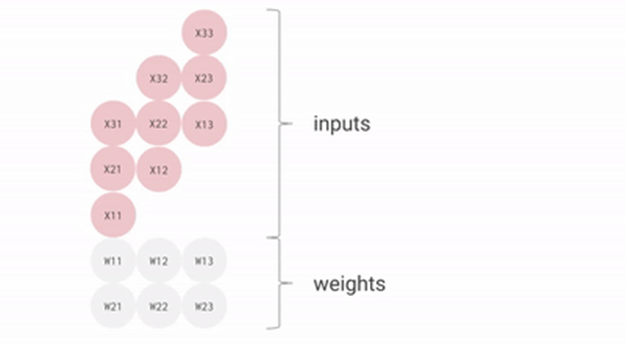

TPU的核心:脉动阵列

MXU有着与传统CPU、GPU截然不同的架构,称为脉动阵列(systolic array)。之所以叫“脉动”,是因为在这种结构中,数据一波一波地流过芯片,与心脏跳动供血的方式类似。

如图所示,CPU和GPU在每次运算中都需要从多个寄存器(register)中进行存取;而TPU的脉动阵列将多个运算逻辑单元(ALU)串联在一起,复用从一个寄存器中读取的结果。

MXU中的权值阵列专门为矩阵乘法运算进行了优化,并不适用于通用计算。

△ 脉动阵列中,输入向量与权值矩阵相乘

△ 脉动阵列中,输入矩阵与权值矩阵相乘

MXU的脉动阵列包含256 × 256 = 65,536个ALU,也就是说TPU每个周期可以处理65,536次8位整数的乘法和加法。

TPU以700兆赫兹的功率运行,也就是说,每秒可以运行65,536 × 700,000,000 = 46 × 1012次乘法和加法运算,或每秒92万亿(92 × 1012)次矩阵单元中的运算。

△ TPU中的MXU

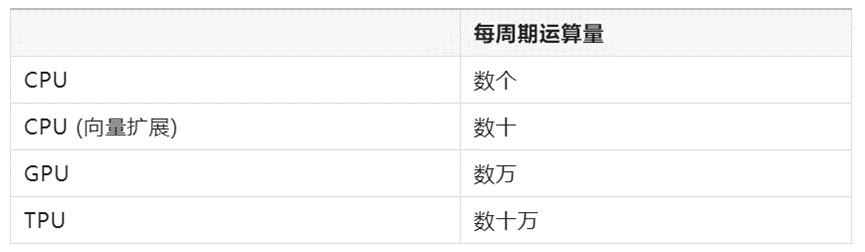

对CPU、GPU和TPU的每周期算术运算量进行一下对比:

这种基于复杂指令集计算(CISC)的矩阵运算设计,实现了出色的性能功耗比:TPU的性能功耗比,比同时期的CPU强83倍,比同时期的GPU强29倍。

极简&确定性的设计

极简这一点,在Google之前发布的TPU论文第8页提到过。与CPU和GPU相比,单用途的TPU就是一个单线程芯片,不需要考虑缓存、分支预测、多道处理等问题。

TPU的设计之简洁,从冲模平面图上就能看出来:

△ 黄色代表运算单元;蓝色是数据单元;绿色是I/O,红色是控制逻辑单元。

与CPU和GPU相比,TPU的控制单元更小,更容易设计,面积只占了整个冲模的2%,给片上存储器和运算单元留下了更大的空间。而且,TPU的大小只有其他芯片的一半。硅片越小,成本越低,良品率也越高。

而确定性,是单用途带来的另一个优势。CPU和GPU需要考虑各种任务上的性能优化,因此会有越来越复杂的机制,带来的副作用就是这些处理器的行为非常难以预测。

而用TPU,能轻易预测运行一个神经网络、得出预测,需要多长时间,这样,能让芯片以吞吐量接近峰值的状态运行,同时严格控制延迟。

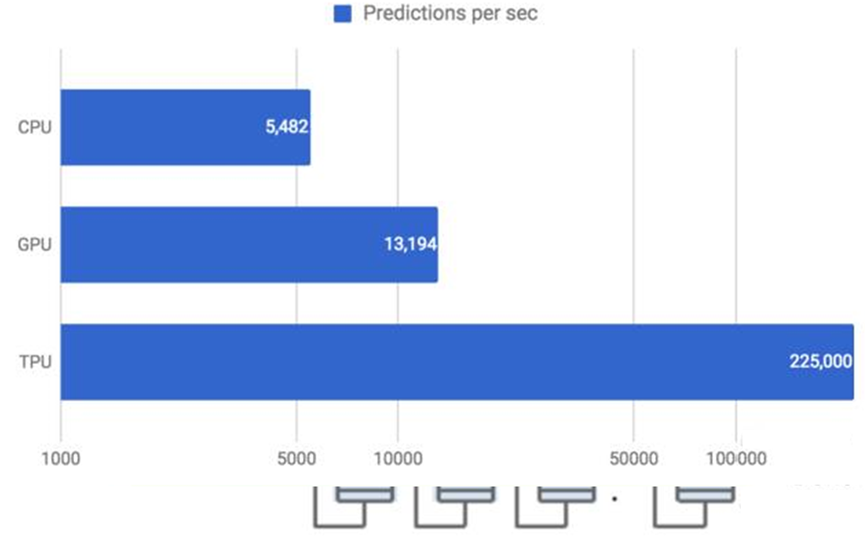

以上面提到的MLP0为例,在同样将延迟控制在7毫秒之内的情况下,TPU的吞吐量是CPU和GPU的15到30倍。

△ 各种处理器上每秒可运行的MLP0预测

下面,是TPU、CPU、GPU在六种神经网络上的性能对比。在CNN1上,TPU性能最为惊人,达到了CPU的71倍。

总结

如上文所述,TPU性能强劲的秘诀,是因为专注于神经网络推断。这使得量化选择、CISC指令集、矩阵处理器和最小设计都成为可能。

神经网络正推动计算模式的转变,Google预计未来几年中,TPU将成为快速、智能和价格实惠的重要芯片。

参考文献链接

https://baijiahao.baidu.com/s?id=1706639922409916892&wfr=spider&for=pc

https://www.nextplatform.com/2022/05/11/google-stands-up-exascale-tpuv4-pods-on-the-cloud/

https://mp.weixin.qq.com/s/sOPhPJhhniMTIlZX3HaSUA

https://mp.weixin.qq.com/s/e8zOrmiIidy8IoV1yMfdKg

https://mp.weixin.qq.com/s/VEDxfx3il-d_zMPCSntsVg

https://mp.weixin.qq.com/s/305V7bDTJb8jOInz9l_xTA