Zynq Book摘抄

Zynq Book

PART A 开始了解 Zynq

- P21 Zynq-7000 是特地使用了ARM Cortex-A9 的r3p0 版本的,那是基于ARMv7-A 架构的。

- P57 另一种强大的硬件调试方法被称为硬件环路测试(HIL)。使用这种方式,部分设计在开发板上运行的同时,信号可被返回到仿真环境进行观察。例如,Xilinx 提供一个教程,教程中PS 端在板子上运行,而PL 组件则在仿真器中运行。这为在真实PS 环境下详细观察PL 信号提供了机会。

- P58 Zynq设计的软硬层次

- P59 需要注意的是并不是所有的设计都同时需要可执行链接格式(ELF,.elf)的文件和比特流(BIT,.bit)文件来配设备的。ELF 文件的作用是烧写PS,而BIT 文件的作用则是烧写PL。因此如果只使用了Zynq 中的一种设备(PS 或者PL),那么就只需要相应地烧写文件。

- P61 另一个潜在的难点是在进程中可能发生的对设计做重新划分的需求,比如说,在软件团队发现有一个功能比预期的要更加依赖于计算,非常适合于硬件加速。Vivado 设计套件的一个好处就在与它的Vivado HLS 工具可以将C 语言高级综合为硬件,这意味着可以很快地基于现有的C 代码将软件程序转化为硬件,而不需要去开发一个硬件协处理器。

- P63 最后关于Vivado 的重要的一点就是,尽管在本书中我们主要使用带有GUI 特性的工具,所有的这些设计工作同样也可以使用工业标准的Tool CommandLanguage(TCL) 脚本语言来完成。这是一种使用设计工具过程中非常强大的、可重现的、参数化的方法。

- P80 MicroBlaze 是一个主要的软处理器类型,在Xilinx 的ISE 和Vivado 的大多数新版本的设计流中都支持。如果需要,单个芯片上可以部署多个MicroBlaze。

- P81 MicroBlaze 的资源使用是随配置而变化的,从“ 最小面积” 类型的大约900个LUT、700 个FF 和2 个RAM 块,到“ 最大性能” 配置的大约3800 个LUT、3200个FF、6个DSP48E1和21个RAM块。

- P82 典型的MicroBlaze 配置可能达到PL 的最高频率的70% 左右,也就是最高等于200MHz 到300MHz —— 对比之下ARM 处理器的最高工作频率是800MHz 到1GHz。

- P84 MicroBlaze 对于很多应用还是非常恰当的选择。单就Zynq 而言,MicroBlaze 可以成为ARM 处理器有用的“ 副官”。

- P85 PicoBlaze 的设计可以直接从Xilinx 网站下载得到,文件包里包括PicoBlaze 控制器的核心VHDL 和Verilog,加上可选的功能,比如UART 和SPI接口。作为一个8 位的控制器,PicoBlaze 的功能是有限的,也无法与一个Zynq 的ARM 处理器相提并论。不过,PicoBlaze 的实现可以在Kintex-7 的逻辑片上运行到超过200MHz,大多数情况下和它可能要控制的逻辑部分一样快[4]。

- P93 把计算卸载到协处理器

- P95 ZYNQ对比FPGA-处理器组合的优势

- P115 机器对机器(Machine-to-Machine,M2M)通信,即具有独立功能的网络化结点(不需要人为干涉);以及物联网(Internet of Things,IoT),即由这样的结点组成的网络的一个集合名词。

- P116 连续的视频帧往往存在高度的重合。可以用算法来发送一小段时间片段内完整的、最新的帧,然后在这些帧之间,对帧与帧之间的不同进行编码。

- P154 OpenCL (Open Computing Language,开放计算语言)是一个开发标准,给出了在异构的计算机单元上运行软件的框架[15]。一个单元组可以由中央处理单元(Central Processing Units,CPU)、DSP、图像处理单元(Graphics Processing Units,GPU)、FPGA 和其他类型的计算资源以任意方式组合而成。OpenCL 靠一个宿主处理器来控制系统中其他处理单元的执行,因此Zynq 是特别适合OpenCL 的平台:一个ARM 核可以实现宿主控制,将功能分配到(一)在FPGA 中定制的处理单元,及(二)第二个ARM 核中。

- P157 DPR 是一种对FPGA 或Zynq 的PL的某个区域实现重新编程,而芯片的其他部分能继续不受影响工作的技术。用基于ARM 的软件控制做的DPR 的实现(以及用于可进化硬件的相关技术)是非常受关注的领域

PART B Zynq SoC & 硬件设计

-

P184 硬件中断可以进一步被分类为以下几种类型:

• 可屏蔽中断(Maskable Interrupts,IRQ)

• 不可屏蔽中断(Non-Maskable Interrupts,NMI)

• 处理器间中断(Inter-Processor Interrupts,IPI) -

P185 在较小的嵌入式系统设计中,系统总线可能是设计中唯一出现的总线。在较大的、多总线的设计中,系统总线会是连接存储器控制器和处理器,及任何高速设备之间具有最大带宽的总线。剩下的不需要这么高的处理器访问速度的外设和存储器控制器,会通过外设总线连接。

-

P192 Zynq 里的PS 和PL 部分之间的主要连接形式是AXI 接口,它在芯片的这两个部分之间实现了高带宽、低延迟的连接。

-

P203 对PS 和PL 的共享存储器的共享访问是通过多端口DDRI 来支持的,它具有四个AXI 从机端口来满足这个要求[9]:

• PL 通过两个专用的64 位端口(AXI_HP)来访问。

• 一个64 位端口通过L2 cache 控制器专用于ARM CPU。这个端口可以被配置为低延迟。

• 所有其他AXI 主机通过中央互联共享剩下的端口。 -

P222 FPGA 实现的例子应用包括数字过滤计算、波束形成和图像处理。传统上这些任务是重复的,而且计算的过程本质上是完全静态的。另一方面,存在一些更动态、不可预测的问题,这些任务更适合在基于处理器的系统上实现。

-

P224 用剖析可以识别出代码执行中可能造成的瓶颈的低效率代码,也能找到函数与PL 中的模块或软件中其他函数之间的糟糕的交互通信。还可能发现某个算法或例程可能本质上更适合在硬件中实现。一旦被识别出来,可以重写原始的软件函数来优化瓶颈问题,或把它转移到PL 来加速。

-

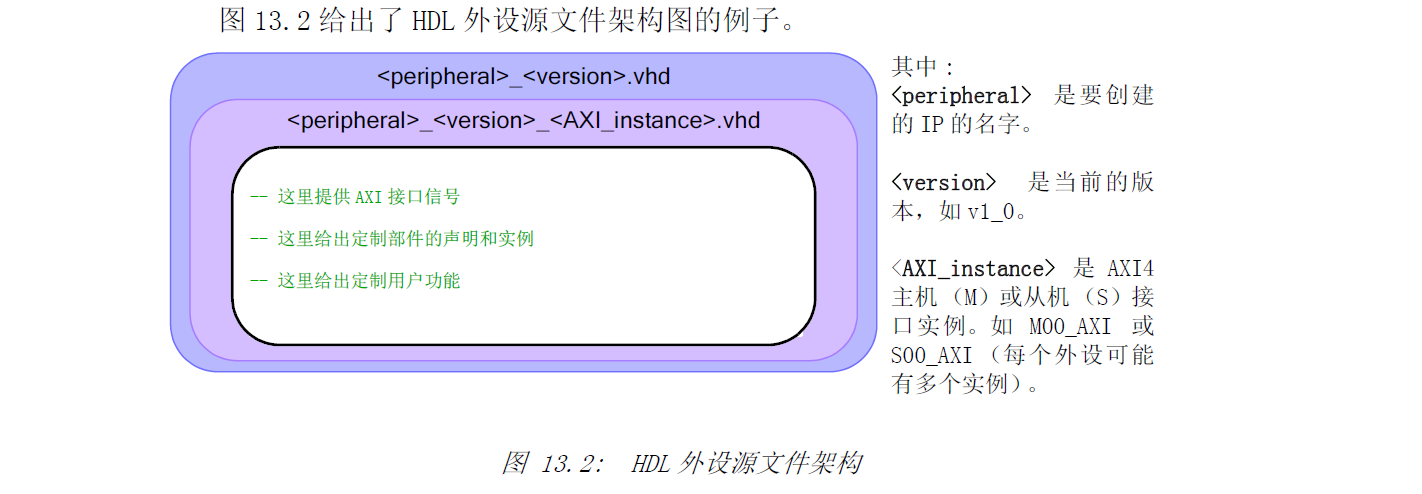

P240 用HDL 设计要通过AXI 接口通信的IP 核的时候,必须要严格遵循Xilinx IP Packager 的外设信号命名规范。一个IP 核的顶层HDL 文件定义了设计接口,并列出了总线接口上的默认连接和端口。它还列出了所有的通用变量,并指定了默认值。

-

P241 System Generator 为IP 设计提供了有用的环境,IP 包可以连接起来快捷方便地做出设计来。它提供了大量的IP 包,从简单的算术运算到复杂的DSP 运算都有。

-

P241 HDL Coder 是一个MathWorks 做的工具,能以MATLAB 函数和Simulink 模型来产生可综合的HDL 代码(VHDL 和Verilog 格式都可以)。它的工作流会分析MATLAB/Simulink 模型,然后自动把这个系统从浮点转换成定点,从而实现高层抽象。这样用户就可以专注于开发算法和模型,而不必操心错综复杂的HDL 设计。

-

P242 Vivado HLS 是Xilinx 提供的一个工具,是Vivado Design Suite 的一部分,能把基于C 的设计(C、C++ 或SystemC)转换成在Xilinx 全可编程芯片上实现用的RTL 设计文件(VHDL/Verilog 或SystemC)。

-

P288 c语言数据类型及其对应的位数和范围。

-

P290 HSL可以定义任意精度/位数的数据类型。

-

P346 IP-XACT 完全不会去描述IP 的硬件功能,而是描述它的接口。因此它不是用来代替像VHDL 或Verilog 这样的RTL 语言,也不是代替嵌入式软件或文档的,而是作为那些东西的补充:一个IP-XACT 部件给出了这个IP 的关键数据。IP-XACT 的标准化解决了IP 重用的很多问题,并使得系统集成变得容易,还能在IP 之间做自动的连接。

PART C 操作系统& 系统集成

-

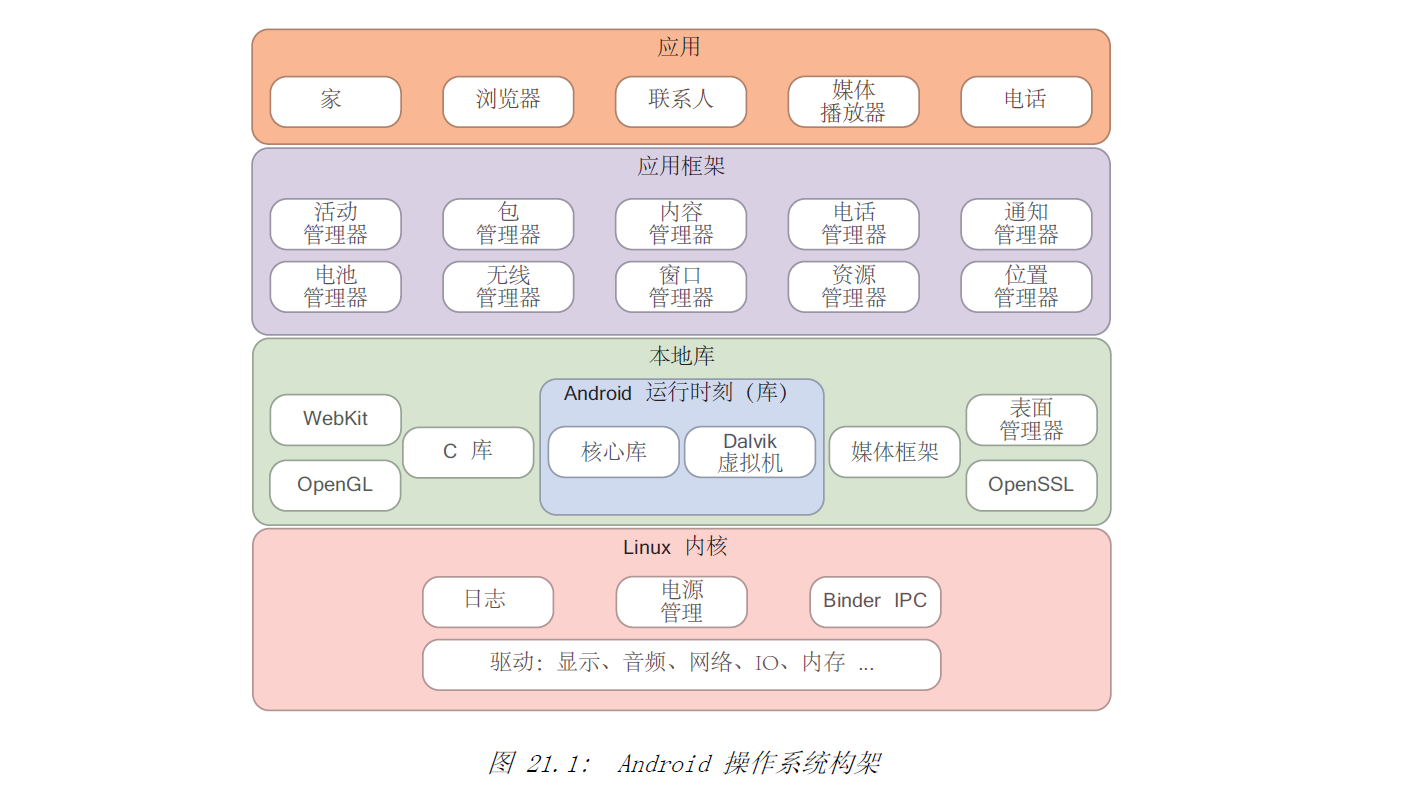

P376 安卓操作系统构架

-

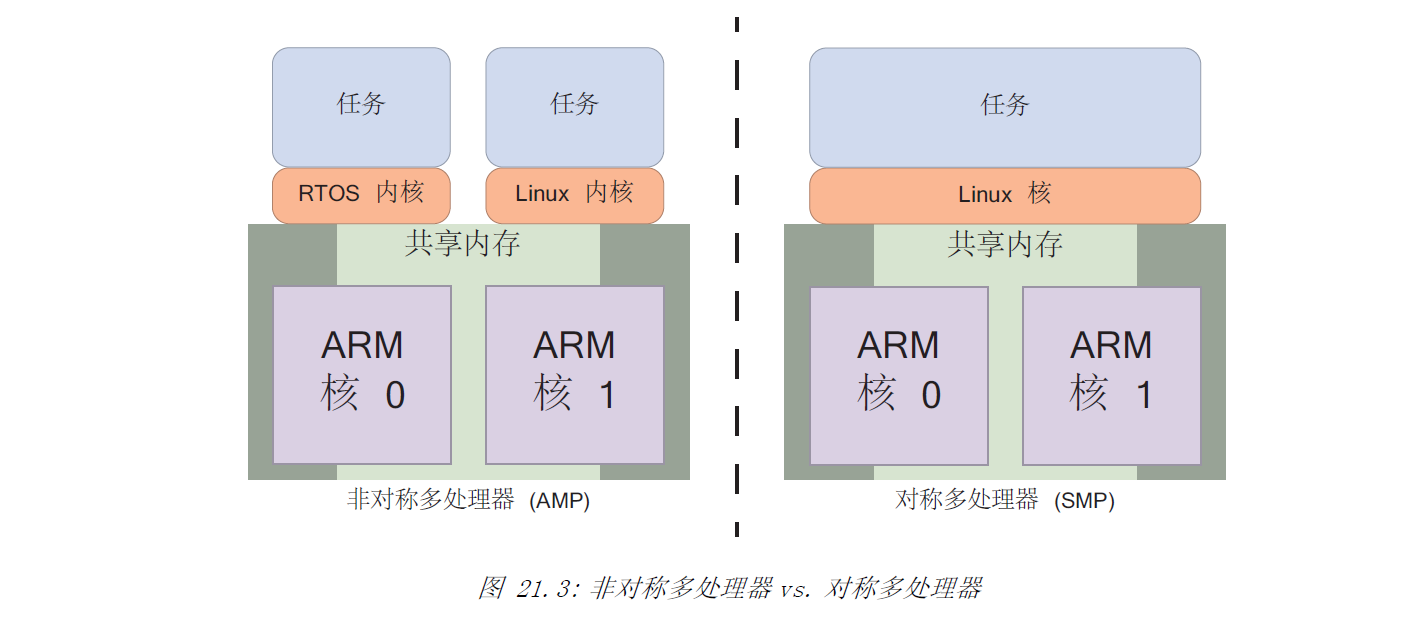

P378 从操作系统支持的角度介绍了非对称多处理器(AMP)和对称多处理器(SMP)这两个术语。不过,从系统架构的角度理解这两者的定义也是有用的。非对称多处理器可以用于要使用多个CPU 核的系统上,这些CPU 核可能是异构的。每个CPU 或CPU 核,可以运行自己的操作系统实例,这些操作系统可以是相同的,也可以是完全不同的。这样做的一个例子是在一个CPU 上运行一个RTOS 的系统,而另一个CPU 上运行一个基于Linux 的GUI。CPU 核之间的通信是利用共享内存进行的,共享内存实现了某种程度上的软件抽象。另一方面,对称多处理器需要系统中所有的CPU 是完全相同的架构的。所有的CPU 上运行了单个操作系统实例,这个操作系统把进程任务分派到各个CPU 上,并加以协调。和AMP 一样,在CPU 之间用共享内存来做通信,以及做任务执行的协调。

-

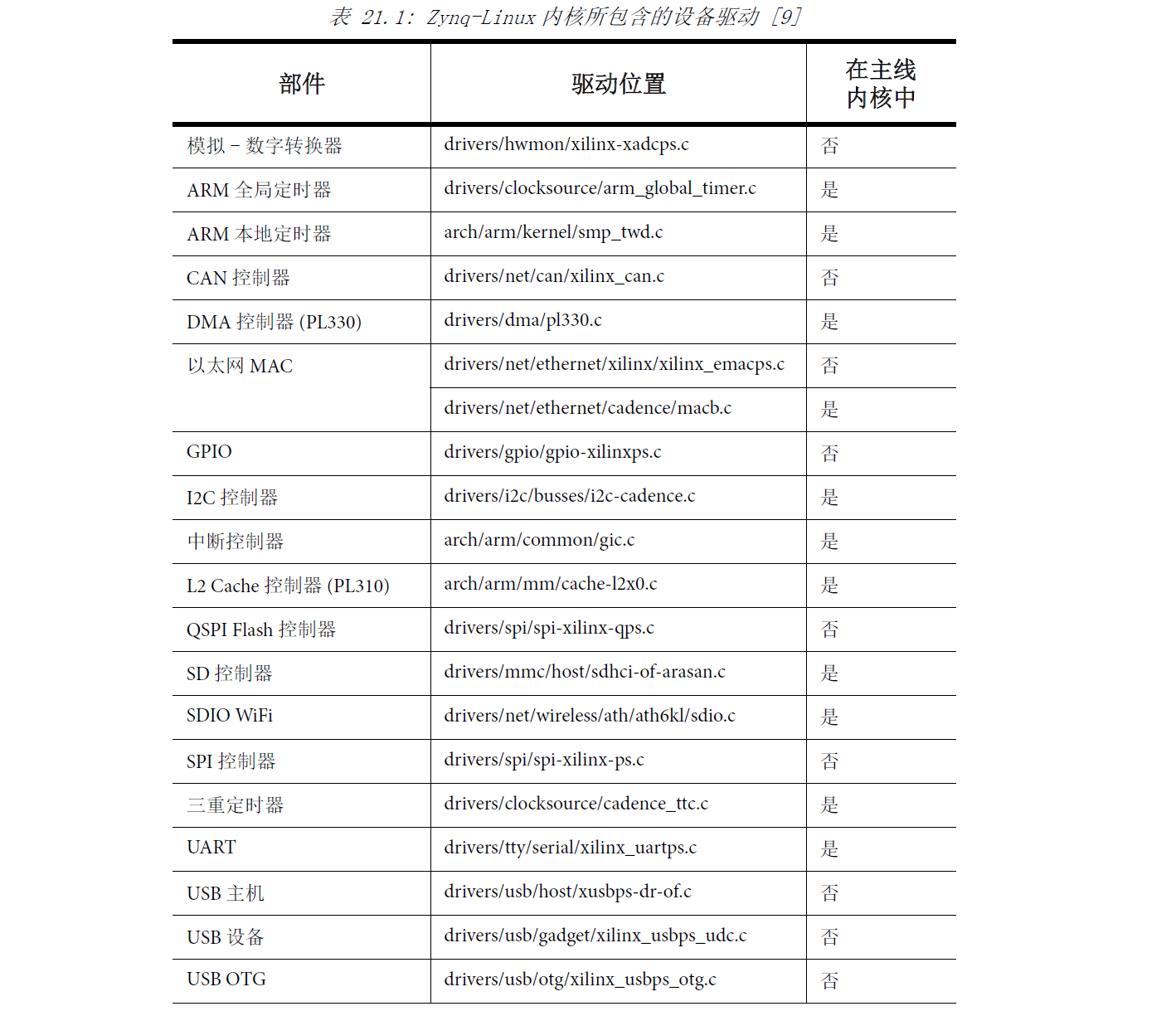

P380 Zynq-Linux 是一个开源的操作系统,由Xilinx 免费提供。它基于kernel.org上的3.0 Linux 内核,包含了一些Xilinx 增加的内容,比如BSP 和特定的设备驱动。表21.1 给出了所包含的设备驱动的列表[9]。

-

P381 Xillinux 是一款Linux 桌面发行版,可以在Zedboard 上运行一个完整的图形桌面环境,键盘和鼠标可以接在Zedboard 上的USB OTG 端口,显示器可以接在板上的VGA 端口上[7]。除了一个完整的Linux 发布版本,Xillybus 还提供了在Linux主机和运行在可编程逻辑上的外设之间交互的开发包。在逻辑这边是以FIFO 的形式实现的,而在主机这边就是标准的Linux 文件操作。这个Linux 发行版本是基于Ubuntu 12.04 长效支持(LTS)的,它和开发包从Xillybus 网站可以免费下载[7]。

-

P382 FreeRTOS 是一个轻量级的实时操作系统,可以用于很多种器件和处理器架构上。FreeRTOS 内核的核心只是由3 个C 语言文件构成,所以它很简单,具有最小的ROM、RAM 和处理器的额外开销,很多情况下内核映像只有4 到9kB[5]。Xilinx 提供了一个已经做好的FreeRTOS 版本,在FreeRTOS 的网站可以免费下载[5]。

-

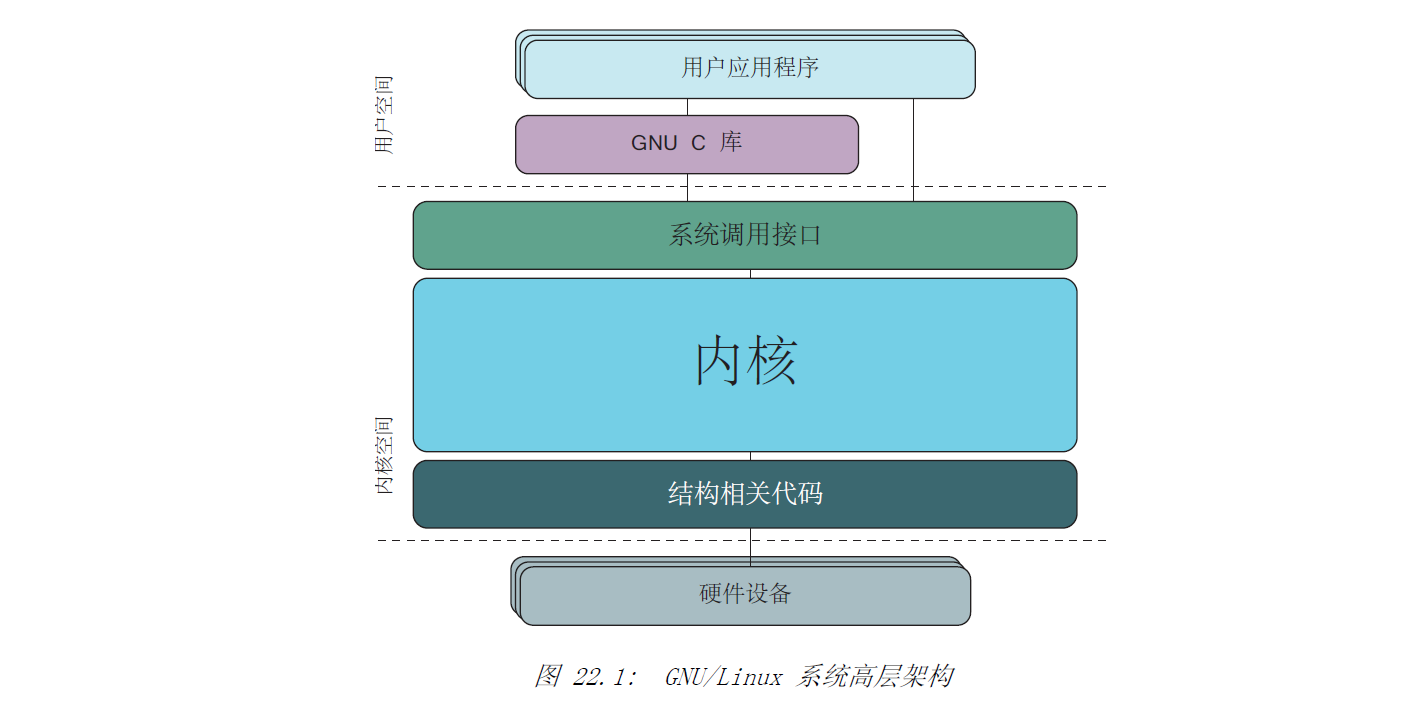

P386 22.2. Linux 系统概述图22.1 是一个GNU/Linux 系统的通用高层架构。实际上,这个内核空间是一个

复杂得多的概念,其中包含了比这里多得多的部件。不过,为了我们行文的需要,此刻先考虑最重要的部分。在内核之上运行的应用与系统程序以及GNU C 库是在用户空间里的。应用指的是具有实际功能的程序,比如文字处理、游戏或开发来运行在Zynq 芯片的处理器上的C 程序。而系统程序是实现各种操作系统服务所必须的!这些操作系统服务保证了系统能确实工作。物理硬件位于链条相反的一侧,经由内核空间从用户层级抽象出来,包括如整个存储系统、开发板上的网卡或GPIO 等。用户层和硬件只能间接访问的这种设计实现了安全性,因为它以使用内核工具的方式确保了访问的规则[3]。系统调用接口(SCI)提供了从用户空间调用系统的内核功能。前面讨论过,Linux 内核构成了操作系统的心脏,提供了一组工具,使得用户空间可以与硬件交互。Linux 内核本身可以被划分成它自己的分层子系统,比如内存和进程管理、虚拟文件系统和设备驱动。不过,这些会在第23 章深入讲解。内核代码被认为是与体系架构无关的,它的代码对Linux 所支持的所有处理器架构都是通用的。在这之下是架构相关的代码,也就是处理器和平台专用的,这部分一般叫做BSP。

-

P411 主引导记录(Master Boot Record,MBR)—— 就是在那个设备的第一个扇区的那512 字节—— 里面是第一级引导装载程序。第一级引导装载程序FSBL 是MBR 里的一段代码。

-

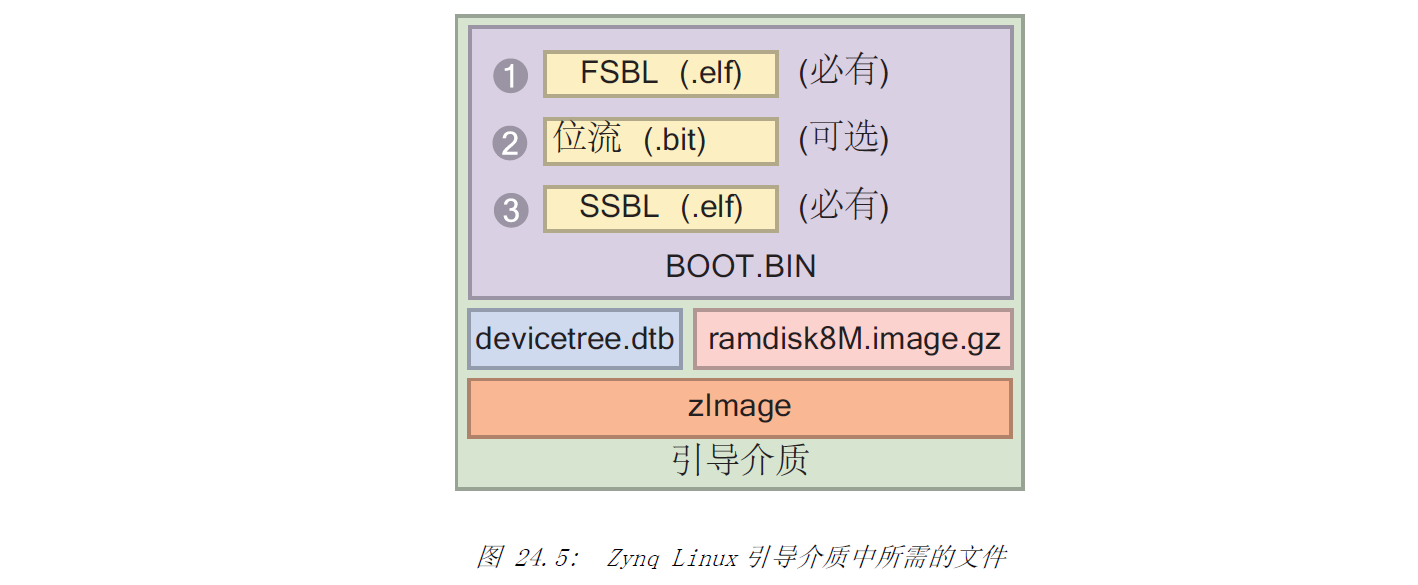

P415 表24.2 详列了Zynq Linux 引导过程中的各个阶段,图24.3 则是这些阶段的图形表示。

-

P417

(BOOT.BIN)是Zynq 引导程序的映像文件。它实际上是两个必不可少的文件,FSBL 和SSBL 的可执行可链接格式(.elf)文件,以及一个可选的位流(.bit)文件。FSBL 和SSBL 文件,恰如其名,是引导装载程序的最后阶段,用来在设备上载入那个Linux 的。位流是用来配置Zynq-7000 AP 设备上的可编程逻辑部分的。zImage文件里是压缩了的Linux内核,一旦被SSBL装载进内存,它会自动解压。Linux 要运行的硬件的数据保存在设备树blob (devicetree.dtd)文件中。最后的那个文件(ramdisk8M.image.gz)是一个RAM 盘映像,载入内存后,使得RAM 的一部分用作像一个磁盘驱动器一样。

(BOOT.BIN)是Zynq 引导程序的映像文件。它实际上是两个必不可少的文件,FSBL 和SSBL 的可执行可链接格式(.elf)文件,以及一个可选的位流(.bit)文件。FSBL 和SSBL 文件,恰如其名,是引导装载程序的最后阶段,用来在设备上载入那个Linux 的。位流是用来配置Zynq-7000 AP 设备上的可编程逻辑部分的。zImage文件里是压缩了的Linux内核,一旦被SSBL装载进内存,它会自动解压。Linux 要运行的硬件的数据保存在设备树blob (devicetree.dtd)文件中。最后的那个文件(ramdisk8M.image.gz)是一个RAM 盘映像,载入内存后,使得RAM 的一部分用作像一个磁盘驱动器一样。 -

P425 本章我们看过了桌面环境下的Linux 的传统的引导过程,这包括对各种阶段的说明,这些阶段有BIOS、第一和第二级引导装载程序、内核和init。然后介绍了在Zynq-7000 AP 芯片上引导嵌入式Linux 的过程,并与桌面的引导顺序作了比较。仔细描述了成功完成引导过程所需的各种文件,包括BOOT.BIN、zImage、devicetree.dtb 和ramdisk8M.image.gz,还介绍了BIF 和所需的认证证书的细节。最后,详细说明了用来组成引导映像的bootgen 工具。