Veriog-数字序列检测(移位寄存器实现)

题目

模块持续每拍并行输入2bit数,请实现对(1011001)的序列检测功能,输入数据的顺序为高位2bit先输入,当检测到该序列时,输出一拍高电平脉冲信号

代码

`timescale 1ns / 1ps

module digit_sequence_detect_shifter(

input clk,

input rstn,

input [1:0] data_in,

output detect

);

reg [7:0] shifter;

always @(posedge clk) begin

if(!rstn) shifter <= 8'd0;

else shifter <= {shifter[5:0],data_in};

end

assign detect = (shifter[7:1]==7'b1011001 || shifter[6:0]==7'b1011001) ? 1'b1 : 1'b0;

endmodule

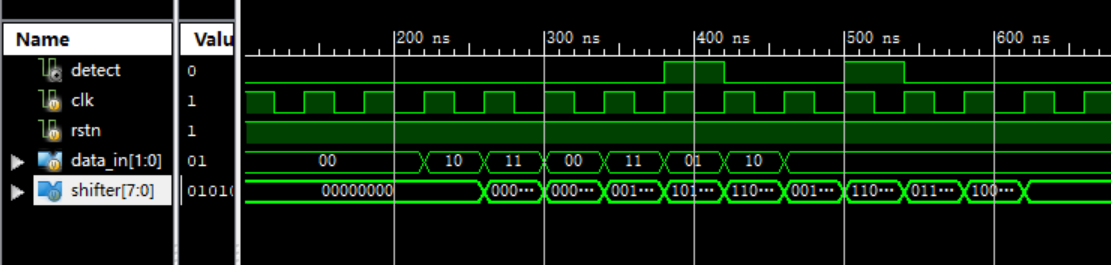

波形

总结

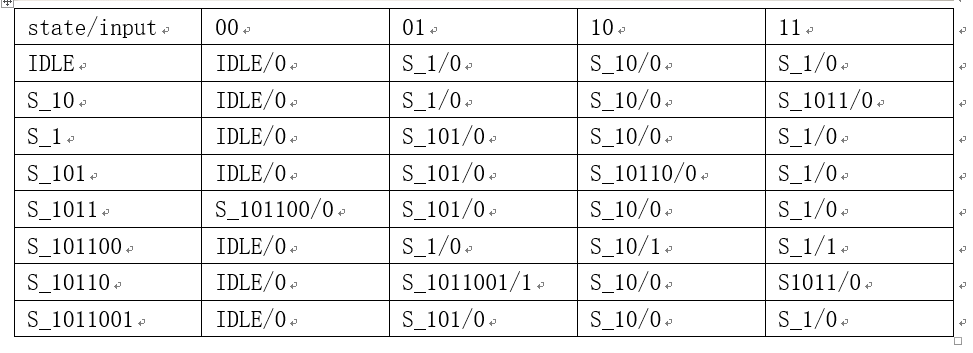

从代码可以看到,相比于用状态机实现的序列检测(状态转移如下表),用移位寄存更加简洁。值得注意的是,该实例用移位寄存器实现的方式类似用摩尔型状态机实现的效果,检测脉冲要在完整序列的下一个时钟上升沿才拉高,其实也可以当周期出结果:https://www.cnblogs.com/wt-seu/p/12815056.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号