时序路径分析模式

1、单一分析模式

对于单一分析模式(Single Mode),静态时序分析工具只会在指定的一种工作条件下检查建立时间和保持时间。因此只吃一种库。

2、BC-WC分析模式

对于最好-最坏分析模式(BC-WC Mode),静态时序分析工具会同时在PVT环境中最好的和最坏工作环境下检查建立时间和保持时间。吃2种库:max库和min库,分析setup时用max库,分析hold时用min库。

3、OCV分析模式

(1)OCV:是指在同一个芯片上, 由于制造工艺等原因造成的偏差。如电压降造成局部供电的差异,晶体管阈值电压的差异,晶体管沟道长度的差异,局部热点形成的温度系数的差异,互连线不同引起的电阻电容差异。

(2)分析准则:“快的更快,慢的更慢”。在检查建立时间时,使用max库计算数据路径延时(包括发射时钟的延时、建立时间),使用min库计算捕获时钟延时;在检查保持时间时,使用min库计算数据路径延时(包括发射时钟延时),使用max库计算捕获时钟的延时(包括保持时间)。

(3)OCV分析模式过于悲观,因为在同一个芯片内,不同地方器件参数的变化不会同时跨度最好边界条件(使用最好时序库)和最坏边界条件(使用最坏时序库)。为了对芯片内部参数差异更好的建模,使用时序减免(Timing derate)来达成:一次读入一个边界条件,再使用时序减免来建模同一个芯片内的差异。

set_timing_derate -early 0.9

set_timing_derate -late 1.1

通过以上减免值的设置,STA工具在计算时序延时中,最快路径会基于单一时序库计算结果再减少10%的延时值,最慢路径会基于单一时序库的计算结果再增加10%的延时值。在实际工程设计中,不同的生产工艺的timing derate 的设定是通过实际工程经验总结得到的。

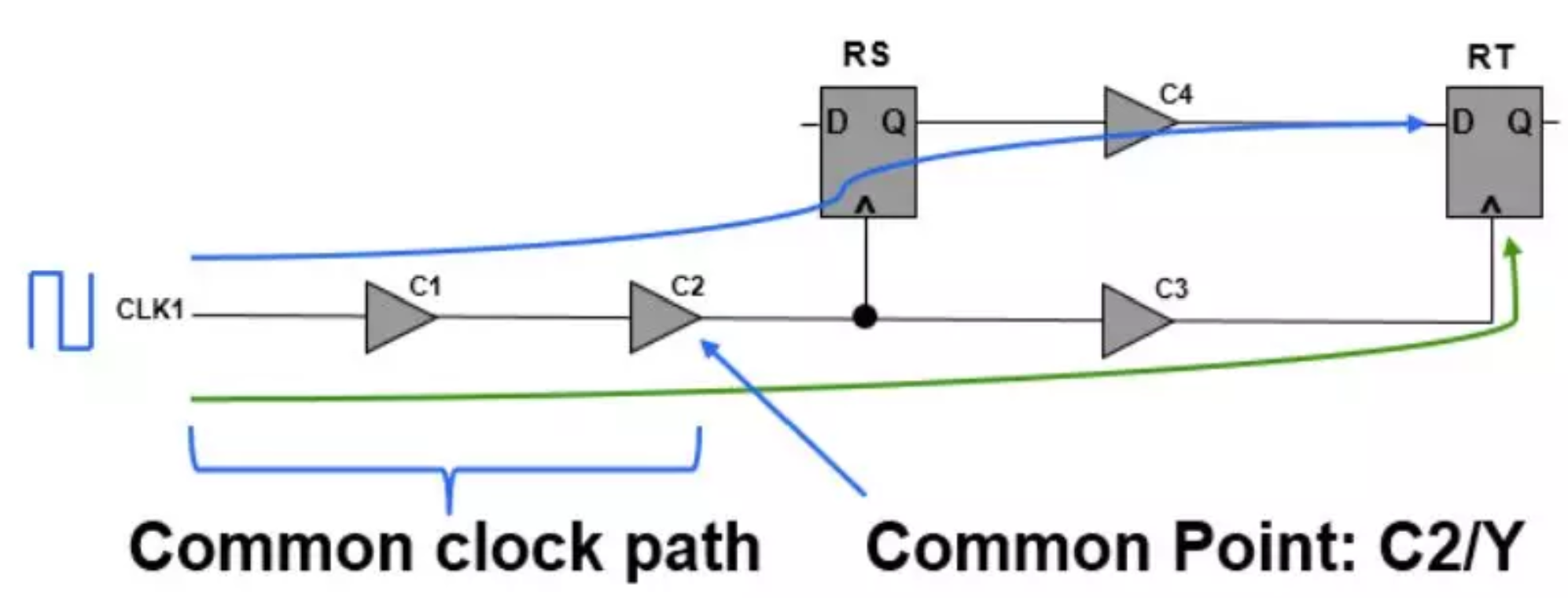

4、CRPR/CPPR

S公司:CRPR:clock reconvergence pessimism removal, 时钟重汇聚悲观移除

C公司:CPPR:clock path pessimism removal,时钟路径悲观移除

剔除公共clock path上的悲观度。

拿setup 分析为例,通常会设一个late 的derate 值(大于1的值)到launch clock path 上,同时会设一个early 的derate 值(小于1的值)到capture clock path 上,这就使得common clock path 在被当做launch clock path 和capture clock path 时的delay 有了差别,但是对于同一段path 在一个固定时间内,它的delay 值一定是固定的,不可能忽大忽小,所以在STA 分析时,需要把由于derate 引起的common path 上delay 的差值剔除掉,这就是所谓的CRPR/CPPR.

5、AOCV分析模式

Advanced OCV:通过对Cell在不同逻辑深度进行仿真,以及基于在路径在物理上跨越的距离得到一个精确的timing derate值。

一维AOCV:以Stage Count作为索引的查找表

二维AOCV:以Distance和Stage count作为索引的查找表

https://www.sohu.com/a/237459990_99933533

6、POCV

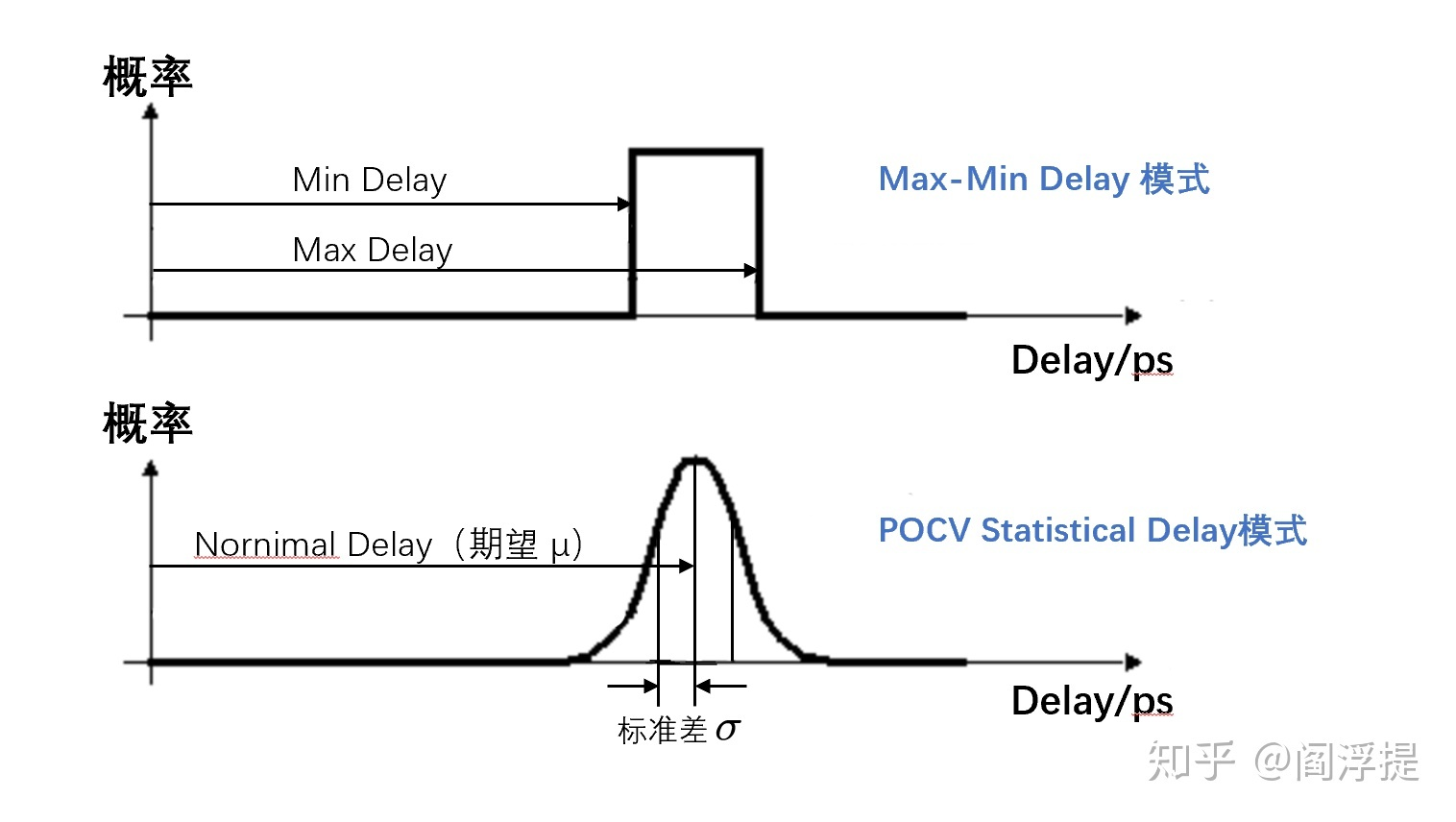

POCV,又称SOCV(Statistical On Chip Variation),如下图所示,POCV将delay模拟成一个正态分布。每个cell的delay最高概率出现在 u周围。整体落在

区间内的概率为99.7%