2017.0322.数字电路与系统-触发器

触发器的描述

1.时序图(也称为工作波形图)

时序图分为两种,一种是理想的时序图,两一种是实际的时序图。理想的时序图,不考虑门的延迟,也不考虑门电路翻转的时间。

画理想的时序图时,因为整个图形包含输入和输出,所以画的时候要注意先后顺序,是先有输入,才有输出的状态改变。

对于由两个与非门组成的基本触发器,当两个输入均能为1时,触发器的输出仍保持之前的输出状态不变,如果此时,将两个输入端撤掉,那么输出端的状态依旧存在,且不变。这样就体现出触发器的记忆存储功能。

2.基本触发器的特点

输入信号直接作用于输出门上,因此输入信号的改变可以直接影响输出端的状态。也就是输入信号的变化可以立即在输出上表现出来。这样两个基本触发器的输入端称之为直接置位端,复位端。

3.基本触发器可以应用在机械开关的消抖动电路。

机械开关的抖动是指,当开关的弹簧片弹到某一处时,它并没有立马稳定下来,而是会有短暂的脱离,再接触,再脱离,最后稳定接触的现象。这也是拨动开关后,计数器能够进行计数的原理。按一次开关,计数器就记一次数。

具体的原理,视频没有讲解清楚,具体触发器怎么解决抖动不是太明白。

4.基本触发器可用于二进制信号的存储和传递。基本的触发器可以存储一位二进制信息,在计算机中,存储信息的最小单位是一个字节,所以存储一个字节的信息需要八个基本触发器。当进行数据传输时,只要将源触发器的输出端接到目的触发器的输入端即可。为了使用方便,通常在目的触发器的输入端加上一个与门,用一选通端来选通触发器的状态。

锁存器

1.时钟控制的触发器是在基本触发器的基础上,加上触发引导电路。基本触发器连同其门控电路作为一个整体,称为锁存器或种控触发器。

锁存器在时钟的某一敏感电平的时候,这个触发器才是起作用的,另一个时刻是保持不变的。也就是说,对门控电路,当门控电路出于选通的情况下,这个触发器和基本的触发器是没有区别的,当门控电路出于静止的时候,触发器就被锁定了,这时触发器的状态是不能改变的。也就是说,门控电路静止的那一刻,它的状态锁存在触发器里面,这时候输入的变化在触发器里面是体现不出来的,它体现的是门控电路被静止前的那一时刻,那一状态锁存在触发器里面。

2.钟控的RS触发器(锁存器)

当CP为1的时候,门控电路没有起到作用;当CP为0的时候,门控的电路的两个输出为1,基本触发器的状态就保持不变。换句话说,当CP为1的时候,锁存了为1的前一刻触发器的状态,这就是使用锁存器的目的。这个锁存器的约束条件和之前基本触发器的约束条件不太一样。基本的R'S'触发器的约束条件是两个输入端R'S'至少有一个为1,但是锁存器中有一个与非门控制电路,也就是锁存器的R,S输入中要有一个为0,(在CP为1的情况下)即RS=0.同前述的基本触发器一样,锁存器也有状态转移方程,状态转移真值表,状态转换图,时序图。所有描述锁存器的方法都要加上CP部分.

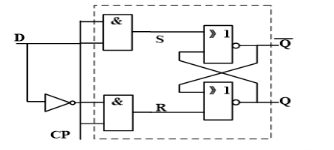

3.钟控的D触发器

由两个与或门的基本触发器构成,CP是门控,D是数据端,分成两条线对应于与或门基本触发器的输入,S=D,R=D'。

CP为0时,S,R的输入均为0,对触发器的状态没有影响。当CP为1时,触发器输出为D

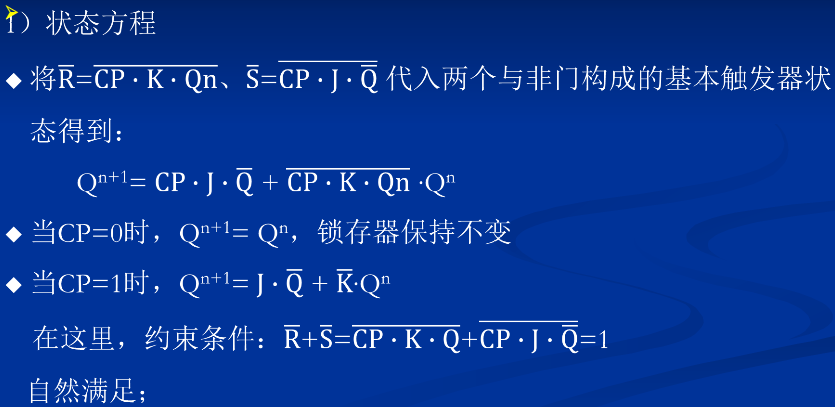

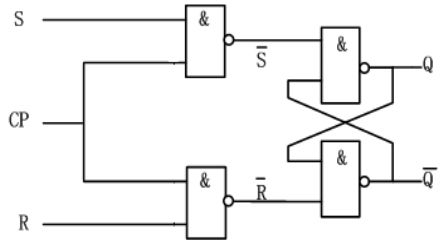

4.钟控JK触发器

钟控JK触发器的状态表达式是建立在两部分的集成的基础上合成的,一个是门控电路,一个是基本触发器。就基本触发器而言,Qn+1=S+R'Qn,由于添加了门控电路,S'=(JQ'n)’,R'=KQn,在CP为1的前提下,然后直接代入,得到的Qn+1次态输出为现态和K,J的三种输入的表达式,要记住R'S'都是基本触发器的输入。由此可见,钟控JK触发器是在与非门基本触发器的基础上发展而来,还有一点就是触发器始终是有约束条件的。观看下面的求解表达式的过程,我们发现整个过程是很严谨的数学过程。