2017.0320.数字电路与系统-触发器

触发器

1.能够存储一位二进制信息,(是说0-1两个状态么?)触发器是很基本的逻辑器件(基本说明很常用,逻辑器件的逻辑两字是来源于逻辑电路么?)具有存储功能,那么电路的输出就不仅仅取决于当前的输入,还跟电路现在所处的状态有关,能够的存储说明这时刻保留的输出是和上一时刻的输入相关的。“所处的状态”这个词,我的理解为,不能像组合逻辑电路那样,当前时刻一有输入,整个电路的的输出不一定和当前的输入对应起来,而是和电路的整体环境有关,不在仅仅取决于当前的输入了。

触发器的输出就是两个两句话,不仅仅取决于当前的输入,还取决于过去的输入。还有一种关于触发器输出的说法就是,输出不仅取决于当前的输入,还取决于当前的状态,“当前的状态”这个词指谓,可能当前的输入没法使得当前的输出与当前的输入一致,当前的输出依旧保持着原先的模样。

2.触发器往往有一个或多个信号的输出端,一个是正常的存储值,另一个可以选择为输出存储器的反码。“输出反码”说明在最后输出时,接了一条线,上面载有反向器。

3.触发器的特点:它要有两个稳定的状态。两个稳定的不同状态能够表示二进制的0和1。

光能够存储还不行,还要能对存储信息进行改变。要能够根据输入的变化,输出可以置零和置一。根据外面信号的变化,触发器可以存储不同的信息,存储状态0或者存储状态1.

两个特点,能够存储,也能够变化。这种存储和变化并非一般意义上的瞬时变化,还会包含有时间上的延时。

4.基本的R'S'触发器。整体的构造是两个与非门组成,同之前的组合逻辑电路的不同点在于,这里存在一个反馈的机制。输出反馈到了输入。两个输入端分别为S',R',两个输出端分别为Q和Q'。

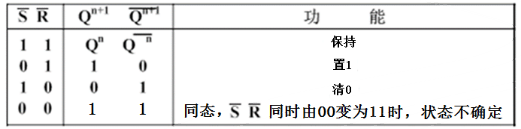

这里讨论输出端的输出是什么,都要加上,“下一时刻的”输出端的输出是什么,Qn+1=(S'Q')',由此式可见的是Qn+1输出除了要考虑即时的输入S',还要考虑输出Q',Q'的信号可不是立马就能得到的,所以存在“下一时刻”的说法。基本的R'S'触发器的真值表要牢记。

S'代表set,是置位的意思,非的符号表示是低电平置位的,低电平的输入让Q输出为1,置位为1.清零和置位说的都是Q端的输出。

什么是触发器?这里给出的判别条件是,要能够清零和置一,以及可以具备两个不同的状态,主语均为Q端?

基本的R'S'触发器是由两个与非门集合成的对称结构的逻辑器件,两个输入端的0-1和1-0,得到的输出是对应的。如果两个输入均为0,那么输出端都为1.

5.这里着重讨论基本的R'S'触发器各种输入输出的变化情况,从S',R'的两个输入都为0的情况开始,这时候两个输出都为1。在触发器中,只要输入为0,对应的输出就为1。当其中的一个输入端S'从0变为1时,对应的输出端就为0。这里难的是,两个输入同时由0变为1时,我们讨论的例子都是从两个输入为0开始进行变化。

与非门只要有输入为0,与非门的输出就为1.

在整个R'S'触发器中,最难的变化是两个输入端同时由0变为1,当两个输入端为0时,两个输出端均为1.一旦两个输入同时变为1,那么两个输出Q和Q'的输出取决于与非的另个一输入,S'和R'都为1,对与非门的输出没有任何影响,不用考虑。这也就相当于每个输出经过一系列的传输后,本质上是自己决定自己。我们先分析Q端,在S'变为1后,开始时,Q‘仍为1,所以Q的输出为0,那么Q反过来作用到下面的与非门时,Q'就为1,也就是Q’保持了不变,但是为什么在Q端输出为0时,Q'要为1呢?说明下面的与非门反应速度要比上面的慢(来自于我们的假设)。这种情况的诞生来源于两个与非门的速度的不一致,如果速度一致的话,Q和Q'反馈到输入的信号同时为1,那么经过与非门后,输出Q和Q‘均为0,均为0的结果反馈到输入后,经过与非门输出又同时为1,再反馈,这样循环往复,输出的两个结果不断地在0和1之间来回往复,前提是两个与非门的反应速度是一样的。实际上,两个门电路不可能做到一样,一旦出现差异的话,就会导致一个输出稳定不变,另个一输出变为0,谁的反应快,谁就先变为0。现实生活中,我们无法辨别哪个门电路反应速度快,所以必须对基本R'S'触发器的输入进行限制。我们刚才论述地是两个输入同时由0变为1的情况。

我们再讨论两个输入均为1时的情况,不再是两者由0变为1了。两个输出均是自反馈,由于两个输入均为1且都是与非门,那么与非门的输出就只取决于另一个输入了。Q经过下面的与非门时,进行了一次非运算,再经过上面的与非门时,又经过了一次非运算,有了两次非运算相当于没有改变。可以这么说,在两个输入同时为1的情况下,Q取0或者1都是成立的,存在着不确定的因素,这个和组合逻辑电路的定义完全不一样。

6.为了使上述的情况的不会发生,我们要对基本R'S'触发器的输入进行限制,不允许Q'和R'同时为0,添加了约束条件。

基本触发器的真值表和之前的组合逻辑电路的真值表也有些不一样,集中在输出的标志上,Qn+1,(Q')n+1,数字电路的时间是离散的,具体时间的间隔是多少我们并不清楚,(n+1)时刻是在n时刻之后的。Qn代表输入信号到来之前的输出信号,Q还没发生变化的状态,称之为现态。Qn+1是输入信号到达,Q的状态发生了变化,称之为次态。

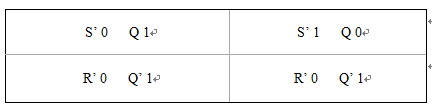

两个或非门构成的触发器

1.两个或非门构建的触发器的输入输出的标记和两个与非门的标记是不一样的,本质上都是为了实现触发器的功能。两个或非门触发器是高电平有效