16位CPU多周期设计

16位CPU多周期设计

这个工程完成了16位CPU的多周期设计,模块化设计,有包含必要的分析说明。

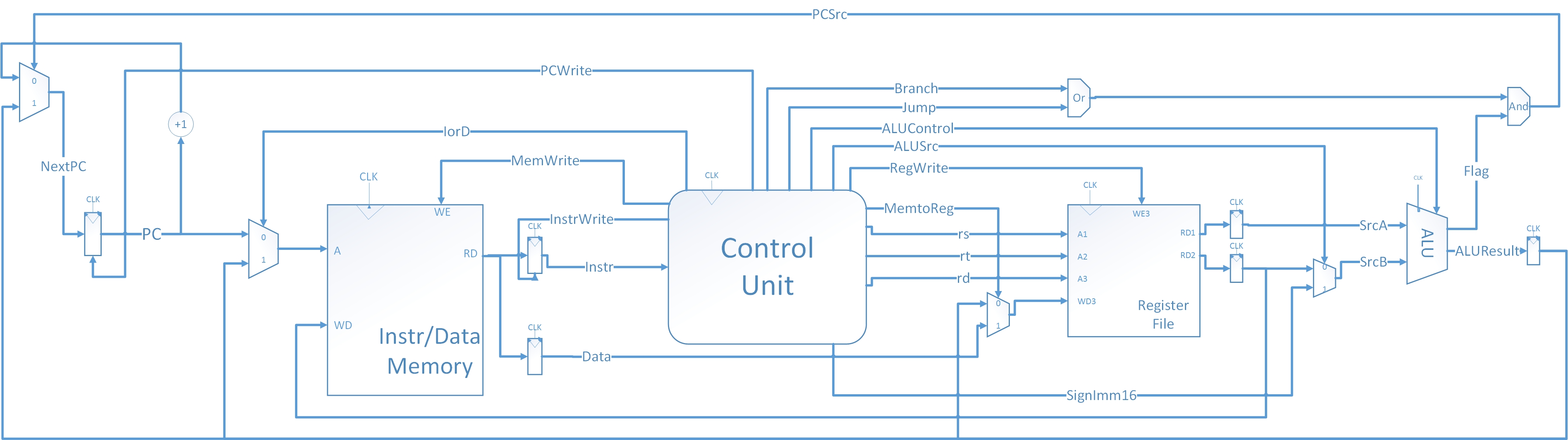

多周期CPU结构图

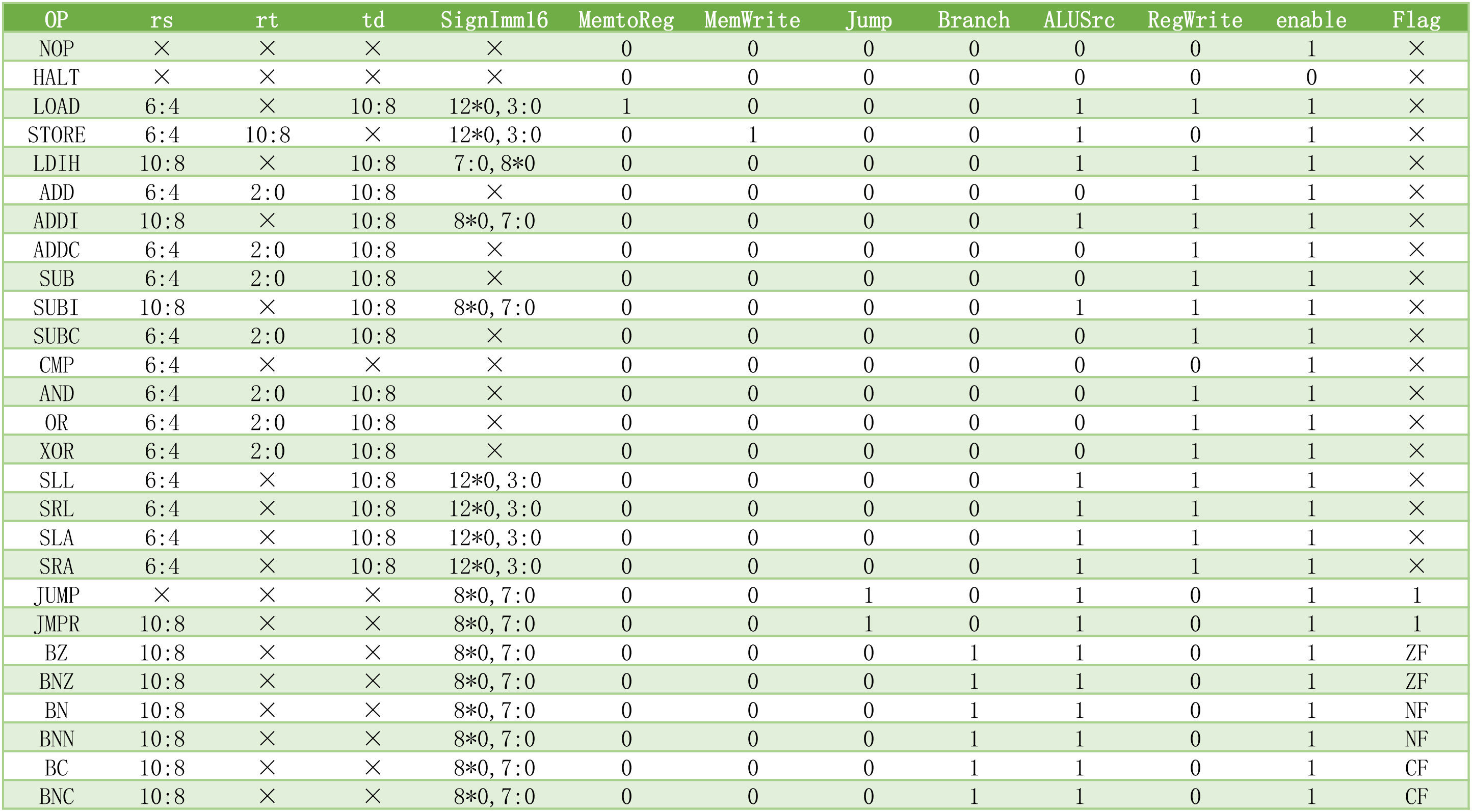

多周期CPU设计真值表

对应某一指令的情况,但仅当对应周期时才为对应的输出,不是组合逻辑

设计思路

-

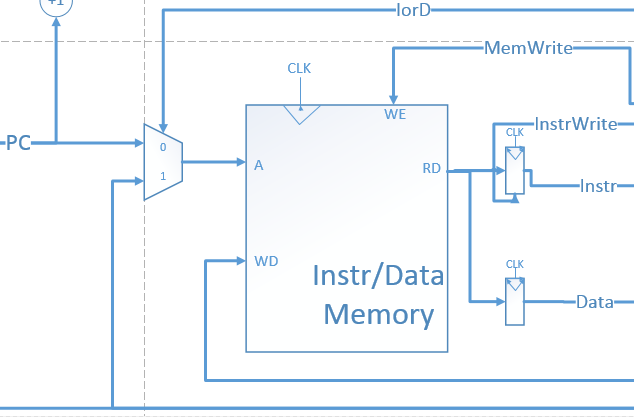

Instruction/Data Memory:

一共有两种模式:

1、 输入8位的地址PC,输出对应内存的16位指令内容

2、 输入8位的地址Address,输出对应内存的DataMemory的内容

输入写入内容WD,当WE写入信号为真的时候,写入到地址为Address的内存里面

-

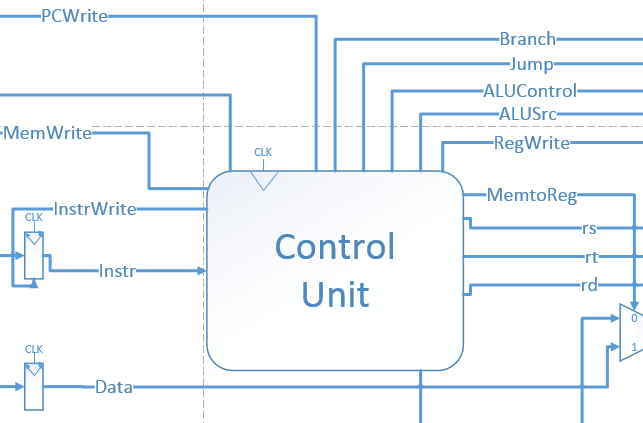

Control Unit

唯一输入16位的指令,根据状态转移图和真值表,输出唯一信号列表,转移方向有指令的高五位Op来决定,并且地址输出集成在控制单元模块中,简化了框图。

-

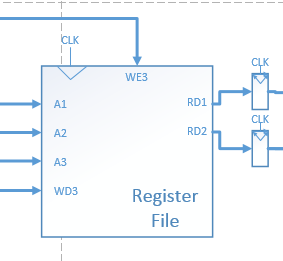

Register File

输入三个地址和写入内容,写入信号,输出两个地址对应的内容

由于单周期内不能一边读一边写,故有一个时钟信号,通过一级缓存,在下一个时钟信号来临时立即写入内存

-

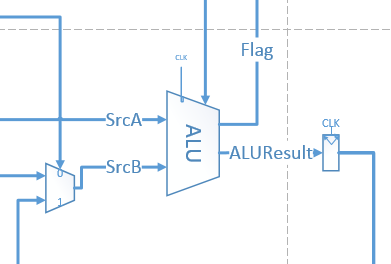

ALU

输入运算数和指令,输出运算结果以及标志位

由于单周期内,标志位并不在当前周期而在下一周期使用,故增加时钟信号,通过一级缓存,在下一个周期时判断使用

-

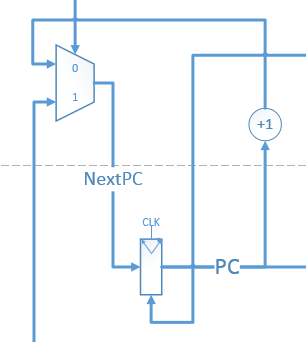

PC-NextPC

根据分支指令,跳转指令和标志位的组合逻辑,决定PC是+1还是到某目标位置,且这里需要一个enable信号进行PC写入控制

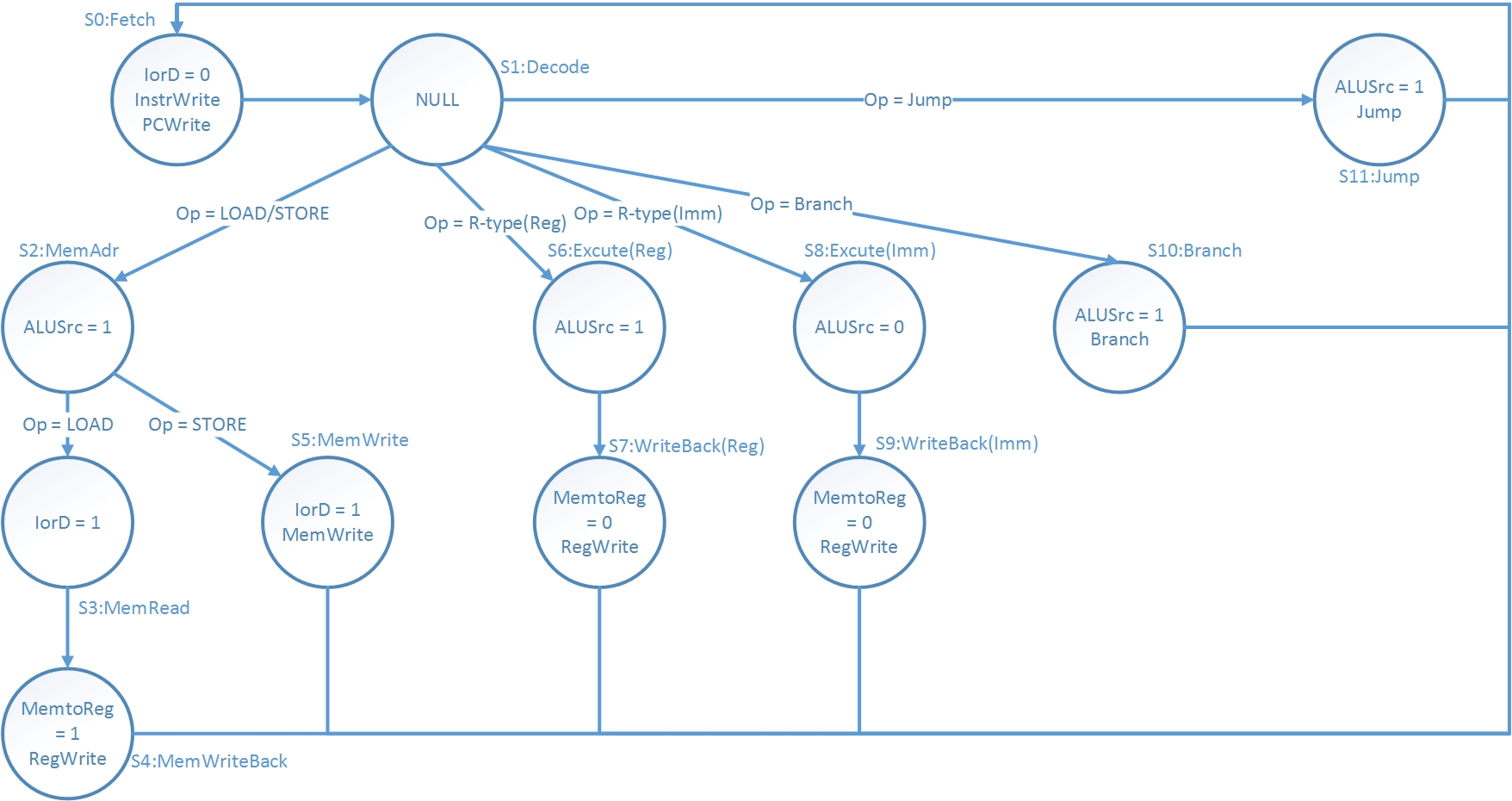

多周期CPU状态转移图

- 写入指令:需要最长的5个周期,读取指令一个周期,指令解码一个周期,寄存器寻址一个周期,读取Data一个周期,写入寄存器一个周期,总共用了五个周期。

- 存储指令:需要4个周期,读取指令一个周期,指令解码一个周期,寄存器寻址一个周期,写入寄存器一个周期,总共用了4个周期。

- 有关寄存器的R-type指令:需要4个周期,读取指令一个周期,指令解码一个周期,寄存器寻址一个周期,写入寄存器一个周期,总共用了4个周期。

- 有关立即数的R-type指令:需要4个周期,读取指令一个周期,指令解码一个周期,寄存器寻址和立即数获得一个周期,写入寄存器一个周期,总共用了4个周期。

- 分支指令:只需要3个周期,读取指令一个周期,指令解码一个周期,运算模块一个周期,总共需要3个周期。

- 跳转指令:只需要3个周期,读取指令一个周期,指令解码一个周期,立即数地址运算一个周期,总共需要3个周期。

特别解释:

i. 状态转移图仅列出了全部的enable信号和select信号,其余和时序逻辑无关的信号均为组合逻辑信号,不在状态转移图中列出,可直接看上面的真值表。

ii. 写入信号只在出现的状态中为真,其余状态均为假

iii. Docode状态里面确定真的不需要改变信号的值,所以为NULL

浙公网安备 33010602011771号

浙公网安备 33010602011771号