NAND FLASH的接口控制设计

Nand flash是flash存储器的其中一种,Nand flash其内部采用非线性宏单元模式以及为固态大容量内存的实现提供了廉价有效的解决方案。NAND FLASH存储器具有容量较大和改写速度快等优点适用于大量数据的存储,因而在业界得到了越来越广泛的应用。NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。

NAND Flash 的存储结构

大多数的NAND Flash都大同小异,所不同的只是该NAND Flash芯片的容量大小和读写速度等基本特性。

块Block 是 NAND Flash 的擦除操作的基本/最小单位。页是读写操作的基本单位。

每一个页,对应还有一块区域,叫做空闲区域/冗余区域,而在 Linux系统中﹐一般叫做OOB(Out Of Band)[2]。这个区域最初基于NAND Flash 的硬件特性﹐数据在读写时候相对容易出错﹐所以为了保证数据的正确性,必须要有对应的检测和纠错机制,此机制被叫做EDC /ECC。所以设计了多余的区域﹐用于放置数据的校验值。OOB的读写操作一般是随着页的操作一起完成的,即读写页的时候,对应地就读写了OOB。OOB的主要用途:标记是否是坏块﹐存储ECC数据﹐存储一些和文件系统相关的数据。

NAND Flash的接口控制设计

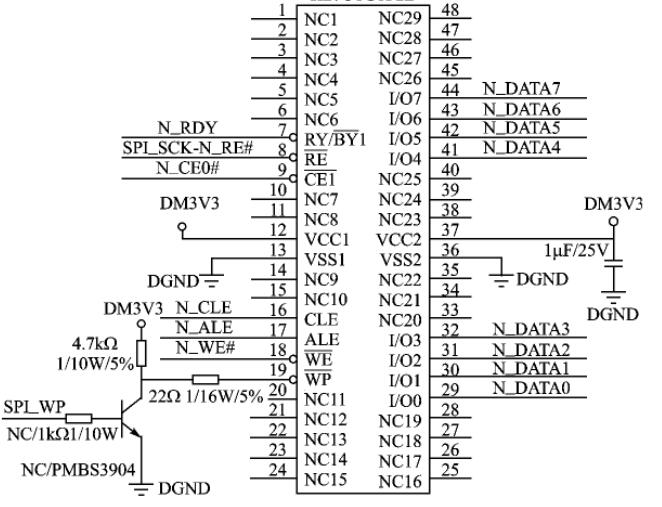

由于NAND Flash只有8个I/O引脚,而且是复用的,既可以传数据﹐也可以传地址、命令。设计命令锁存使能(Command Latch Enable,CLE)和地址锁存使能( Ad-dress Latch Enable,ALE),就是先要发一个CLE(或ALE)命令,告诉NAND Flash 的控制器一声,下面要传的图1NAND Flash控制电路是命令(或地址)。这样NAND Flash内部才能根据传入的内容﹐进行对应的动作。相对于并口的NOR Flash 的48或52个引脚来说,大大减小了引脚数目,这样封装后的芯片体积小。同时减少了芯片接口﹐使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

NAND Flash的接口控制电路如图1所示

浙公网安备 33010602011771号

浙公网安备 33010602011771号