双端口SRAM中读干扰问题

普通的存储器器件为单端口,也就是数据的输入输出只利用一个端口,设计了两个输入输出端口的就是双端口sram。虽然还具有扩展系列的4端口sram,但双端口sram已经非常不错了。双端口sram经常应用于cpu与其周边控制器等类似需要直接访问存储器或者需要随机访问缓冲器之类的器件之间进行通信的情况。

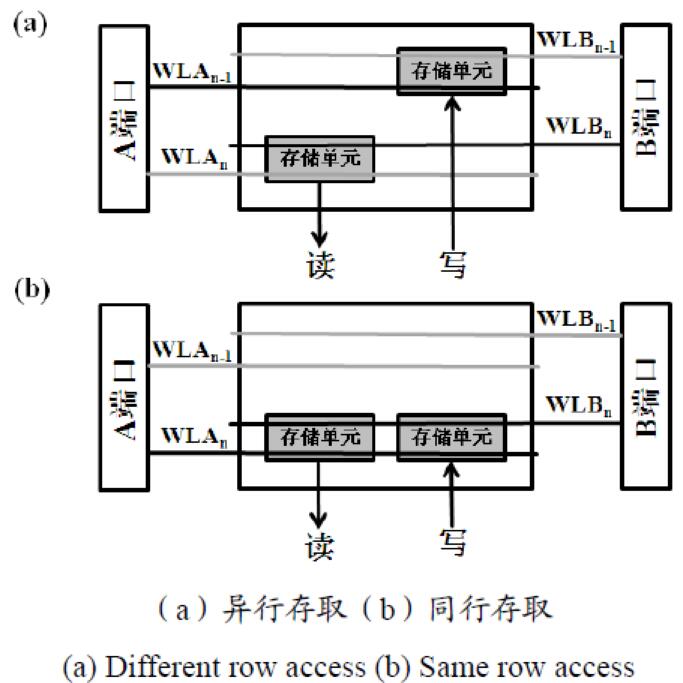

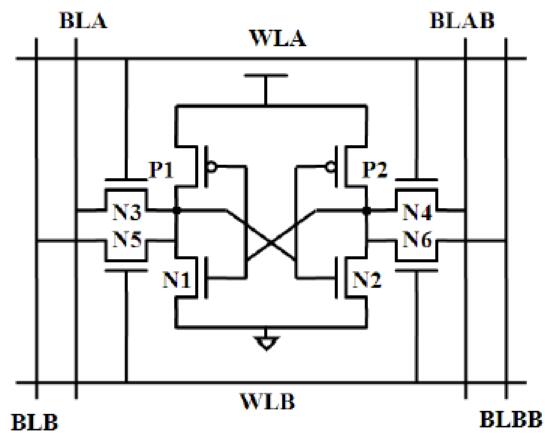

从存储单元来看,双端口SRAM只是在单端口SRAM的基础上加上了两个存取管(见图1),但要实现两个端口对存储单元的独立读写,还要对新增的端口复制一套单端口SRAM的读写外围电路。然而这样虽然增强了存储器的读写能力,但却是以降低存储单元的稳定性为代价的,具体表现为双端口SRAM的两个端口进行同行存取时发生的读写干扰(Read/WriteDisturbance)问题;并且当两个端口进行异步存取时,读写干扰会表现出一定的规律性;对读写干扰问题目前尚未找到完美的解决方法,现有的各个方法都具有一定的侧重方向。

读干扰的原理分析

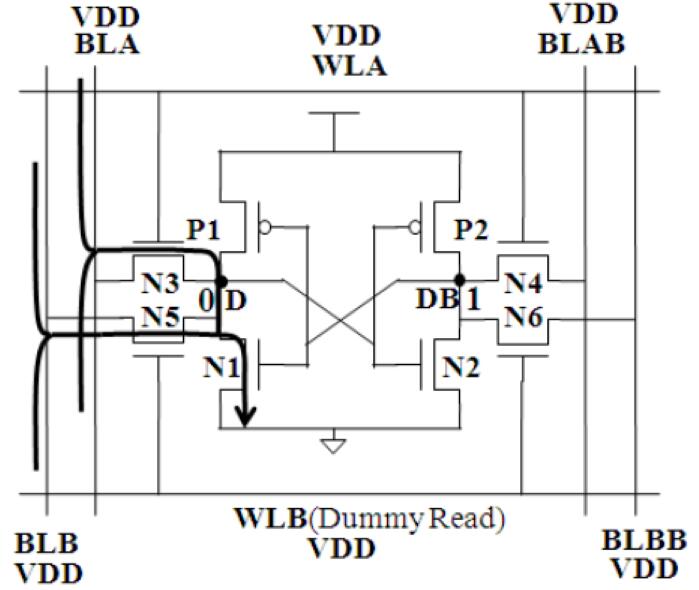

如图2(a)所示,当双端口SRAM的两个端口对不同的行进行操作时,只有连接在WLAn-1和WLBn上的存取管才会被打开,即一个双端口SRAM存储单元只有两个存取管被打开,所以此时双端口SRAM单元可以像单端口SRAM单元一样工作。但是如果两个端口对同一行进行操作时,如图2(b),由于半选择问题该行所有存储单元的所有存取管都将被打开。当一个进行读操作的存储单元的所有存取管都被打开时,和单端口SRAM读操作时存取管降低RSNM同理,该单元的RSNM将有更大幅度的下降,这称为读干扰;此外,伪读取操作对执行写操作的存储单元的数据写入也会造成困难,这称为写干扰。现在假设A端口在进行读操作,B端口在进行写操作,下面分别分析读干扰。

读干扰

图3是图2(b)中左边进行读操作的存储单元的具体情形,可以看到,B端口的写操作使WLB为高电平,此高电平对该单元产生了伪读取操作。与单端口SRAM的读取操作相比,下拉管N1将同时对BLA和BLB放电,这将导致两个结果:第一,对BLA的放电电流减小,造成读取时间增加;第二,D点电压将会比单端口SRAM中读取操作升高得更高,从而进一步降低RSNM,甚至直接使单元翻转。对于后者可以这样简单地分析:N3和N5同时打开后,二者并联,若将其看成整体,则存取管的宽度将增加一倍,其“电阻”减半,而N1的电阻不变,故在放电通路上D点的分压变得更高;对于前者,虽然放电通路的电阻减小,N1的下拉电流增大,但其还没有增大到原来的两倍(其宽度加倍电流才会加倍),而N3和N5的电流相等,故N3分得的电流较之单端口SRAM将减小。

图3双端口SRAM单元中的读干扰

浙公网安备 33010602011771号

浙公网安备 33010602011771号