单端口SRAM与双端口SRAM电路结构

SRAM是随机存取存储器的一种。所谓的静态是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。SRAM不需要刷新电路即能保存它内部存储的数据,因此SRAM具有较高的性能.

SRAM的速度快但价格相对昂贵,一般用小容量的SRAM作为更高速CPU和较低速DRAM 之间的缓存(cache).SRAM也有许多种,如Async SRAM (异步SRAM)、Sync SRAM (同步高速SRAM)、PBSRAM (流水式突发SRAM),还有INTEL没有公布细节的CSRAM等。

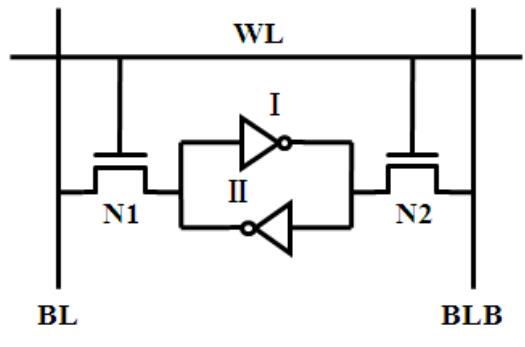

不管是哪种 SRAM,其基本的原理大都是通过两个首尾相接的反相器来锁存数据的,如图 2-2 所示。其中反相器Ⅰ和Ⅱ形成正反馈,使电路总能恢复到稳定状态;N1 和 N2 叫做存取管,用来读取或者写入数据;字线( WL)控制存取管的开启,从而将存储的数据从位线( BL 和 BLB)传送至外围电路。反相器Ⅰ、Ⅱ和存取电路组成了一个 SRAM 单元(SRAM Cell)(由于该单元只能存储一位的数据,有时也叫做 bit-cell)。根据存取电路的不同,目前大 致可以将 SRAM 单元分为上述三种端口的类型,下面分别介绍这些单元的结构。

单端口 SRAM

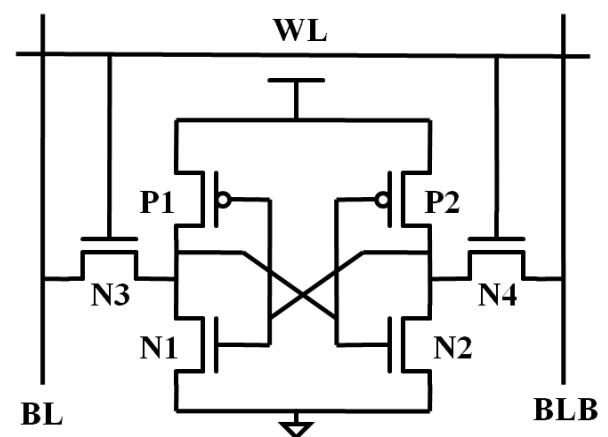

根据图1中反相器的不同,单端口SRAM单元有电阻负载型、无负载型和六管 CMOS 单元等。电阻负载型存储单元由于电其压传输特性曲线(VTC)不陡并且功耗大已远离了主流设计;无负载型存储单元虽然可以实现较高的密度[16],但其稳定性差;六管 CMOS SRAM 单元是目前主流的设计,其结构如图2 所示。它由 6 个晶体管(N1~N4、P1~P2)组成,N1、N2 叫做下拉(PD)管,P1、P2 叫做上拉(PU)管,N3、N4 是存取管,有时也叫传输管(PG)。这种六管存储单元具有很好的健壮性、低功耗和低电压工作特性,所以非常受欢迎;下文中的两端口和双端口存储单元以及在分析SRAM 单元的操作、特性时都将采用这种结构,并简称为六管单元。

两端口 SRAM

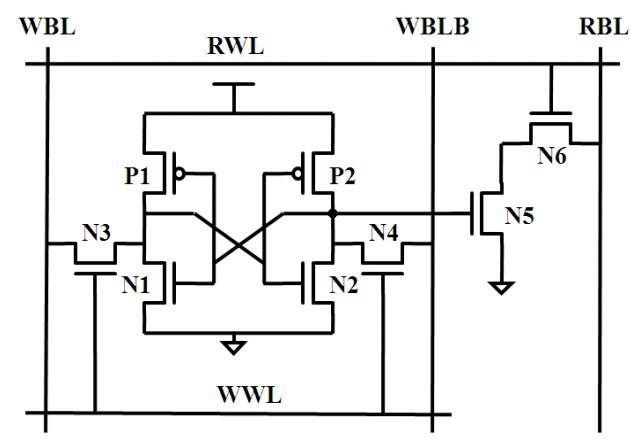

随着工艺尺寸的不断降低,参数波动变得越来越严重,六管SRAM存储单元固有的缺点(见下文)导致其在低电压情况下难以提供足够的稳定性,于是出现了一种 8 管 SRAM 单元[17],如图 3 所示。这种结构具有独立的读写字线(RWL, WWL)和读写位线(RBL, WBL 和 WBLB),从而有分开的读端口和写端口;数据从读端口读出,从写端口写入。这样不仅提高了稳定性,而且可以进行同时读写,从而有更高的性能。但是由于读端口是单端的,外围放大电路需要更大的读位线摆幅(较之差分)才能得到满幅的逻辑电平,所以导致存取时间变长。

双端口 SRAM

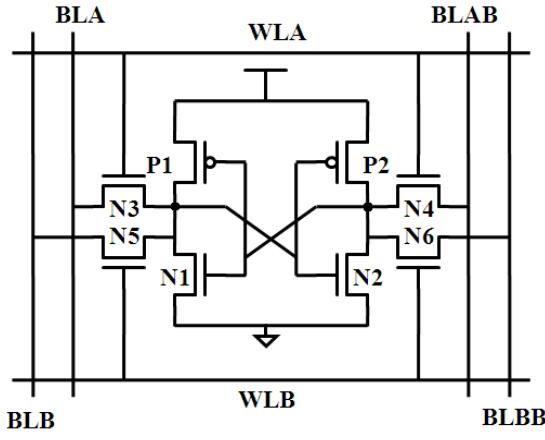

双端口注sram芯片存储单元是在单端口六管 CMOS 单元的基础上复制增加了一套读写端口,如图4 所示;与两端口 SRAM 中的某一端口只能完成读或写功能不同,在双端口 SRAM 中,每一个端口都可以进行读和写操作;因此也把这种结构叫做两读写(2RW)单元,把 2P-SRAM 的存储单元叫做一读一写(1R1W)单元,而把六管 CMOS 存储单元叫做一读写(1RW)单元。

浙公网安备 33010602011771号

浙公网安备 33010602011771号