串口SRAM和并口SRAM的引脚区别

首先来看一下并口和串口的区别:

引脚的区别:

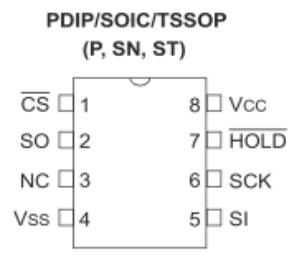

串口SRAM(或其它存储器)通常有如下的示意图:

串口SRAM引脚

引脚只有SCK,CS#,SI,SO,HOLDB,VCC,VSS不到8个,一般遵循SPI协议,

并口SRAM引脚很多,串口SRAM引脚很少。

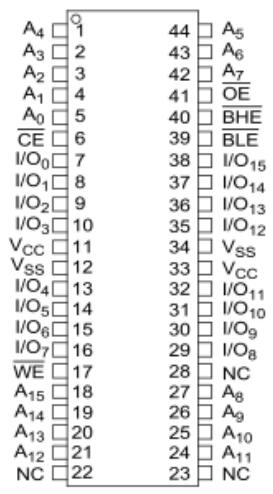

大部分SRAM是并口(parallel)操作的,也有少部分奇葩是串口协议的。并口的SRAM通常有如下的示意图:

并口SRAM引脚

引脚密密麻麻接近50个,包含地址、IO、使能信号、电源等。

其中地址通常和容量有关系,这里是1Mb的容量,地址有16个(A15-A0);

其中IO通常是8的倍数,这里是16个(IO15-IO0);

使能信号CE#,WE#,OE#,BHE#,BLE#,请原谅我用#代替上划线,上划线根本无法输入,MD;

电源信号:VCC/VSS.

电路分类的区别

并口SRAM是异步电路,没有时钟信号;

串口电路是同步电路,有时钟信号。

再来看看并口SRAM的应用场合。

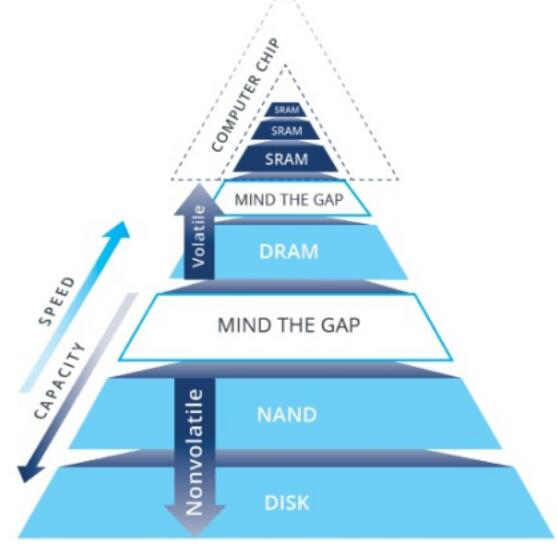

并口SRAM通常速度都比较快,应用在很多高速场合,比如作为CPU的高速缓冲存储器(Cache),如下图所示:

SRAM处于计算机存储器金字塔的最顶端,在速度上,SRAM>DRAM>NAND。因为SRAM的操作条件比较简单,就是简单的MOS管打开,相互fighting或者传输值的过程,用core电压就可以实现。而DRAM要产生3v左右的高压,NAND的操作电压就更高了。

在面积上,SRAM存储单元6个管子(6T),相对于DRAM的1T1C以及NAND的1T而言,又是最大的。所以在价格上也是SRAM>DRAM>NAND。

有时候SRAM也会作为寄存器的替代,因为SRAM存储单元(6个管子)面积相对于寄存器(DFF)要小不少,如果在设计中需要用到几百Byte,使用寄存器的面积可能比SRAM大上好几倍。

浙公网安备 33010602011771号

浙公网安备 33010602011771号