如何减小SRAM读写操作时的串扰

静态存储器SRAM是一款不需要刷新电路即能保存它内部存储数据的存储器。在SRAM 存储阵列的设计中,经常会出现串扰问题发生。那么要如何减小如何减小SRAM读写操作时的串扰,以及提高SRAM的可靠性呢,下面宇芯来简单介绍。

设计结果与仿真分析

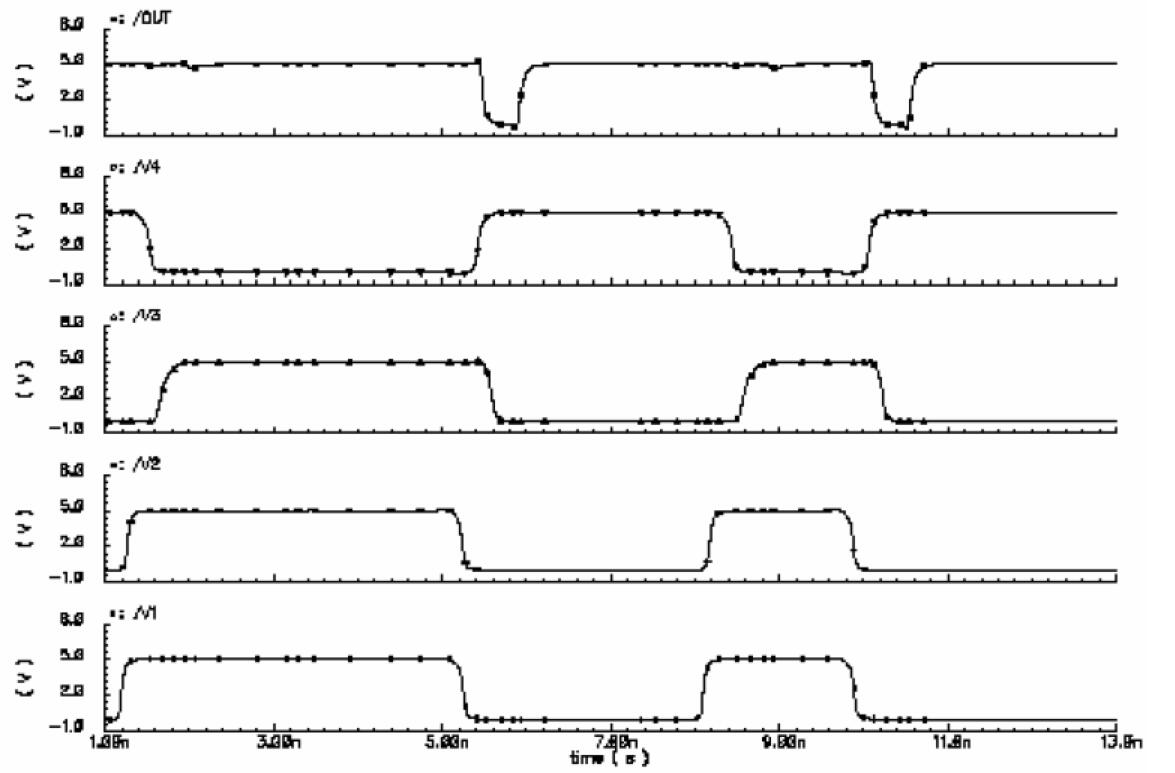

图1为脉冲产生电路通过analog Environment的仿真波形图。当地址产生变化,由于信号经过的延迟路径长短不同而产生了脉冲,当V1脉冲生成时,作为灵敏放大器输入端电位平衡的控制信号,缩短了预充时间,大大提高了读取速度。V2 作为位线预充电路的控制信号,避免了数据读写时发生错误。V3和V4作为字线放电电路的控制信号,只有当V3和V4同时为低电平时,字线放电。通过后仿真,我们看到在读操作时,防串扰结构布局的存储器平均输出时间比一般结构的存储器输出时间短,可见在速度上,防串扰结构布局的存储器具有一定的优势。在性能方面,该结构减小了SRAM读写操作时存储阵列中单元之间的串扰,提高了可靠性。

图1 脉冲产生电路波形图

在sram芯片存储阵列的设计中,经常会出现串扰问题发生,只需要利用行地址的变化来生成充电脉冲的电路。仿真结果表明,该电路功能正确,性能优良,减小了读写操作时存储阵列中单元之间的串扰,与其它脉冲电路相比,该电路结构简单、紧凑,对于嵌入式SRAM 的发展具有极其重要的现实意义。

浙公网安备 33010602011771号

浙公网安备 33010602011771号