STM32F4以太网MAC接口

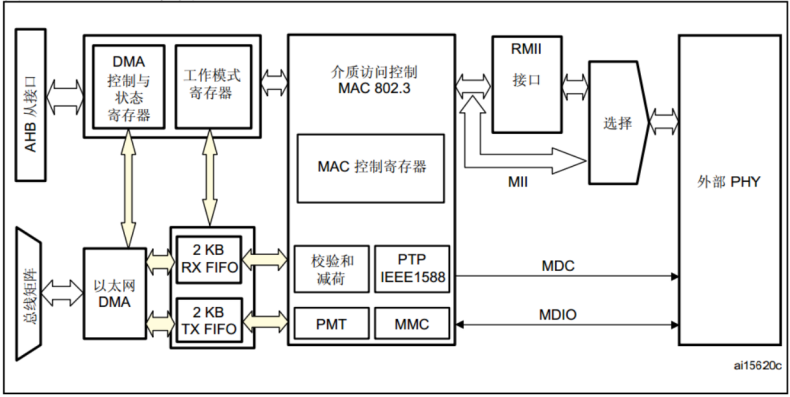

STM32F407自带有10/100Mbit/s的以太网MAC内核,STM32F407的ETH框图如下:

F407的MAC有3种接口:SMI、MII和RMII。下面依次介绍这3种接口。

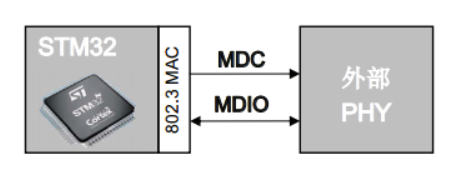

①SMI接口

SMI接口为站管理接口,程序中可以通过这个接口来访问PHY寄存器。SMI接口有两条线:数据线MDIO和时钟线MDC。该接口可支持访问最多32个PHY。

MDC:周期性时钟,提供以最大频率2.5MHZ传输数据时的参考时序,在空闲状态下,SMI管理接口将MDC信号的时钟信号驱动为低电平。

MDIO:数据输入/输出比特流,用于通过MDC时钟信号向PHY设备同步传输信息。

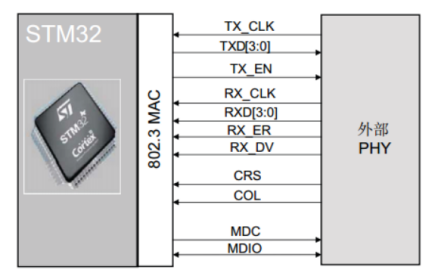

②MII接口

MII接口:介质独立接口 (MII) 定义了 10 Mbit/s 和 100 Mbit/s 的数据传输速率下 MAC 子层与 PHY 之间的互连。 MII 包括 16 个数据和控制信号的引脚。

TX_CLK和RX_CLK为发送和接收连续时钟,当速率为10Mbit/s时为2.5MHZ,速率为100Mbit/s时为25MHZ。

要生成TX_CLK和RX_CLK时钟,必须向外部PHY提供25MHZ时钟,通常我们使用25M的晶振,也可以使用STM32F4xx的MCO引脚输出25MHZ的时钟。

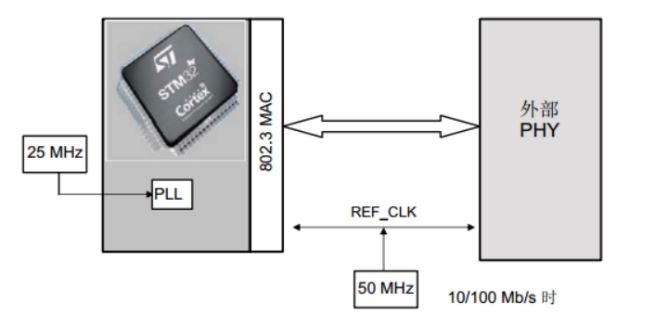

③RMII接口

介质独立接口 (RMII) 规范降低了 10/100 Mbit/s 下微控制器以太网外设与外部 PHY 间的 引脚数。 RMII 规范将引脚 数减少为 7 个(引脚数减少 62.5%)。不过RMII接口的参考时钟必须是50MHZ!

RMII时钟源: 通常使用50MHZ的时钟驱动PHY或使用嵌入式PLL生成50MHZ频率来驱动PHY。

浙公网安备 33010602011771号

浙公网安备 33010602011771号