RISC介绍

CPU中包含了控制部件和运算部件,即中央处理器。1971 年,Intel 将运算器和控制器集成在一个芯片上,称为 4004 微处理器,这标志着 CPU 的诞生。到了 1978 年,开发的 8086 处理器奠定了 X86 指令集架构。此后,8086 系列处理器被广泛应用于个人计算机以及高性能服务器中。

CPU的工作流程分为以下五个阶段:取指、指令译码、执行指令、访存读取数据和结果回写

指令和数据统一存储在内存中,数据与指令需要从统一的存储空间中存取,经由共同的总线传输,无法并行读取数据和指令。这就是大名鼎鼎的冯诺依曼体系结构。

CPU运行程序会循环执行上述五个阶段,它既是程序指令的执行者,有被程序中相关的指令所驱动,最后实现了相关的计算功能。这些功能再组合成相应算法,然后由多种算法共同实现功能强大的软件。

CPU的工作离不开指令,指令集架构就显的尤其重要。有CISC(复杂指令集)和RISC(精简指令集)

CISC

CPU 的指令集越丰富、每个指令完成的功能越多,为该 CPU 编写程序就越容易,因为每一项简单或复杂的任务都有一条对应的指令,不需要软件开发人员写大量的指令。这就是复杂指令集计算机体系结构——CISC。

CISC 的典型代表就是 x86 体系架构,x86 CPU 中包含大量复杂指令集,比如串操作指令、循环控制指令、进程任务切换指令等,还有一些数据传输指令和数据运算指令,它们包含了丰富的内存寻址操作。

CISC 的优势在于,用少量的指令就能实现非常多的功能,程序自身大小也会下降,减少内存空间的占用。但凡事有利就有弊,这些复杂指令集,包含的指令数量多而且功能复杂。

RISC

20 世纪 80 年代,编译器技术的发展,导致各种高级编程语言盛行。这些高级语言编译器生成的低级代码,比程序员手写的低级代码高效得多,使用的也是常用的几十条指令。 最终导致人们开始向 CISC 的反方向思考,由此产生了** RISC——精简指令集计算机体系结构。**

正如它的名字一样,RISC 设计方案非常简约,通常有 20 多条指令的简化指令集。每条指令长度固定,由专用的加载和储存指令用于访问内存,减少了内存寻址方式,大多数运算指令只能访问操作寄存器。

而 CPU 中配有大量的寄存器,这些指令选取的都是工程中使用频率最高的指令。由于指令长度一致,功能单一,操作依赖于寄存器,这些特性使得 CPU 指令预取、分支预测、指令流水线等部件的效能大大发挥,几乎一个时钟周期能执行多条指令。

RISC 的代表产品是 ARM 和 RISC-V。

用 RISC-V 来命名该指令集架构,有两层意思:RISC-V 中的“V”,一方面代表第 5 代 RISC;另一方面,“V”取“ Variation”之意,代表变化。

RISC-V是什么

RISC-V 是一套开放许可证书、免费的、由基金会维护的、一个整数运算指令集外加多个扩展指令集的 CPU 架构规范

指令集命名方式

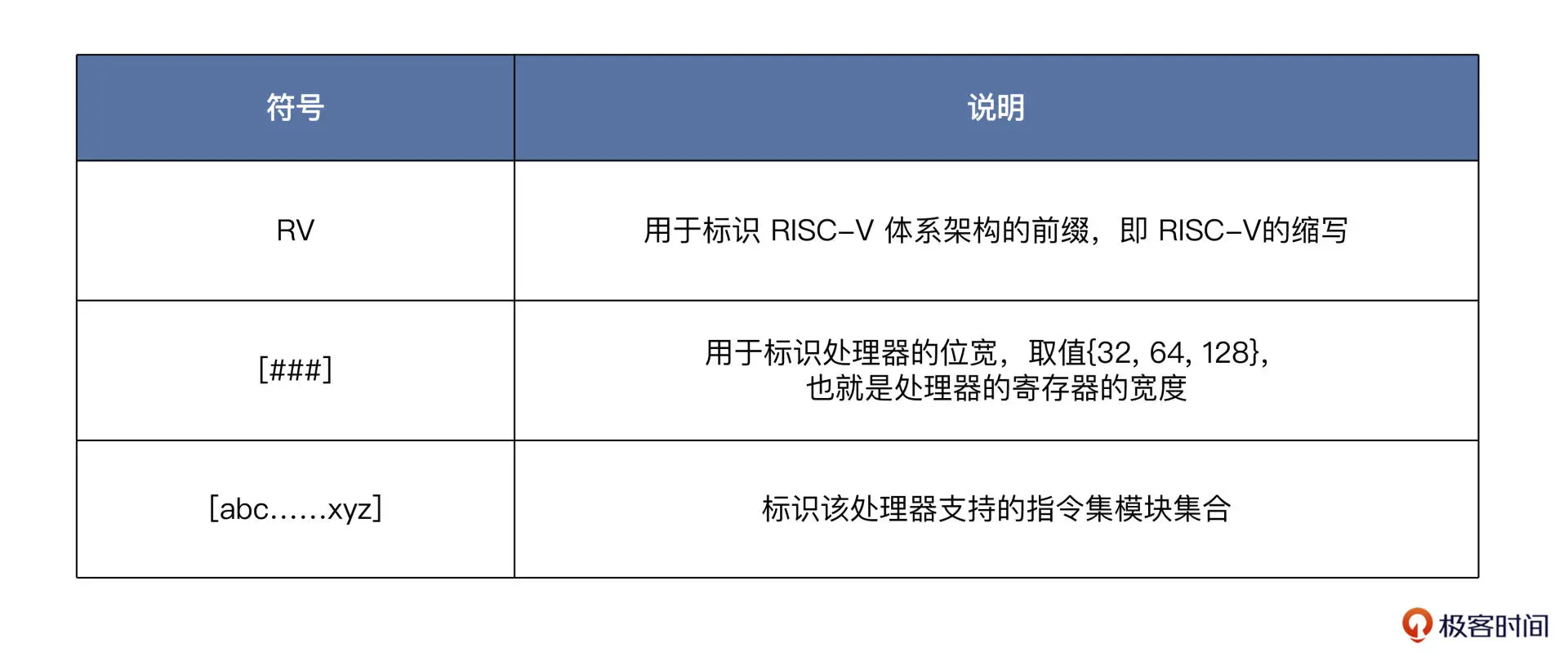

RISC-V 规范中有相关定义说明,以 RV 为前缀,然后是位宽,最后是代表指令集的字母集合,具体形式如下:

RV[###][abc……xyz]

用表格为你说明一下这个格式,如下所示:

举个例子,比如:RV64IMAC,就表示 64 位的 RISC-V,支持整数指令、乘除法指令、原子指令和压缩指令。

指令集模块

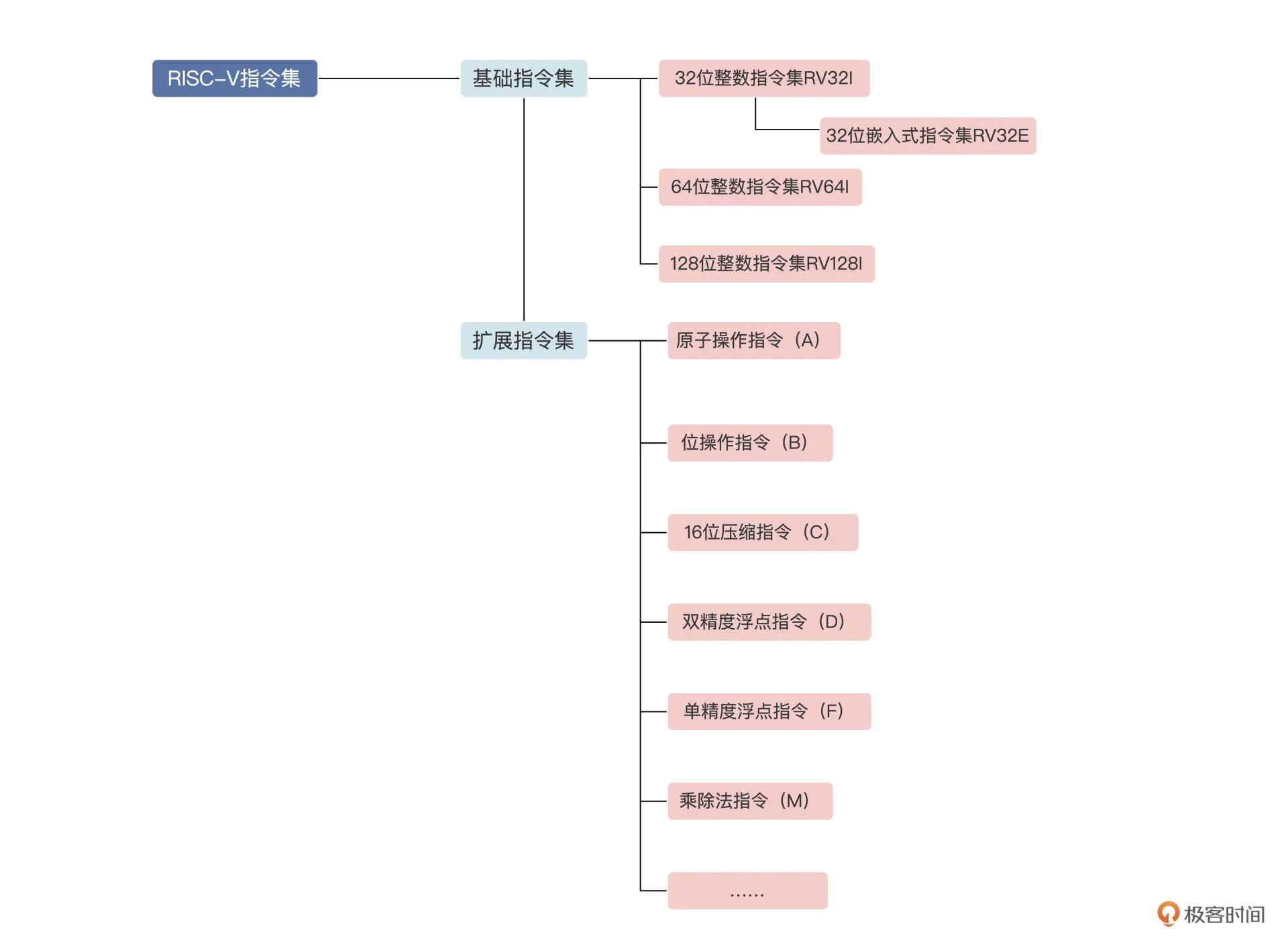

指令集是一款 CPU 架构的主要组成部分,是 CPU 和上层软件交互的核心,也是 CPU 主要功能的体现。

RISC-V 规范只定义了 CPU 需要包含基础整形操作指令,如整型的储存、加载、加减、逻辑、移位、分支等。其它的指令称为可选指令或者用户扩展指令,比如乘、除、取模、单精度浮点、双精度浮点、压缩、原子指令等,这些都是扩展指令。扩展指令需要芯片工程师结合功能需求自定义。

所以 RISC-V 采用的是模块化的指令集,易于扩展、组装。它适应于不同的应用场景,可以降低 CPU 的实现成本。

下图展示的是 RISC-V 指令集的各个组成部分:

RISC-V寄存器

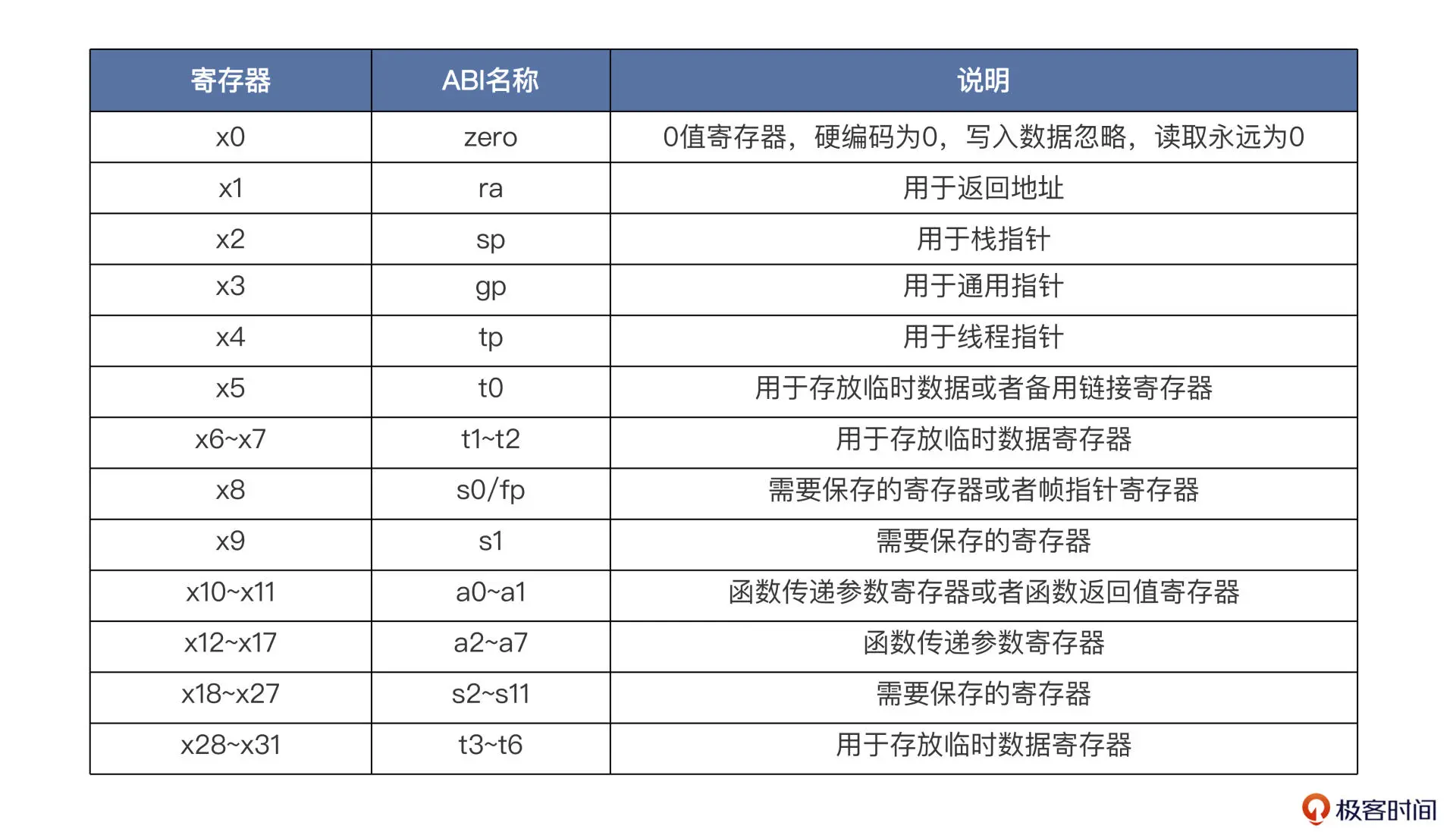

指令的操作数是来源于寄存器,精简指令集架构的 CPU,都会提供大量的寄存器,RISC-V 当然也不例外。RISC-V 的规范定义了 32 个通用寄存器以及一个 PC 寄存器,这对于 RV32I、RV64I、RV128I 指令集都是一样的,只是寄存器位宽不一样。

如果实现支持 F/D 扩展指令集的 CPU,则需要额外支持 32 个浮点寄存器。而如果实现只支持 RV32E 指令集的嵌入式 CPU,则可以将 32 个通用寄存器缩减为 16 个通用寄存器。

不常用的 32 个浮点寄存器并没有列在这张表里。表中的 ABI 名称,即应用程序二进制接口,你可以理解为寄存器别名,高级语言在生成汇编语言的时候会用到它们。

比如 C 语言处理函数调用时,用哪些寄存器传递参数、返回值,调用者应该保护哪些寄存器,用什么寄存器管理栈帧等等。

定义好ABI标准,就能在语言间相互调用函数了,比如C语言函数调用汇编语言函数。

RISC-V 特权级

不同的特权级能访问的系统资源不同,高特权级能访问低特权级的资源,反之则不行。RISC-V 的规范文档定义了四个特权级别(privilege level),特权等级由高到低排列,如下表所示

一个 RISC-V 硬件线程(hart),相当于一个 CPU 内的独立的可执行核心,在任一时刻,只能运行在某一个特权级上,这个特权级由 CSR(控制和状态寄存器)指定和配置。

具体分级如下:

-

1.机器特权级(M):RISC-V 中 hart 可以执行的最高权限模式。在 M 模式下运行的 hart,对内存、I/O 和一些必要的底层功能(启动和系统配置)有着完全的控制权。因此,它是唯一一个所有标准 RISC-V CPU 都必须实现的权限级。实际上,普通的 RISC-V 微控制器仅支持机器特权级。

-

- 虚拟机监视特权级(H):为了支持虚拟机监视器而定义的特权级。

-

- 管理员特权级(S):主要用于支持现代操作系统,如 Linux、FreeBSD 和 Windows。

-

- 用户应用特权级(U):用于运行应用程序,同样也适用于嵌入式系统。

特权级的作用:

有了特权级的存在,就给指令加上了权力,从而去控制用指令编写的程序。应用程序只能干应用程序该干的事情,不能越权操作。操作系统则拥有更高的权力,能对系统的资源进行管理。

RISC-V 因何流行:其优势:一是 RISC-V 完全开放,二是 RISC-V 指令简单,三是 RISC-V 实行模块化设计,易于扩展。

为什么说 RISC-V 很简单?RISC-V 提供了一个非常强大且开放的精简指令集架构,只有 32 个通用寄存器、40 多条常用指令、4 个特权级。如果需要其它功能,则要进行指令集的扩展,单核心的规范文档才不到 300 页,一个人在一周之内就能搞清楚。

RISC-V 的模块化设计。RISC-V 虽然简单,但这并不意味着功能的缺失。通过模块化的设计,就能实现对各种功能组件的剪裁和扩展。

正是因为 RISC-V 开放、简单和模块化这三大特点,硬件工程师和软件工程师才能站在巨人的肩膀上开发,自由地调用和组装功能模块,快速去实现特定业务场景下的芯片需求

浙公网安备 33010602011771号

浙公网安备 33010602011771号