【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART5--实验四

4.实验四:计数器

Part I :16位计数器

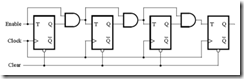

图4.1中所示的电路是使用了4个T触发器的4位同步计数器。这个计数器在其使能信号有效时每当到来一个上升沿时即计数一次,当清零信号有效时,计数器结果清零。试设计一个同类型的16位计数器。

图4.1 四位同步计数器

执行以下步骤:

1使用图4.1中给出的结构来写出一段16位计数器的VHDL代码,并编译。

2仿真工程来证实其正确性。

3扩展VHDL文件,使用按钮KEY0作为时钟输入,使用开关SW1和SW0作为使能信号和清零信号,使用7段码显示器HEX3—0来显示结果。进行必要的引脚分配并编译工程。

4在DE2-115开发板上实现这个电路,并通过拨动开关来测试电路功能。

5实现一个4位计数器并用Quartus II的RTL观测器来研究Quartus II是如何来综合该电路的。

Part 1代码:

counter_16:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY counter_16 IS

6

7 PORT (

8

9 en : IN STD_LOGIC;

10

11 clk : IN STD_LOGIC;

12

13 clr : IN STD_LOGIC;

14

15 Qout : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)

16

17 );

18

19 END counter_16;

20

21 ARCHITECTURE trans OF counter_16 IS

22

23 COMPONENT t_ff IS

24

25 PORT (

26

27 t : IN STD_LOGIC;

28

29 clk : IN STD_LOGIC;

30

31 rst_n : IN STD_LOGIC;

32

33 qq : OUT STD_LOGIC

34

35 );

36

37 END COMPONENT;

38

39 SIGNAL q : STD_LOGIC_VECTOR(15 DOWNTO 0);

40

41 -- X-HDL generated signals

42

43 SIGNAL xhdl1 : STD_LOGIC;

44

45 SIGNAL xhdl2 : STD_LOGIC;

46

47 SIGNAL xhdl3 : STD_LOGIC;

48

49 SIGNAL xhdl4 : STD_LOGIC;

50

51 SIGNAL xhdl5 : STD_LOGIC;

52

53 SIGNAL xhdl6 : STD_LOGIC;

54

55 SIGNAL xhdl7 : STD_LOGIC;

56

57 SIGNAL xhdl8 : STD_LOGIC;

58

59 SIGNAL xhdl9 : STD_LOGIC;

60

61 SIGNAL xhdl10 : STD_LOGIC;

62

63 SIGNAL xhdl11 : STD_LOGIC;

64

65 SIGNAL xhdl12 : STD_LOGIC;

66

67 SIGNAL xhdl13 : STD_LOGIC;

68

69 SIGNAL xhdl14 : STD_LOGIC;

70

71 SIGNAL xhdl15 : STD_LOGIC;

72

73 BEGIN

74

75 u0 : t_ff

76

77 PORT MAP (

78

79 en,

80

81 clk,

82

83 clr,

84

85 q(0)

86

87 );

88

89 xhdl1 <= en AND q(0);

90

91 u1 : t_ff

92

93 PORT MAP (

94

95 xhdl1,

96

97 clk,

98

99 clr,

100

101 q(1)

102

103 );

104

105 xhdl2 <= en AND q(0) AND q(1);

106

107 u2 : t_ff

108

109 PORT MAP (

110

111 xhdl2,

112

113 clk,

114

115 clr,

116

117 q(2)

118

119 );

120

121 xhdl3 <= en AND q(0) AND q(1) AND q(2);

122

123 u3 : t_ff

124

125 PORT MAP (

126

127 xhdl3,

128

129 clk,

130

131 clr,

132

133 q(3)

134

135 );

136

137 xhdl4 <= en AND q(0) AND q(1) AND q(2) AND q(3);

138

139 u4 : t_ff

140

141 PORT MAP (

142

143 xhdl4,

144

145 clk,

146

147 clr,

148

149 q(4)

150

151 );

152

153 xhdl5 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4);

154

155 u5 : t_ff

156

157 PORT MAP (

158

159 xhdl5,

160

161 clk,

162

163 clr,

164

165 q(5)

166

167 );

168

169 xhdl6 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5);

170

171 u6 : t_ff

172

173 PORT MAP (

174

175 xhdl6,

176

177 clk,

178

179 clr,

180

181 q(6)

182

183 );

184

185 xhdl7 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6);

186

187 u7 : t_ff

188

189 PORT MAP (

190

191 xhdl7,

192

193 clk,

194

195 clr,

196

197 q(7)

198

199 );

200

201 xhdl8 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6) AND q(7);

202

203 u8 : t_ff

204

205 PORT MAP (

206

207 xhdl8,

208

209 clk,

210

211 clr,

212

213 q(8)

214

215 );

216

217 xhdl9 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6) AND q(7) AND q(8);

218

219 u9 : t_ff

220

221 PORT MAP (

222

223 xhdl9,

224

225 clk,

226

227 clr,

228

229 q(9)

230

231 );

232

233 xhdl10 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6) AND q(7) AND q(8) AND q(9);

234

235 u10 : t_ff

236

237 PORT MAP (

238

239 xhdl10,

240

241 clk,

242

243 clr,

244

245 q(10)

246

247 );

248

249 xhdl11 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6) AND q(7) AND q(8) AND q(9) AND q(10);

250

251 u11 : t_ff

252

253 PORT MAP (

254

255 xhdl11,

256

257 clk,

258

259 clr,

260

261 q(11)

262

263 );

264

265 xhdl12 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6) AND q(7) AND q(8) AND q(9) AND q(10) AND q(11);

266

267 u12 : t_ff

268

269 PORT MAP (

270

271 xhdl12,

272

273 clk,

274

275 clr,

276

277 q(12)

278

279 );

280

281 xhdl13 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6) AND q(7) AND q(8) AND q(9) AND q(10) AND q(11) AND q(12);

282

283 u13 : t_ff

284

285 PORT MAP (

286

287 xhdl13,

288

289 clk,

290

291 clr,

292

293 q(13)

294

295 );

296

297 xhdl14 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6) AND q(7) AND q(8) AND q(9) AND q(10) AND q(11) AND q(12) AND q(13);

298

299 u14 : t_ff

300

301 PORT MAP (

302

303 xhdl14,

304

305 clk,

306

307 clr,

308

309 q(14)

310

311 );

312

313 xhdl15 <= en AND q(0) AND q(1) AND q(2) AND q(3) AND q(4) AND q(5) AND q(6) AND q(7) AND q(8) AND q(9) AND q(10) AND q(11) AND q(12) AND q(13) AND q(14);

314

315 u15 : t_ff

316

317 PORT MAP (

318

319 xhdl15,

320

321 clk,

322

323 clr,

324

325 q(15)

326

327 );

328

329 Qout <= q;

330

331 END trans;

t_ff:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY t_ff IS

6

7 PORT (

8

9 t : IN STD_LOGIC;

10

11 clk : IN STD_LOGIC;

12

13 rst_n : IN STD_LOGIC;

14

15 qq : OUT STD_LOGIC

16

17 );

18

19 END t_ff;

20

21 ARCHITECTURE trans OF t_ff IS

22

23 -- Declare intermediate signals for referenced outputs

24

25 SIGNAL q_xhdl0 : STD_LOGIC;

26

27 BEGIN

28

29 -- Drive referenced outputs

30

31 qq <= q_xhdl0;

32

33 PROCESS (clk)

34

35 BEGIN

36

37 IF (clk'EVENT AND clk = '1') THEN

38

39 IF ((NOT(rst_n)) = '1') THEN

40

41 q_xhdl0 <= '0';

42

43 ELSE

44

45 IF (t = '1') THEN

46

47 q_xhdl0 <= NOT(q_xhdl0);

48

49 ELSE

50

51 q_xhdl0 <= q_xhdl0;

52

53 END IF;

54

55 END IF;

56

57 END IF;

58

59 END PROCESS;

60

61 END trans;

62

63 led_display:

64

65 LIBRARY ieee;

66

67 USE ieee.std_logic_1164.all;

68

69 ENTITY led_display IS

70

71 PORT (

72

73 idig : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

74

75 oseg : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

76

77 );

78

79 END led_display;

80

81 ARCHITECTURE trans OF led_display IS

82

83 BEGIN

84

85 PROCESS (idig)

86

87 BEGIN

88

89 CASE idig IS

90

91 WHEN "0001" =>

92

93 oseg <= "1111001";

94

95 WHEN "0010" =>

96

97 oseg <= "0100100";

98

99 WHEN "0011" =>

100

101 oseg <= "0110000";

102

103 WHEN "0100" =>

104

105 oseg <= "0011001";

106

107 WHEN "0101" =>

108

109 oseg <= "0010010";

110

111 WHEN "0110" =>

112

113 oseg <= "0000010";

114

115 WHEN "0111" =>

116

117 oseg <= "1111000";

118

119 WHEN "1000" =>

120

121 oseg <= "0000000";

122

123 WHEN "1001" =>

124

125 oseg <= "0011000";

126

127 WHEN "1010" =>

128

129 oseg <= "0001000";

130

131 WHEN "1011" =>

132

133 oseg <= "0000011";

134

135 WHEN "1100" =>

136

137 oseg <= "1000110";

138

139 WHEN "1101" =>

140

141 oseg <= "0100001";

142

143 WHEN "1110" =>

144

145 oseg <= "0000110";

146

147 WHEN "1111" =>

148

149 oseg <= "0001110";

150

151 WHEN OTHERS =>

152

153 oseg <= "1000000";

154

155 END CASE;

156

157 END PROCESS;

158

159 END trans;

lab4_part1顶层:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY lab4_part1 IS

6

7 PORT (

8

9 KEY : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

10

11 SW : IN STD_LOGIC_VECTOR(1 DOWNTO 0);

12

13 HEX3 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

14

15 HEX2 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

16

17 HEX1 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

18

19 HEX0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

20

21 );

22

23 END lab4_part1;

24

25 ARCHITECTURE trans OF lab4_part1 IS

26

27 COMPONENT counter_16 IS

28

29 PORT (

30

31 en : IN STD_LOGIC;

32

33 clk : IN STD_LOGIC;

34

35 clr : IN STD_LOGIC;

36

37 Qout : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)

38

39 );

40

41 END COMPONENT;

42

43 COMPONENT led_display IS

44

45 PORT (

46

47 idig : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

48

49 oseg : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

50

51 );

52

53 END COMPONENT;

54

55 SIGNAL q : STD_LOGIC_VECTOR(15 DOWNTO 0);

56

57 -- Declare intermediate signals for referenced outputs

58

59 SIGNAL HEX3_xhdl3 : STD_LOGIC_VECTOR(6 DOWNTO 0);

60

61 SIGNAL HEX2_xhdl2 : STD_LOGIC_VECTOR(6 DOWNTO 0);

62

63 SIGNAL HEX1_xhdl1 : STD_LOGIC_VECTOR(6 DOWNTO 0);

64

65 SIGNAL HEX0_xhdl0 : STD_LOGIC_VECTOR(6 DOWNTO 0);

66

67 BEGIN

68

69 -- Drive referenced outputs

70

71 HEX3 <= HEX3_xhdl3;

72

73 HEX2 <= HEX2_xhdl2;

74

75 HEX1 <= HEX1_xhdl1;

76

77 HEX0 <= HEX0_xhdl0;

78

79 z0 : counter_16

80

81 PORT MAP (

82

83 SW(1),

84

85 KEY(0),

86

87 SW(0),

88

89 q

90

91 );

92

93 H0 : led_display

94

95 PORT MAP (

96

97 q(3 DOWNTO 0),

98

99 HEX0_xhdl0

100

101 );

102

103 H1 : led_display

104

105 PORT MAP (

106

107 q(7 DOWNTO 4),

108

109 HEX1_xhdl1

110

111 );

112

113 H2 : led_display

114

115 PORT MAP (

116

117 q(11 DOWNTO 8),

118

119 HEX2_xhdl2

120

121 );

122

123 H3 : led_display

124

125 PORT MAP (

126

127 q(15 DOWNTO 12),

128

129 HEX3_xhdl3

130

131 );

132

133 END trans;

仿真波形如下:

Part II :思考题

1.)简化VHDL代码,使计数器的VHDL描述基于以下语句:

Q<=Q+1;

编制一个16位计数器,与之前的计数器比较所需的LE和最大允许的频率。使用RTL观测器来观察电路结构和第一部分中电路的区别。

2.)使用一个参数化模型库中的LPM模块来实现16位计数器,选择与以上设计一致的LPM设置,拥有使能和同步清零信号。比较这个版本的计数器与之前的设计。

3)设计一个在7段码显示器HEX0上连续闪烁数字0—9的的电路。每一个数字应该大概保持一秒钟。使用一个计数器来确定这一秒钟的间隔。这个计数器通过DE2-115上的50MHZ的时钟信号来增加计数。不要使用其他时钟信号,确保电路中所有的触发器直接由上述的50MHZ时钟信号驱动。

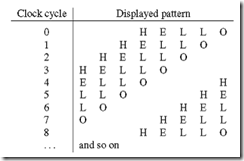

4.)设计并实现一个在HEX7—0上显示单词HELLO的电路。并使单词每间歇1秒就从右往左移动一次,预期显示如图4.2所示。

图4.2