【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART3--实验二

2.实验二:二进制与BCD码的转换及显示

本节实验主要实现二进制数字到十进制数字的转换以及BCD码的加法。

Part I :二进制数字的显示

将开关SW15--0所设定的值显示在7段码显示器HEX3--HEX0上,即将开关SW15--12,SW11--8,SW7--4和SW3--0设置的值分别显示在HEX3,HEX2,HEX1和HEX0上。该电路应能显示0---9的数字,并且对于1010—1111的输入值不作显示。

Part 1代码:

七段码显示模块:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY led_display IS

6

7 PORT (

8

9 s : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

10

11 seg : OUT STD_LOGIC_VECTOR(0 TO 6)

12

13 );

14

15 END led_display;

16

17 ARCHITECTURE trans OF led_display IS

18

19 BEGIN

20

21 seg(6) <= (NOT(s(3)) AND NOT(s(2)) AND NOT(s(1))) OR (s(2) AND s(1) AND s(0));

22

23 seg(5) <= (NOT(s(3)) AND NOT(s(2)) AND s(0)) OR ((NOT(s(2)) AND s(1)) OR (s(1) AND s(0)));

24

25 seg(4) <= s(0) OR (s(2) AND NOT(s(1)));

26

27 seg(3) <= (NOT(s(3)) AND NOT(s(2)) AND NOT(s(1)) AND s(0)) OR (s(2) AND NOT(s(1)) AND NOT(s(0))) OR (s(2) AND s(1) AND s(0));

28

29 seg(2) <= NOT(s(2)) AND s(1) AND NOT(s(0));

30

31 seg(1) <= (s(2) AND NOT(s(1)) AND s(0)) OR (s(2) AND s(1) AND NOT(s(0)));

32

33 seg(0) <= (s(2) AND NOT(s(1)) AND NOT(s(0))) OR (NOT(s(3)) AND NOT(s(2)) AND NOT(s(1)) AND s(0));

34

35 END trans;

顶层文件:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY lab2_part1 IS

6

7 PORT (

8

9 HEX3 : OUT STD_LOGIC_VECTOR(0 TO 6);

10

11 HEX2 : OUT STD_LOGIC_VECTOR(0 TO 6);

12

13 HEX1 : OUT STD_LOGIC_VECTOR(0 TO 6);

14

15 HEX0 : OUT STD_LOGIC_VECTOR(0 TO 6);

16

17 SW : IN STD_LOGIC_VECTOR(15 DOWNTO 0)

18

19 );

20

21 END lab2_part1;

22

23 ARCHITECTURE trans OF lab2_part1 IS

24

25 COMPONENT led_display IS

26

27 PORT (

28

29 s : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

30

31 seg : OUT STD_LOGIC_VECTOR(0 TO 6)

32

33 );

34

35 END COMPONENT;

36

37 BEGIN

38

39 H3 : led_display

40

41 PORT MAP (

42

43 SW(15 DOWNTO 12),

44

45 HEX3

46

47 );

48

49 H2 : led_display

50

51 PORT MAP (

52

53 SW(11 DOWNTO 8),

54

55 HEX2

56

57 );

58

59 H1 : led_display

60

61 PORT MAP (

62

63 SW(7 DOWNTO 4),

64

65 HEX1

66

67 );

68

69 H0 : led_display

70

71 PORT MAP (

72

73 SW(3 DOWNTO 0),

74

75 HEX0

76

77 );

78

79 END trans;

仿真波形如下:

Part II :

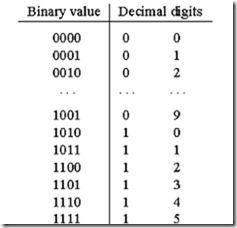

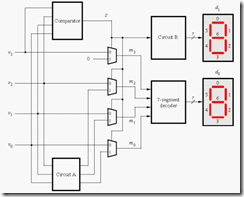

将一个4位2进制数V=v3v2v1v0转换为与之等价的两位十进制数D=d1d0。转换表格如表2.1所示。图2.1所示的是该设计的局部电路,它包含一个比较器,用来检测V的值是否大于9,并且通过比较器的输出来控制7段码显示器的显示。通过创建一个VHDL实体来完成这个电路设计。该VHDL实体应该包含比较器、多路选择器、和电路A(这里并不包含电路B或是7段译码器)。该VHDL实体应有4位输入V,4位输出M和输出z。

表2.1 2—10进制转换表

图2.2 2—10进制转换电路的局部设计

Part 2代码:

Circuita:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY circuita IS

6

7 PORT (

8

9 v : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

10

11 a : OUT STD_LOGIC_VECTOR(2 DOWNTO 0)

12

13 );

14

15 END circuita;

16

17 ARCHITECTURE trans OF circuita IS

18

19 BEGIN

20

21 a(2) <= v(2) AND v(1);

22

23 a(1) <= v(2) AND NOT(v(1));

24

25 a(0) <= (v(1) AND v(0)) OR (v(2) AND v(0));

26

27 END trans;

28

29 Circuitb:

30

31 LIBRARY ieee;

32

33 USE ieee.std_logic_1164.all;

34

35 ENTITY circuitb IS

36

37 PORT (

38

39 z : IN STD_LOGIC;

40

41 seg : OUT STD_LOGIC_VECTOR(0 TO 6)

42

43 );

44

45 END circuitb;

46

47 ARCHITECTURE trans OF circuitb IS

48

49 BEGIN

50

51 seg(6) <= '1';

52

53 seg(5) <= z;

54

55 seg(4) <= z;

56

57 seg(3) <= z;

58

59 seg(2) <= '0';

60

61 seg(1) <= '0';

62

63 seg(0) <= z;

64

65 END trans;

Comparator:

1 LIBRARY IEEE;

2

3 USE IEEE.STD_LOGIC_1164.ALL;

4

5 USE IEEE.STD_LOGIC_UNSIGNED.ALL;

6

7 USE IEEE.STD_LOGIC_ARITH.ALL;

8

9 ENTITY comparator IS

10

11 PORT (A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

12

13 Z:OUT STD_LOGIC);

14

15 END ENTITY comparator;

16

17 ARCHITECTURE ART OF comparator IS

18

19 BEGIN

20

21 PROCESS(A)IS

22

23 VARIABLE B:BIT_VECTOR(3 downto 0);

24

25 BEGIN

26

27 IF(A>"1001")THEN

28

29 Z<='1';

30

31 ELSE Z<='0';

32

33 END IF;

34

35 END PROCESS;

36

37 END ARCHITECTURE ART;

mux_2to1:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY mux_2to1 IS

6

7 PORT (

8

9 a : IN STD_LOGIC;

10

11 b : IN STD_LOGIC;

12

13 s : IN STD_LOGIC;

14

15 m : OUT STD_LOGIC

16

17 );

18

19 END mux_2to1;

20

21 ARCHITECTURE trans OF mux_2to1 IS

22

23 BEGIN

24

25 m <= b WHEN (s = '1') ELSE

26

27 a;

28

29 END trans;

mux_4b_2to1:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY mux_4b_2to1 IS

6

7 PORT (

8

9 x : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

10

11 y : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

12

13 s : IN STD_LOGIC;

14

15 m : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

16

17 );

18

19 END mux_4b_2to1;

20

21 ARCHITECTURE trans OF mux_4b_2to1 IS

22

23 COMPONENT mux_2to1 IS

24

25 PORT (

26

27 a : IN STD_LOGIC;

28

29 b : IN STD_LOGIC;

30

31 s : IN STD_LOGIC;

32

33 m : OUT STD_LOGIC

34

35 );

36

37 END COMPONENT;

38

39 -- Declare intermediate signals for referenced outputs

40

41 SIGNAL m_xhdl2 : STD_LOGIC_VECTOR(3 DOWNTO 0);

42

43 BEGIN

44

45 -- Drive referenced outputs

46

47 m <= m_xhdl2;

48

49 u3 : mux_2to1

50

51 PORT MAP (

52

53 x(3),

54

55 y(3),

56

57 s,

58

59 m_xhdl2(3)

60

61 );

62

63 u2 : mux_2to1

64

65 PORT MAP (

66

67 x(2),

68

69 y(2),

70

71 s,

72

73 m_xhdl2(2)

74

75 );

76

77 u1 : mux_2to1

78

79 PORT MAP (

80

81 x(1),

82

83 y(1),

84

85 s,

86

87 m_xhdl2(1)

88

89 );

90

91 u0 : mux_2to1

92

93 PORT MAP (

94

95 x(0),

96

97 y(0),

98

99 s,

100

101 m_xhdl2(0)

102

103 );

104

105 END trans;

led_display:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY led_display IS

6

7 PORT (

8

9 s : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

10

11 seg : OUT STD_LOGIC_VECTOR(0 TO 6)

12

13 );

14

15 END led_display;

16

17 ARCHITECTURE trans OF led_display IS

18

19 BEGIN

20

21 seg(6) <= (NOT(s(3)) AND NOT(s(2)) AND NOT(s(1))) OR (s(2) AND s(1) AND s(0));

22

23 seg(5) <= (NOT(s(3)) AND NOT(s(2)) AND s(0)) OR ((NOT(s(2)) AND s(1)) OR (s(1) AND s(0)));

24

25 seg(4) <= s(0) OR (s(2) AND NOT(s(1)));

26

27 seg(3) <= (NOT(s(3)) AND NOT(s(2)) AND NOT(s(1)) AND s(0)) OR (s(2) AND NOT(s(1)) AND NOT(s(0))) OR (s(2) AND s(1) AND s(0));

28

29 seg(2) <= NOT(s(2)) AND s(1) AND NOT(s(0));

30

31 seg(1) <= (s(2) AND NOT(s(1)) AND s(0)) OR (s(2) AND s(1) AND NOT(s(0)));

32

33 seg(0) <= (s(2) AND NOT(s(1)) AND NOT(s(0))) OR (NOT(s(3)) AND NOT(s(2)) AND NOT(s(1)) AND s(0));

34

35 END trans;

lab2_part2顶层文件:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY lab2_part2 IS

6

7 PORT (

8

9 SW : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

10

11 HEX1 : OUT STD_LOGIC_VECTOR(0 TO 6);

12

13 HEX0 : OUT STD_LOGIC_VECTOR(0 TO 6)

14

15 );

16

17 END lab2_part2;

18

19 ARCHITECTURE trans OF lab2_part2 IS

20

21 COMPONENT led_display IS

22

23 PORT (

24

25 s : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

26

27 seg : OUT STD_LOGIC_VECTOR(0 TO 6)

28

29 );

30

31 END COMPONENT;

32

33 COMPONENT comparator IS

34

35 PORT (A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

36

37 Z:OUT STD_LOGIC);

38

39 END COMPONENT;

40

41 COMPONENT circuita IS

42

43 PORT (

44

45 v : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

46

47 a : OUT STD_LOGIC_VECTOR(2 DOWNTO 0)

48

49 );

50

51 END COMPONENT;

52

53 COMPONENT circuitb IS

54

55 PORT (

56

57 z : IN STD_LOGIC;

58

59 seg : OUT STD_LOGIC_VECTOR(0 TO 6)

60

61 );

62

63 END COMPONENT;

64

65 COMPONENT mux_4b_2to1 IS

66

67 PORT (

68

69 x : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

70

71 y : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

72

73 s : IN STD_LOGIC;

74

75 m : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

76

77 );

78

79 END COMPONENT;

80

81 SIGNAL z : STD_LOGIC;

82

83 SIGNAL a : STD_LOGIC_VECTOR(2 DOWNTO 0);

84

85 SIGNAL m : STD_LOGIC_VECTOR(3 DOWNTO 0);

86

87 SIGNAL xhdl3 : STD_LOGIC_VECTOR(3 DOWNTO 0);

88

89 -- Declare intermediate signals for referenced outputs

90

91 SIGNAL D1_xhdl1 : STD_LOGIC_VECTOR(0 TO 6);

92

93 SIGNAL D0_xhdl0 : STD_LOGIC_VECTOR(0 TO 6);

94

95 BEGIN

96

97 -- Drive referenced outputs

98

99 HEX1 <= D1_xhdl1;

100

101 HEX0 <= D0_xhdl0;

102

103 C : comparator

104

105 PORT MAP (

106

107 SW,

108

109 z

110

111 );

112

113 A1 : circuita

114

115 PORT MAP (

116

117 SW(2 DOWNTO 0),

118

119 a

120

121 );

122

123 xhdl3 <= ('0' & a);

124

125 M1 : mux_4b_2to1

126

127 PORT MAP (

128

129 SW,

130

131 xhdl3,

132

133 z,

134

135 m

136

137 );

138

139 B1 : circuitb

140

141 PORT MAP (

142

143 z,

144

145 D1_xhdl1

146

147 );

148

149 f1 : led_display

150

151 PORT MAP (

152

153 m,

154

155 D0_xhdl0

156

157 );

158

159 END trans;

仿真波形如下:

Part III :思考题

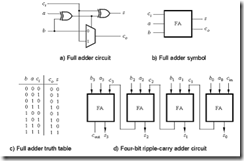

1.)图2.2所示的电路是一个全加器,它有3个输入:a,b和c,输出s和c0。图2.2.b和图2.2.c是全加器的电路符号和真值表。全加器产生的是两位二进制的和c0s=a+b+c。图2.2.d所示的是如何将4个全加器设计成4位二进制数的加法器。这个类型的电路通常被称为行波进位二进制计数器,因为进位信号从一个全加器传递到下一个全加器。写一段VHDL代码来实现如下图描述的电路。

图2.2 一个脉动进位二进制计数器电路

执行以下步骤:

1创建一个Quartus II 工程,先写一段全加器的VHDL代码,再写一个包含4个全加器的顶层VHDL实体。

2使用开关SW7—4和SW3—0来代表输入A和B,使用SW8来代表进位输入信号。将开关连接至对应的红色led上,将电路的输出,进位输出和结果输出连接至绿色led上。

3将必需的引脚分配包含进工程中,编译工程并将其下载至FPGA芯片。

4通过输入不同的输入信号A、B来测试电路是否正确工作。

2.)在之前的练习中我们讨论了2—10进制转换电路。用4位二进制数来代表十进制数,有时用这种方法来代表十进制数是很有用的。这种代表方法被称之为BCD码表示法。例如,十进制数59的BCD码位01011001。

你要设计一个实现两个BDC码数字加法的电路。电路的输入是两个BDC数字A和B,另外和一个低位来的进位Cin。电路的输出应为一个两位的BCD数字S1S0。要注意的是,使用这个电路产生的最大的和是S1S0=9+9+1=19。

执行以下步骤:

1创建一个新的Quartus II工程,应使用第三部分中4位加法电路来实现4位加法运算A+B。同第二部分的设计方法类似,设计出一个使得这个最大值为19的5位输出结果的电路转换成结果为两个BCD码S1S0。使用简单的VHDL赋值语句来说明所需要的逻辑函数。在VHDL代码中不能使用任何IF-ELSE,CASE,或类似的语句。

2使用开关SW7—4和SW3—0分别来作为输入A和B,使用SW8来作为低位进位。将开关连接至对应的红色led上,将电路由A+B产生的4位的和输出与进位输出连接至绿色led上。将A、B的BCD值显示在7段码显示器HEX6—4上,并将结果S1S0的值显示在HEX1—0上。

3因为该电路只处理BCD数字,因此要检测输入A、B是否大于9。若A、B大于9,则意味着发生错误,这时点亮一个绿色led灯LEDG8。

4将必需的引脚分配包含进工程中,编译工程并将其下载至FPGA芯片。

5通过输入不同的A、B、Cin的值来检测电路是否正常工作。

3.)设计一个可以对两个两位BCD数字相加的电路,即A1A0和B1B0相加产生一个3位BCD码的结果S2S1S0。使用思考题2中的电路来构建这个2位BCD码加法器。

执行以下步骤:

1使用开关SW15—8和SW7—0来代表2位BCD数字A1A0和B1B0。

A1A0的值要显示在7段码显示器HEX7—6上,同时,B1B0应显示在HEX5—4上。其和S2S1S0应显示在HEX2—0上。

2引脚包含进工程并编译工程。

3将文件下载进FPGA中并测试电路功能。

4.)在思考题3)中我们使用了两个思考题2中一位BCD码加法电路的VHDL实体来构建了一个两位BCD码加法器。另外一种描述两位BCD码加法器电路的算法与以下的伪代码类似:

1 T0 = A0 + B0

2 if(T0 > 9) then

3 Z0 = 10;

4 c1 = 1;

5 else

6 Z0 = 0;

7 c1 = 0;

8 end if

9 S0 = T0 − Z0

10 T1 = A1 + B1 + c1

11 if (T1 > 9) then

12 Z1 = 10;

13 c2 = 1;

14 else

15 Z1 = 0;

16 c2 = 0;

17 end if

18 S1 = T1 − Z1

19 S2 = c2

实现其中伪代码的电路是很明了的:第1,9,10和18行代表加法器,第2—8行和11—17行代表多路选择器,而检测状态T0,T1是否大于9则是由比较器来实现的。你要写出一段与之对应的VHDL代码。注意你可以用加法来代替9和18行中的减法运算。本部分实验的目的是检验依靠VHDL编译器通过使用IF-ELSE语句同VHDL中>和+运算来设计电路的效果。

执行以下步骤:

1创建一个新的Quartus II工程,使用与第五部分中相同的开关、灯和显示器连接。编译工程。

2使用Quartus II中RTL指示器工具来检测由你的VHDL编译后产生的电路。并将之与第五部分中的电路对比。

3将之下载至DE2开发板中,并通过设置不同的输入值来测试电路功能。

5.)设计一个综合电路,使其具有将一个6位二进制数转换为一个BCD码表示的2位十进制数。使用开关SW5—0作为输入,使用7段码显示器HEX1—0来显示十进制数。在DE2-115开发板上实现这个设计,并证明其功能。

浙公网安备 33010602011771号

浙公网安备 33010602011771号