【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART2--实验一

1.实验一:拨码开关、led灯和多路选择器

这个练习的目的是学习如何连接简单的输入、输出设备到一个FPGA芯片,并且用这些器件实现一个电路。我们将用DE2开发板上的switches SW17-0作为输入,用LED和7-segment displays作为输出。

这个实验包括6个部分,主要是组合逻辑电路和使用赋值语句。

Part I :点亮LED灯

Altera 的DE2系列开发板有18个拨动开关(toggle switch)和18个红色的LED。本部分要求,当你拨动一个开关(比如Switch 1),对应的LED就会亮(比如LEDR1)。

Part 1代码:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY lab1_part1 IS

6

7 PORT ( iSW : IN STD_LOGIC_VECTOR(17 DOWNTO 0);

8

9 oLEDR : OUT STD_LOGIC_VECTOR(17 DOWNTO 0));

10

11 END lab1_part1;

12

13 ARCHITECTURE Behavior OF lab1_part1 IS

14

15 BEGIN

16

17 oLEDR <= iSW;

18

19 END Behavior;

详细步骤:

1.建立工程,Quartus II --File--New project wizard(注意工程目录中不能出现中文字符,不能建立在桌面上);

2.新建HDL文件,Quartus II --File--New 选择 VHDL File ;

3.将上述代码输入至第2步中所建文件中;

4.编译;

5.仿真;

6.引脚锁定;

7.重新编译;

8.下载;

Part II:设计一个8位的2选1多路选择器

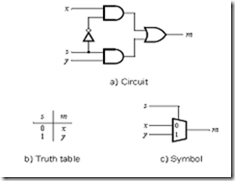

图2-1-a所示是一个通过选择信号S来控制的2-1的多路选择器。如果S=0时多路选择器的输出M就等于输入X,如果S=1时多路选择器的输出就等于Y。图2-1-b给出了这个多路选择器的真值表,图2-1-c是这个电路的符号。

图2-1 2-1多路选择器

这个多路选择器可以由下面的VHDL语句来描述:

m <= (NOT (s) AND x) OR (s AND y);

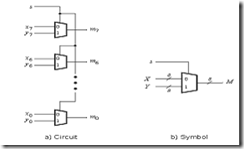

要求编写一个包含8个如上所示的赋值语句的VHDL实体,来描述图2-2-a所示的电路。 这个电路有两个8位输入X和Y,并且他的输出也是8位的M。如果S=0时,则M=X,或者M=1时,则M=Y。它的电路符号如图2-2-b所示,X,Y,M都是8位的。

图2-2一个8位的2—1多路选择器

详细步骤:(同part I)

附Part II 代码:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY lab1_part2 IS

6

7 PORT (

8

9 iSW : IN STD_LOGIC_VECTOR(17 DOWNTO 0);

10

11 oLEDR : OUT STD_LOGIC_VECTOR(17 DOWNTO 0);

12

13 oLEDG : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

14

15 );

16

17 END lab1_part2;

18

19 ARCHITECTURE Behavior OF lab1_part2 IS

20

21 component mux2to1

22

23 PORT (

24

25 s : IN STD_LOGIC;

26

27 x : IN STD_LOGIC;

28

29 y : IN STD_LOGIC;

30

31 m : OUT STD_LOGIC

32

33 );

34

35 END component;

36

37 signal s : std_logic ;

38

39 signal x : std_logic_vector( 7 downto 0 );

40

41 signal y : std_logic_vector( 7 downto 0 );

42

43 signal m : std_logic_vector( 7 downto 0 );

44

45 begin

46

47 s <= isw(17) ;

48

49 x <= isw(7 downto 0) ;

50

51 y <= isw(15 downto 8) ;

52

53 oledg <= m ;

54

55 oledr <= isw ;

56

57 mux2to1_0 : mux2to1

58

59 port map (

60

61 s => s ,

62

63 x => x(0) ,

64

65 y => y(0) ,

66

67 m => m(0)

68

69 );

70

71 mux2to1_1 : mux2to1

72

73 port map (

74

75 s => s ,

76

77 x => x(1) ,

78

79 y => y(1) ,

80

81 m => m(1)

82

83 );

84

85 mux2to1_2 : mux2to1

86

87 port map (

88

89 s => s ,

90

91 x => x(2) ,

92

93 y => y(2) ,

94

95 m => m(2)

96

97 );

98

99 mux2to1_3 : mux2to1

100

101 port map (

102

103 s => s ,

104

105 x => x(3) ,

106

107 y => y(3) ,

108

109 m => m(3)

110

111 );

112

113 mux2to1_4 : mux2to1

114

115 port map (

116

117 s => s ,

118

119 x => x(4) ,

120

121 y => y(4) ,

122

123 m => m(4)

124

125 );

126

127 mux2to1_5 : mux2to1

128

129 port map (

130

131 s => s ,

132

133 x => x(5) ,

134

135 y => y(5) ,

136

137 m => m(5)

138

139 );

140

141 mux2to1_6 : mux2to1

142

143 port map (

144

145 s => s ,

146

147 x => x(6) ,

148

149 y => y(6) ,

150

151 m => m(6)

152

153 );

154

155 mux2to1_7 : mux2to1

156

157 port map (

158

159 s => s ,

160

161 x => x(7) ,

162

163 y => y(7) ,

164

165 m => m(7)

166

167 );

168

169 END Behavior;

170

171 LIBRARY ieee;

172

173 USE ieee.std_logic_1164.all;

174

175 ENTITY mux2to1 IS

176

177 PORT (

178

179 s,x,y : IN STD_LOGIC;

180

181 m : OUT STD_LOGIC);

182

183 END mux2to1;

184

185 ARCHITECTURE Behavior OF mux2to1 IS

186

187 BEGIN

188

189 m <= ( not s and x ) or ( s and y );

190

191 END Behavior;

仿真波形如下:

Part III:设计一个3位的5选1多路选择器

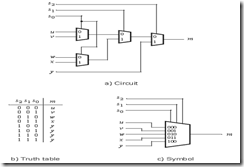

在这个部分讨论的是输出M是从5个输入U,V,W,X,Y中选择一个的5选1多路选择器。图2-3-a展示了我们如何用2选1多路选择器来构建一个5选1多路选择器。这个电路使用3位选择端s1,s2,s3,它的真值表如图2-3-b所示。图2-3-c表示了这个电路的符号。

图2-3 5-1多路选择器

详细步骤:(同part I)

附Part III 代码:

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY lab1_part3 IS

6

7 PORT (

8

9 iSW : IN STD_LOGIC_VECTOR(17 DOWNTO 0);

10

11 oLEDR : OUT STD_LOGIC_VECTOR(17 DOWNTO 0);

12

13 oLEDG : OUT STD_LOGIC_VECTOR(17 DOWNTO 0)

14

15 );

16

17 END lab1_part3;

18

19 ARCHITECTURE Behavior OF lab1_part3 IS

20

21 component mux2to1_3bit

22

23 PORT (

24

25 a : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

26

27 b : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

28

29 z : IN std_logic ;

30

31 c : OUT STD_LOGIC_VECTOR(2 DOWNTO 0)

32

33 );

34

35 END component;

36

37 signal u : std_logic_vector( 2 downto 0 );

38

39 signal v : std_logic_vector( 2 downto 0 );

40

41 signal w : std_logic_vector( 2 downto 0 );

42

43 signal x : std_logic_vector( 2 downto 0 );

44

45 signal y : std_logic_vector( 2 downto 0 );

46

47 signal s : std_logic_vector( 2 downto 0 );

48

49 signal m : std_logic_vector( 2 downto 0 );

50

51 signal c1 : std_logic_vector( 2 downto 0 );

52

53 signal c2 : std_logic_vector( 2 downto 0 );

54

55 signal c3 : std_logic_vector( 2 downto 0 );

56

57 BEGIN

58

59 s <= isw( 17 downto 15 ) ;

60

61 u <= isw( 14 downto 12 ) ;

62

63 v <= isw( 11 downto 9 ) ;

64

65 w <= isw( 8 downto 6 ) ;

66

67 x <= isw( 5 downto 3 ) ;

68

69 y <= isw( 2 downto 0 ) ;

70

71 oledr <= isw ;

72

73 oledg( 2 downto 0 ) <= m ;

74

75 mux2to1_3bit_0 : mux2to1_3bit

76

77 port map (

78

79 a => u ,

80

81 b => v ,

82

83 z => s(0),

84

85 c => c1

86

87 );

88

89 mux2to1_3bit_1 : mux2to1_3bit

90

91 port map (

92

93 a => w ,

94

95 b => x ,

96

97 z => s(0),

98

99 c => c2

100

101 );

102

103 mux2to1_3bit_2 : mux2to1_3bit

104

105 port map (

106

107 a => c1 ,

108

109 b => c2 ,

110

111 z => s(1),

112

113 c => c3

114

115 );

116

117 mux2to1_3bit_3 : mux2to1_3bit

118

119 port map (

120

121 a => c3 ,

122

123 b => y ,

124

125 z => s(2),

126

127 c => m

128

129 );

130

131 END Behavior;

132

133 LIBRARY ieee;

134

135 USE ieee.std_logic_1164.all;

136

137 ENTITY mux2to1_3bit IS

138

139 PORT ( a : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

140

141 b : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

142

143 z : IN std_logic ;

144

145 c : OUT STD_LOGIC_VECTOR(2 DOWNTO 0)

146

147 );

148

149 END mux2to1_3bit;

150

151 ARCHITECTURE Behavior OF mux2to1_3bit IS

152

153 component mux2to1

154

155 PORT ( s,x,y : IN STD_LOGIC;

156

157 m : OUT STD_LOGIC);

158

159 END component;

160

161 signal x : std_logic_vector( 2 downto 0 );

162

163 signal y : std_logic_vector( 2 downto 0 );

164

165 signal m : std_logic_vector( 2 downto 0 );

166

167 BEGIN

168

169 x <= a(2 downto 0) ;

170

171 y <= b(2 downto 0) ;

172

173 c <= m ;

174

175 mux2to1_0 : mux2to1

176

177 port map (

178

179 s => z ,

180

181 x => x(0) ,

182

183 y => y(0) ,

184

185 m => m(0)

186

187 );

188

189 mux2to1_1 : mux2to1

190

191 port map (

192

193 s => z ,

194

195 x => x(1) ,

196

197 y => y(1) ,

198

199 m => m(1)

200

201 );

202

203 mux2to1_2 : mux2to1

204

205 port map (

206

207 s => z ,

208

209 x => x(2) ,

210

211 y => y(2) ,

212

213 m => m(2)

214

215 );

216

217 END Behavior;

218

219 LIBRARY ieee;

220

221 USE ieee.std_logic_1164.all;

222

223 ENTITY mux2to1 IS

224

225 PORT ( s,x,y : IN STD_LOGIC;

226

227 m : OUT STD_LOGIC);

228

229 END mux2to1;

230

231 ARCHITECTURE Behavior OF mux2to1 IS

232

233 BEGIN

234

235 m <= ( not s and x ) or ( s and y );

236

237 END Behavior;

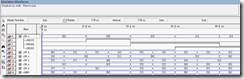

仿真波形如下:

part IV:设计一个7段显示控制器显示“HELLO”

这部分要求用一个7segment显示H、E、L、O。需要注意DE2上的七段码数码管是共阴极,对应的真值表见表 1 7-segment 译码真值表:

表 1 7-segment 译码真值表

|

c2c1c0 |

character |

7_segment |

|

000 |

H |

1001000 |

|

001 |

E |

0110000 |

|

010 |

L |

1110001 |

|

011 |

O |

0000001 |

|

100 |

blank |

1111111 |

|

101 |

|

|

|

110 |

|

|

|

111 |

|

|

附Part IV代码 :

1 LIBRARY ieee;

2

3 USE ieee.std_logic_1164.all;

4

5 ENTITY lab1_part4 IS

6

7 PORT ( iSW : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

8

9 oLEDR : OUT STD_LOGIC_VECTOR(2 DOWNTO 0);

10

11 oHEX0_d : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

12

13 );

14

15 END lab1_part4;

16

17 ARCHITECTURE Behavior OF lab1_part4 IS

18

19 begin

20

21 oledr <= isw ;

22

23 oHEX0_d(0) <= isw(2) or ( not isw(0) ) ;

24

25 oHEX0_d(1) <= isw(2) or ( isw(1) and ( not isw(0) )) or (( not isw(1)) and isw(0) ) ;

26

27 oHEX0_d(2) <= isw(2) or ( isw(1) and ( not isw(0) )) or (( not isw(1)) and isw(0) ) ;

28

29 oHEX0_d(3) <= isw(2) or (( not isw(1)) and ( not isw(0) )) ;

30

31 oHEX0_d(4) <= isw(2) ;

32

33 oHEX0_d(5) <= isw(2) ;

34

35 oHEX0_d(6) <= isw(2) or isw(1) ;

36

37 END Behavior;

仿真波形如下:

浙公网安备 33010602011771号

浙公网安备 33010602011771号