SDRAM-controller Nport terasic core详解

SDRAM-controller

Nport terasic core

详解

WG

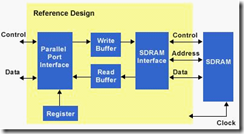

摘要:在构建嵌入式系统选择存储器时,无论在集成度、功耗、价格等方面,SDRAM都有非常明显的优势。SDRAM在使用时须有配合相应的controller,友晶科技在其DE系列FPGA开发板的配套demonstrations中也给出了相应的core,比如sdram_controller_2port、sdram_controller_4port等。此处不同的port数量是通过构建数目不同的buffer来实现的。虽然开辟了多条读写通道与SDRAM芯片通信,但实质上同一时刻仅有一条通道与SDRAM进行读或写。下面我们就来详细解释。

友晶的sdram_controller是将buffer(FIFO)、SDRAM接口、SDRAM时序控制等部分封装在了一起。

如上图所示,我们使用时,可以不用考虑刷新时间、潜伏时间等等SDRAM芯片相关的一些参数。只需要分配好地址空间和满足响应逻辑就可以使用了。

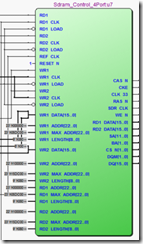

在sdram控制器对外的接口中主要分为两部分,一部分是与FPGA内部其他模块的交互信号,一部分是与外部SDRAM芯片的交互信号。

第一部分主要由:

1. WR1_ADDR 指的是 WR1 这个 Port 的起始位置(Starting address)。

2. WR1_DATA 即是该端口写入的数据。

3. WR1_MAX_ADDR 指的是 WR1 这个 Port 的結束位置(Ending address),每個address的数据宽度就是WR1 port的数据宽度16-bit。

4. WR1_LENGTH 即是Port內部都有一个FIFO做Buffer,当这个Buffer中数据到一定的数量的時候,控制器就会将Buffer中的数据写进SDRAM,这个数量就是WR1_LENGTH。

5. WR1_LOAD 就是刚刚提到的FIFO中的Asynchronous Clear信号,High的時候Clear。

6. WR即是写有效信号,在要写数据进SDRAM前将其拉高。

第二部分主要由:

Sa ba cs dqm等信号。这些信号是控制器与SDRAM芯片直接传送的。若是仅仅使用平台上的SDRAM,可以先不深究这些。

上图是DE2-70平台中某范例中使用到的SDRAM-controller,该控制器是4端口的,DE2-70平台上SDRAM是32M的,数据位宽为16bit,使用4端口可以增加带宽,有效利用资源。注意:4port是指读写各两个port。

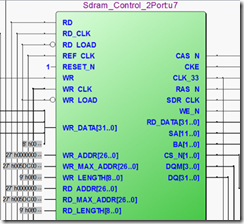

下图是DE2-115平台上与之相同范例中的SDRAM-controller,DE2-115平台的SDRAM是64M,数据位宽是32bit,所以使用的控制器是两端口的,一读一写。

再下面一张图,是DE2-70平台上,DE2_70_TV范例中使用的控制器,是一端口写入,两端口读取的。

可见,我们应该根据所作任务不同来合理分配SDRAM的读写端口数目,这对成功完成预期功能是很有意义的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号