软件设计师:计算机系统知识

硬件

CPU

计算机硬件系统由控制器、运算器、存储器、输入设备、输出设备组成。

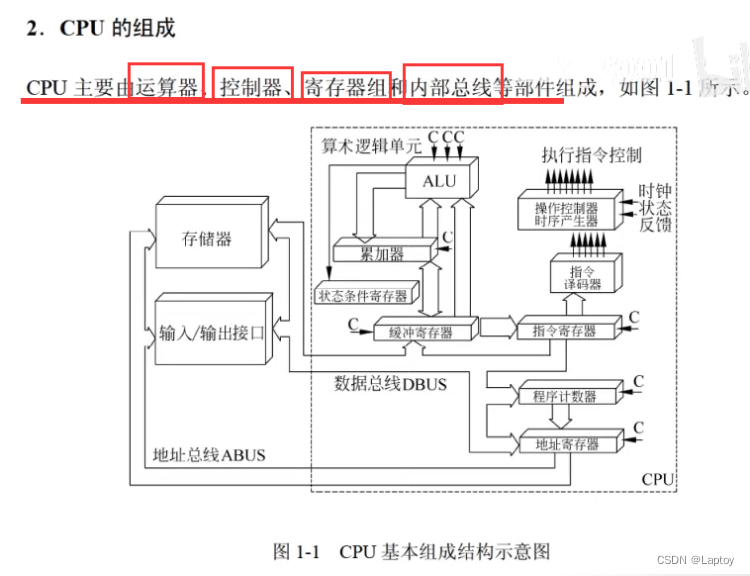

CPU 中央处理单元: 运算器、控制器等。

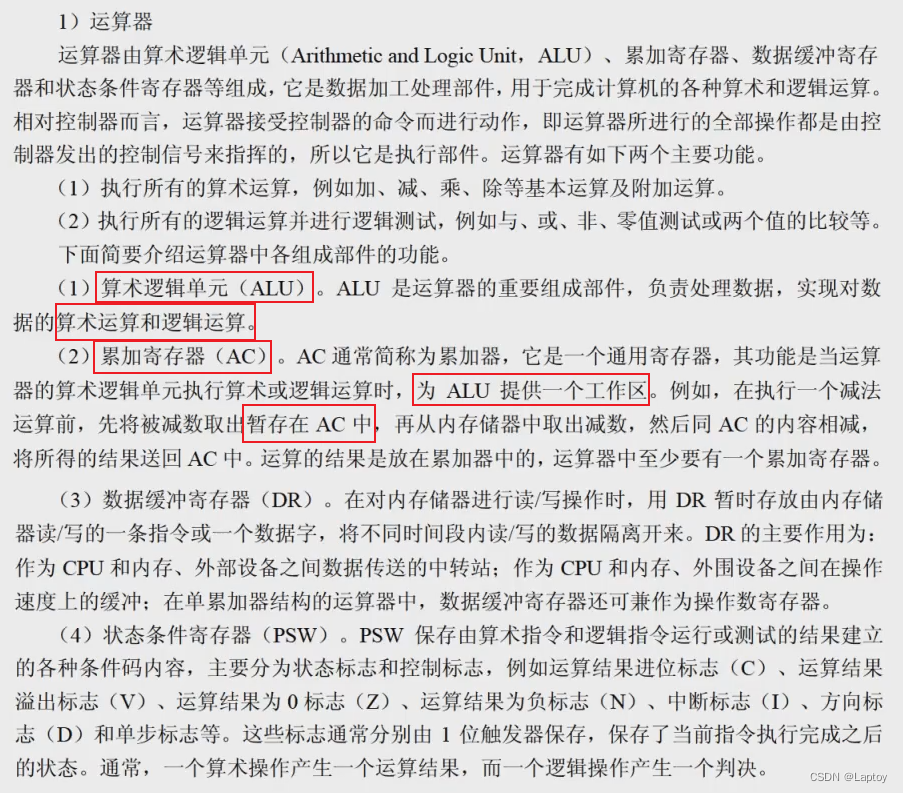

运算器

算术逻辑单元(ALU)、累加寄存器(AC)、数据缓冲寄存器、状态条件寄存器等。

控制器

指令包含操作码和地址码两部分,分析执行一条指令时,操作码、地址码都存入指令寄存器(IR)。

- 指令寄存器(IR):存放的是从内存中取得指令,就像个中间站一样,不过是存放指令的中间站

- 程序计数器(PC):存放的是下一条指令的地址(用于跟踪指令地址),还有计数的功能

- 地址寄存器(AR):存放的是cpu访问内存单元的地址

- 指令译码器(ID):是把操作码解析成对应的指令操作

进制

二、八、十、十六进制,进制转换,进制加减法。

例:字节编址从B3000H到DABFFH区域的存储容量为(B3000-DABFF)+1

数据表示

最高位是符号位,0是正,1是负。

- 原码,第一位符号位

[+1]原=0 0000001 [-1]原= 1 0000001

- 反码,第一位符号位,正数反码同原码,负数反码是绝对值按位求反

[+1]反=0 0000001 [-1]反=1 1111110

- 补码,第一位符号位,正数补码同原码同反码,负数补码是反码加1(简化计算机运算部件的设计)

[+1]补=0 0000001 [-1]补=1 1111111

- 移码,补码的符号位取反

[+1]移=1 0000001 [-1]移=0 1111111

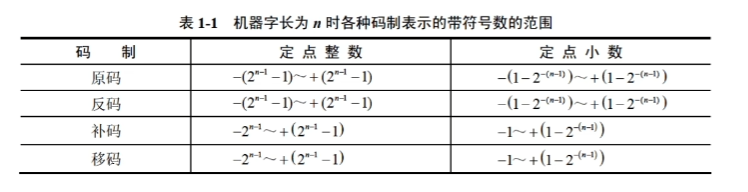

当机器字节为n时,定点数的补码和移码可表示 2n 个数,原码和反码只能表示 2n-1 个数(0的表示占用了两个编码 +0 -0)

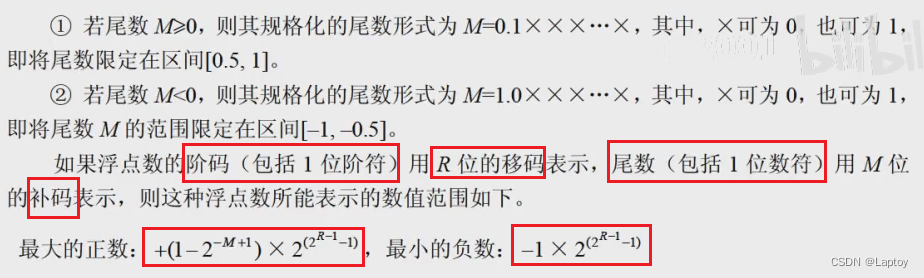

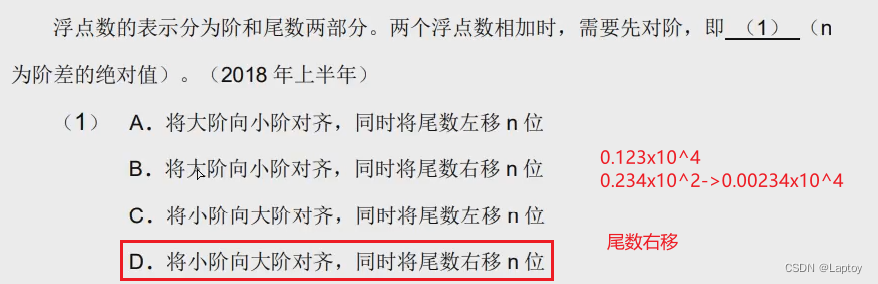

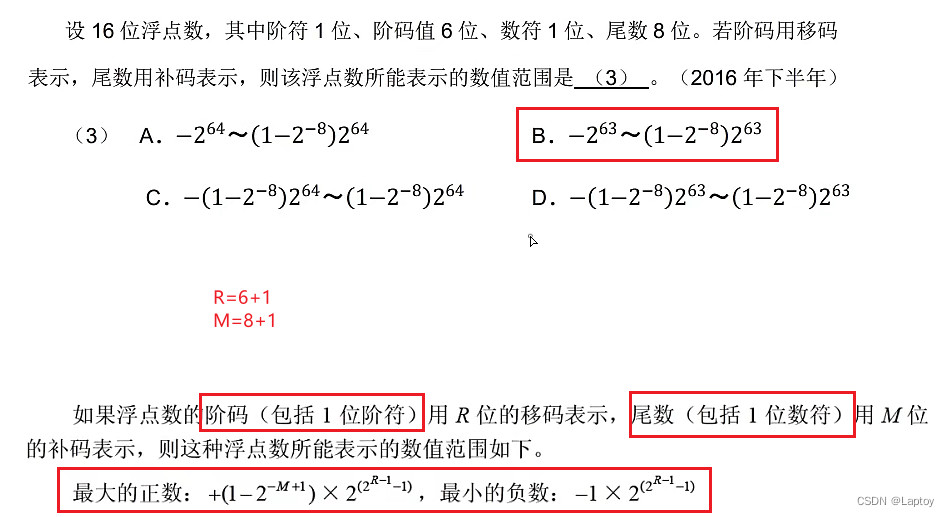

浮点数

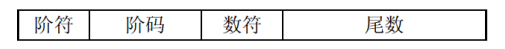

浮点表示法,N = 2E * F,其中E为阶码,F为尾数

阶码决定数值范围,尾数决定精度。阶码采用移码,尾数采用原码表示。尾数的绝对值限定在区间 [0.5,1]

阶符和数符为符号位。

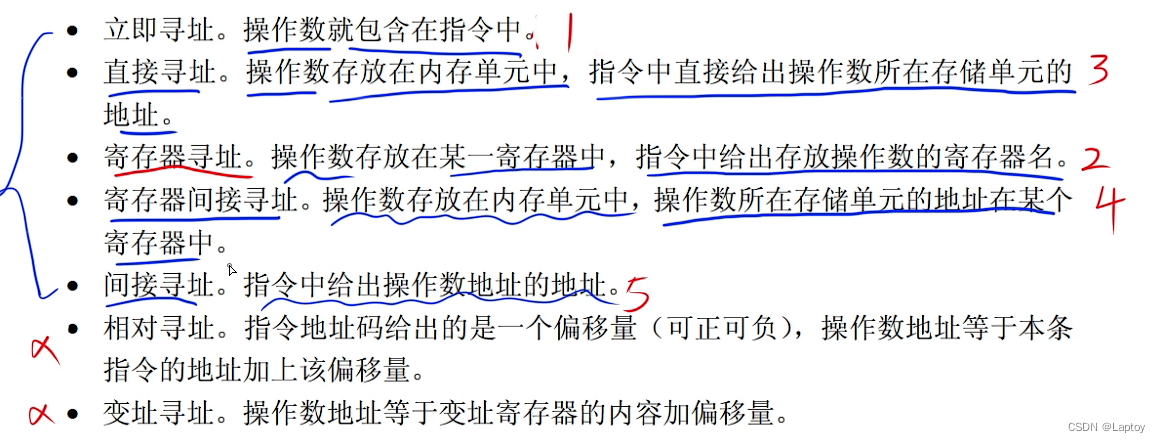

寻址

寻址速度:立即寻址>寄存器寻址>直接寻址>寄存器间接寻址>间接寻址

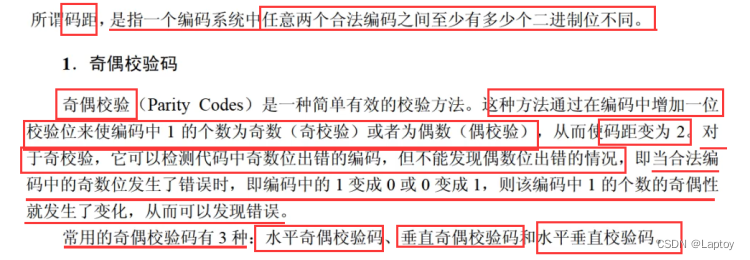

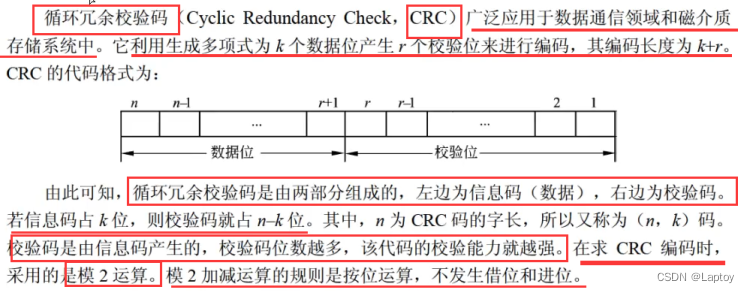

校验码

- 奇偶校验码:只能检奇偶个数错不能纠错

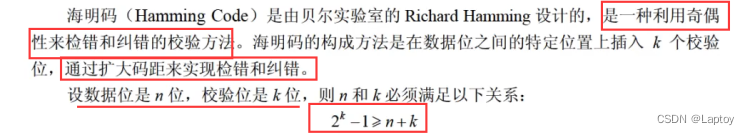

- 海明码:运用奇偶性来检错和纠错,码距是3,

2k-1>=n+k,其中k是检验位,n是数据位

码距=2,无纠错能力

码距>=3,有纠错能力

- 循环冗余检验码:码距为2,运用模二运算进行检错不能纠错

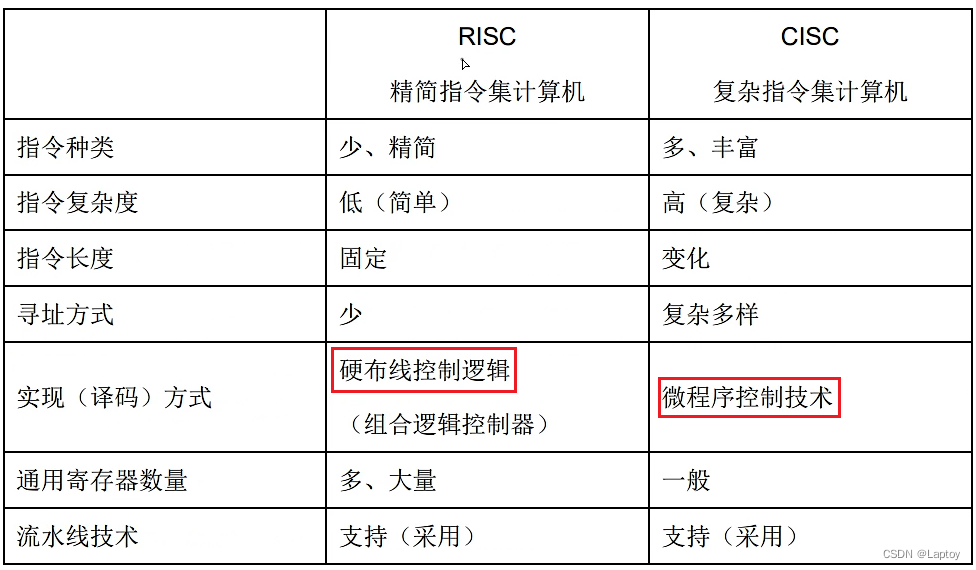

RISC 和 CISC

-

RISC:精简指令集计算机(Reduced Instruction Set Computer)

-

CISC:复杂指令集计算机(Complex Instruction Set Computer)

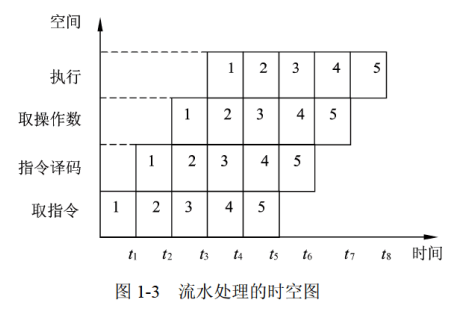

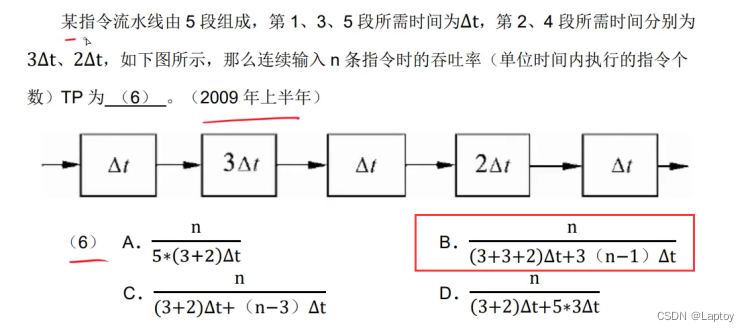

流水线

流水线执行时间 = 一条完整指令执行时间 + (n-1) * 一个周期中最长的时间

吞吐率 = 指令条数/流水线执行时间

加速比 = 使用流水线/不使用流水线

存储器

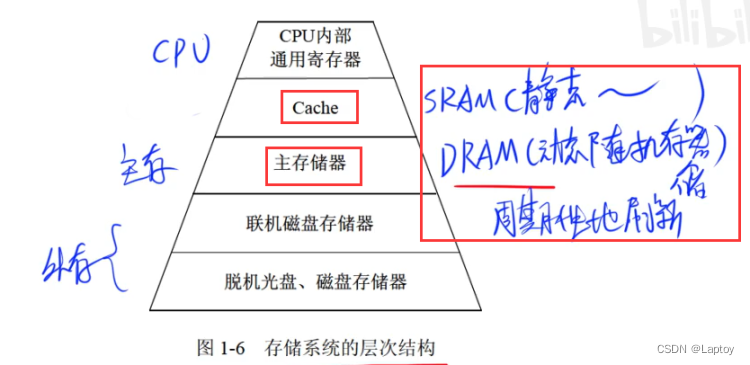

主存 SRAM(静态随机存储器) DRAM(动态随机存储器,周期性刷新) 易失型存储器 断电丢失

虚拟存储体系由主存-辅存两级存储器构成 内存也称为主存 外存也称为辅存

闪存 如U盘 非易失型存储器

相联存储器是一种按内容访问的存储器

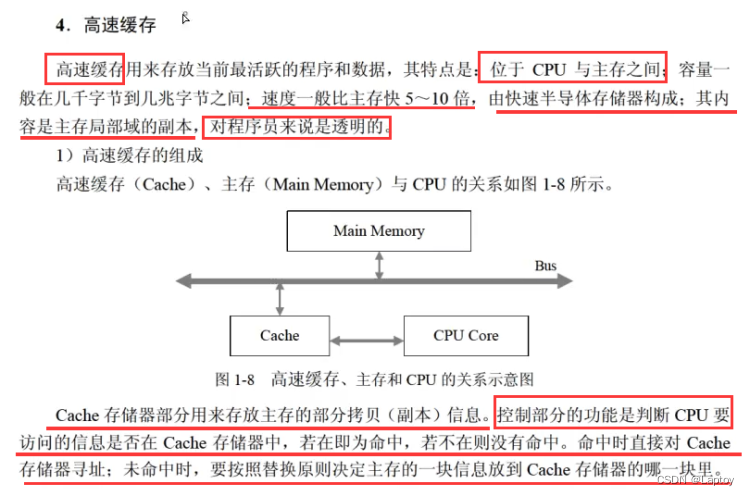

Cache

CPU和主存之间,速度快

Cache对于程序员完全透明

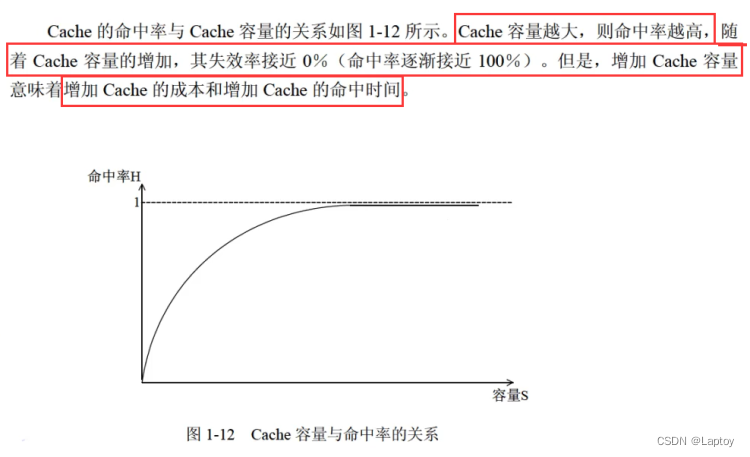

容量越大命中率越高

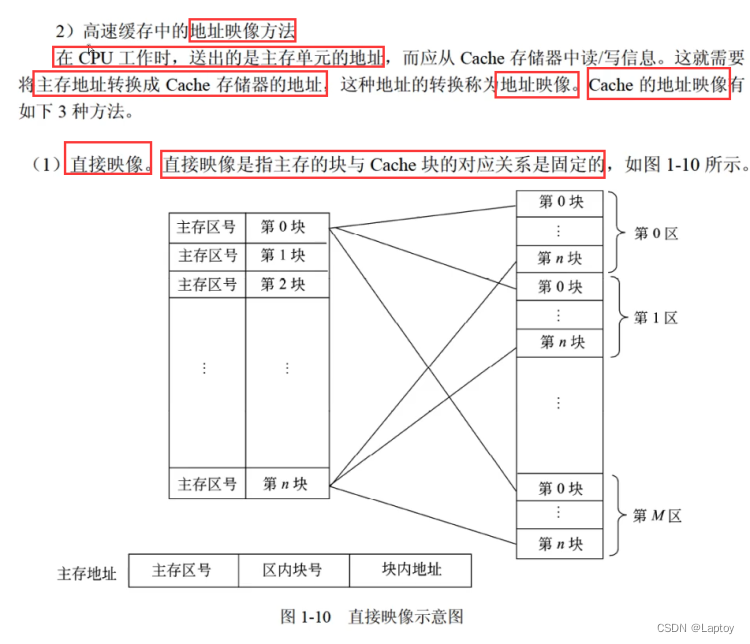

Cache与主存地址的映射由硬件自动完成

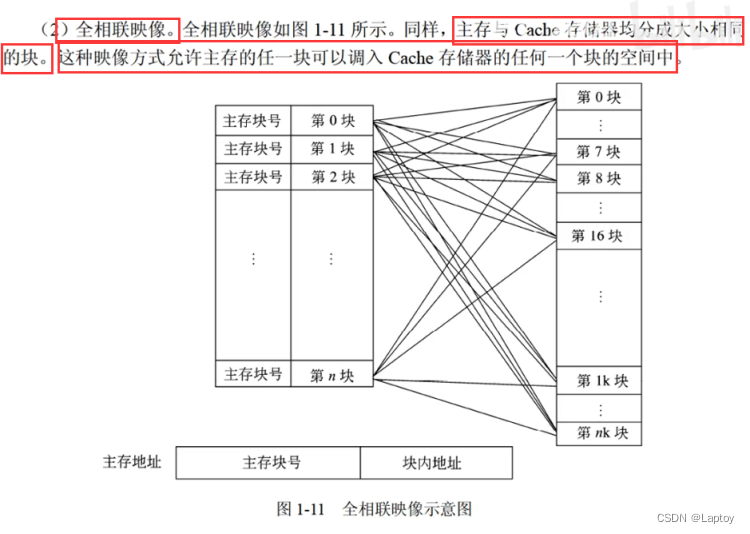

发生块冲突从少到多的顺序:全相联映射–>组相联映射–>直接映射

组相联映射是全相联映射和直接映射的这种,将Cache中的块再分成组

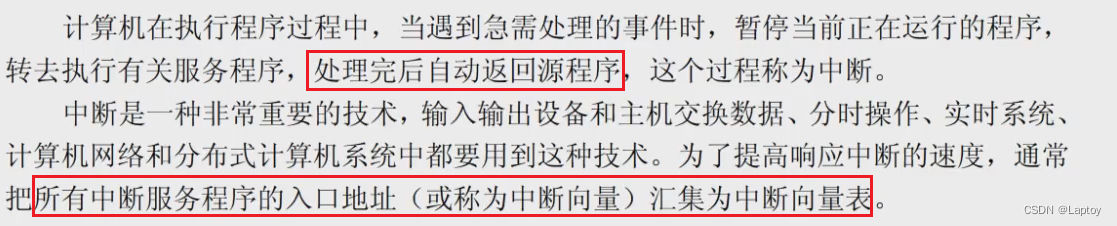

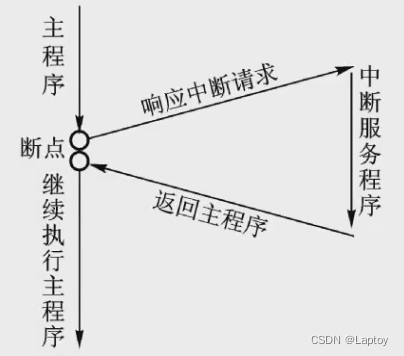

中断

- 中断向量:提供中断服务程序的入口地址

- 中断向量表:所有中断服务的入口地址

- 中断响应时间:从发出中断请求到进入中断服务程序

- 保存现场继续执行主程序

输入输出(IO)控制方式

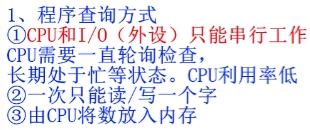

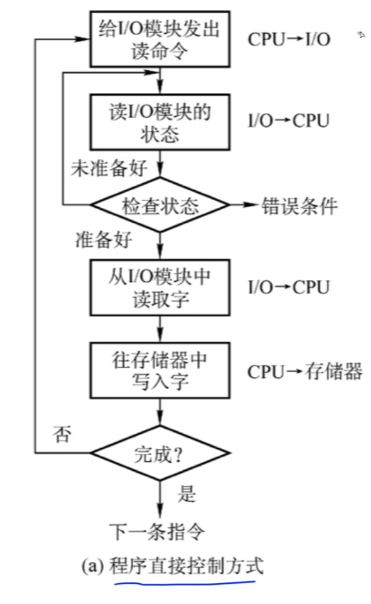

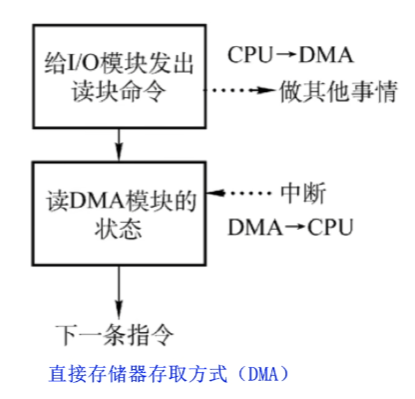

程序查询方式

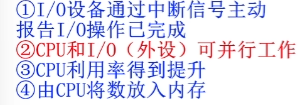

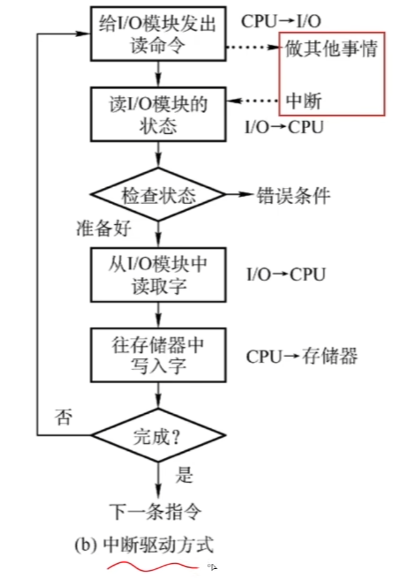

中断驱动方式

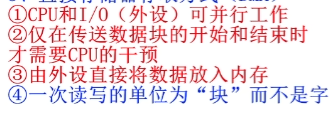

DMA(Direct Memory Access) 直接存储器访问

传输时由外设直接放入内存,无需CPU干预

DMA传输数据比中断驱动方式传输数据更快

总线

微机中总线分为数据总线、地址总线、控制总线3类。

常见总线如下图:

加密与认证

加密技术 防窃听(被动攻击)

-

对称加密:加密和解密同一把密钥,加解密速度快,密钥分发困难

-

非对称加密:公钥加密私钥解密,公钥可公开,加解密速度慢

-

混合加密:对称加密数据,非对称加密对称密钥

摘要 防篡改

不可逆、抗碰撞

把数据和摘要值一起发送,接收者计算摘要值进行对比,可验证是否被篡改

数字签名 防篡改 防否认 无法防中间人攻击

发送方用私钥对摘要值签名,将签名值放在密文后发送;接收方用公钥验签,可以防篡改和不可否认。

数字证书 保证公钥合法性

- CA:权威证书认证机构

CA对用户个人信息和用户公钥进行签名制作数字证书,用CA公钥可以验证数字证书和该公钥的合法性

加密算法

- 对称算法:DES 3DES RC-5 IDEA AES RC4

- 非对称算法:RSA ECC DSA

- 摘要算法:MD5 SHA1 SHA256

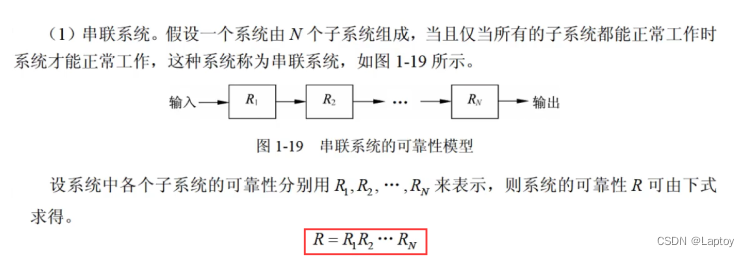

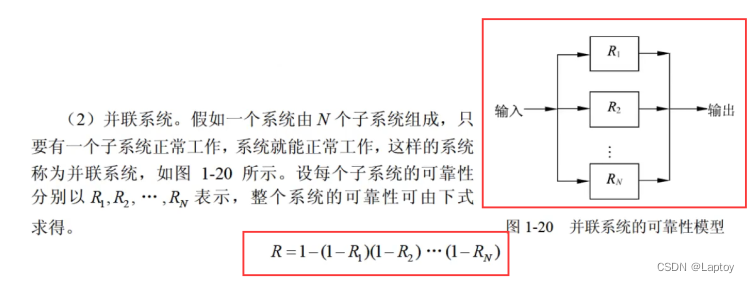

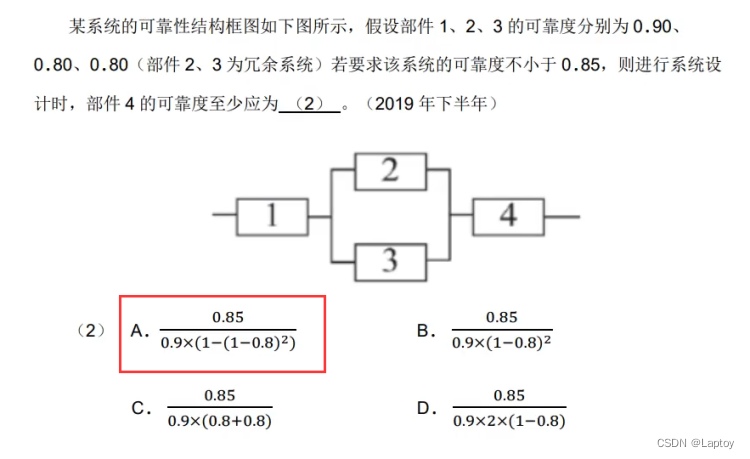

可靠性

- 串联系统可靠性:R=R1R2...RN

- 并联系统可靠性:R=1-(1-R1)(1-R2)...(1-RN)

浙公网安备 33010602011771号

浙公网安备 33010602011771号