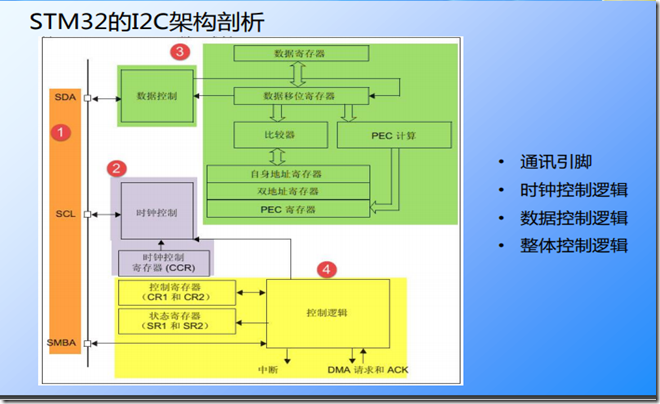

STM32的I2C特性及架构

软件模拟协议:使用CPU直接控制通讯引脚(GPIO)的电平,产生出符合通讯协议标准的逻辑。

硬件实现协议:由STM32的I2C片上外设专门负责实现I2C通讯协议,只要配置好该外设,它就会自动根据协议要求产生通讯信号,收发数据并缓存起来,CPU只要检测该外设的状态和访问数据寄存器,就能完成数据收发。这种由硬件外设处理I2C协议的方式减轻了CPU的工作,且使软件设计更加简单。

STM32的I2C外设可用作通讯的主机及从机,支持100Kbit/s和400Kbit/s的速率,支持7位、10位设备地址,支持DMA数据传输,并具有数据校验功能。

STM32框架结构

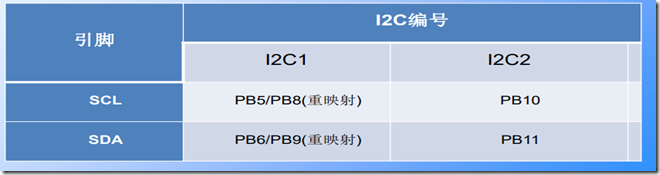

1.通讯引脚

STM32芯片有多个I2C外设,它们的I2C通讯信号引出到不同的GPIO引脚上,使用时必须配置到这些指定的引脚,以《STM32F10x规格书》为准。

2.时钟控制逻辑

SCL线的时钟信号,由I 2C接口根据时钟控制寄存器(CCR)控制,控制的参数主要为时钟频率。

• 可选择I2C通讯的“标准/快速”模式,这两个模式分别I2C对应 100/400Kbit/s的通讯速率。

• 在快速模式下可选择SCL时钟的占空比,可选Tlow/Thigh=2或 Tlow/Thigh=16/9模式。

• CCR寄存器中12位的配置因子CCR,它与I2C外设的输入时钟源共同作用,产生SCL时钟。STM32的I2C外设输入时钟源为PCLK1。

计算时钟频率:

标准模式: Thigh=CCR*TPCKL1 Tlow = CCR*TPCLK1

快速模式中Tlow/Thigh=2时: Thigh = CCR*TPCKL1 Tlow = 2*CCR*TPCKL1

快速模式中Tlow/Thigh=16/9时: Thigh = 9*CCR*TPCKL1 Tlow = 16*CCR*TPCKL1

例如,我们的PCLK1=36MHz,想要配置400Kbit/s的速率,计算方式如下:

PCLK时钟周期: TPCLK1 = 1/36000000

目标SCL时钟周期: TSCL = 1/400000

SCL时钟周期内的高电平时间: THIGH = TSCL/3

SCL时钟周期内的低电平时间: TLOW = 2*TSCL/3

计算CCR的值: CCR = THIGH/TPCLK1 = 30

计算出来的CCR值写入到寄存器即可。

3.数据控制逻辑

I2C的SDA信号主要连接到数据移位寄存器上,数据移位寄存器的数据来源及目标是数据寄存器(DR)、地址寄存器(OAR)、PEC寄存器以及SDA数据线。

• 当向外发送数据的时候,数据移位寄存器以“数据寄存器”为数据源,把数据一位一位地通过SDA信号线发送出去;

• 当从外部接收数据的时候,数据移位寄存器把SDA信号线采样到的数据一位一位地存储到“数据寄存器”中。

4.整体控制逻辑

整体控制逻辑负责协调整个I2C外设,控制逻辑的工作模式根据我们配置的“控制寄存器(CR1/CR2)”的参数而改变。

在外设工作时,控制逻辑会根据外设的工作状态修改“状态寄存器(SR1 和SR2)”,只要读取这些寄存器相关的寄存器位,就可以了解I2C的工作状态。