笔记4- vivado simulation 使用

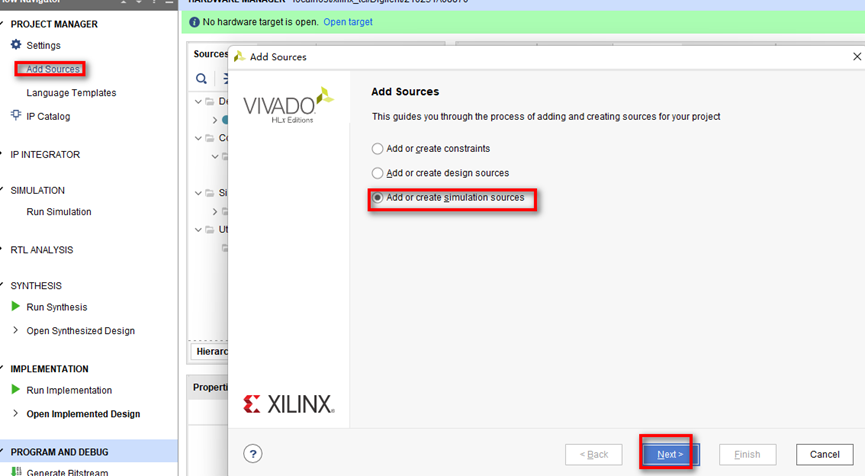

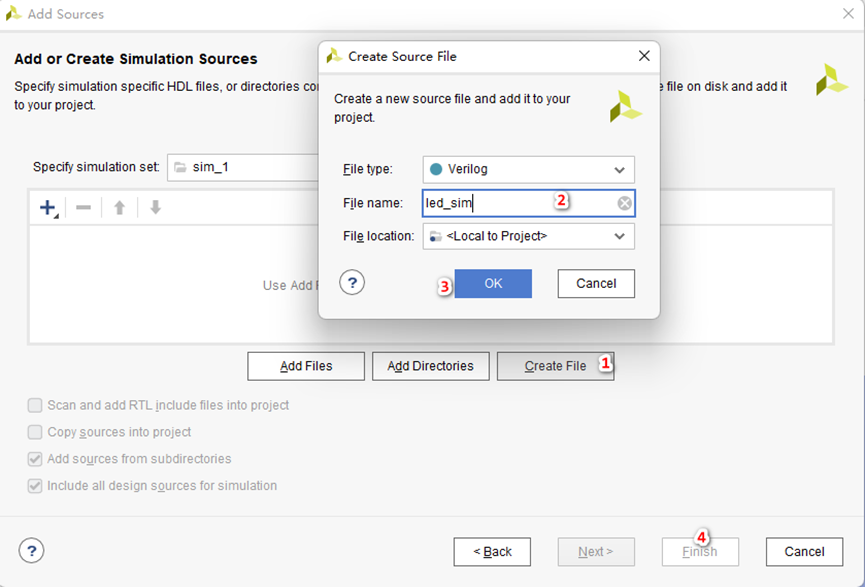

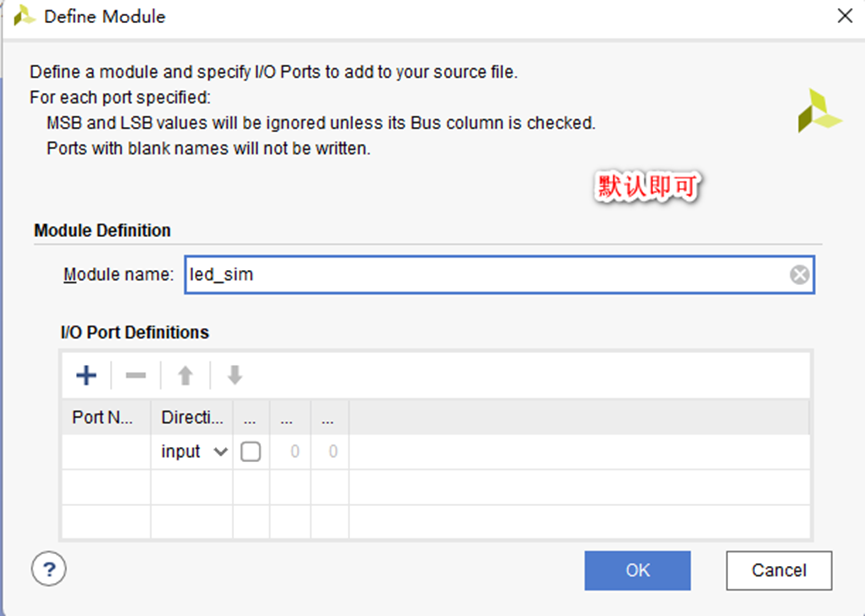

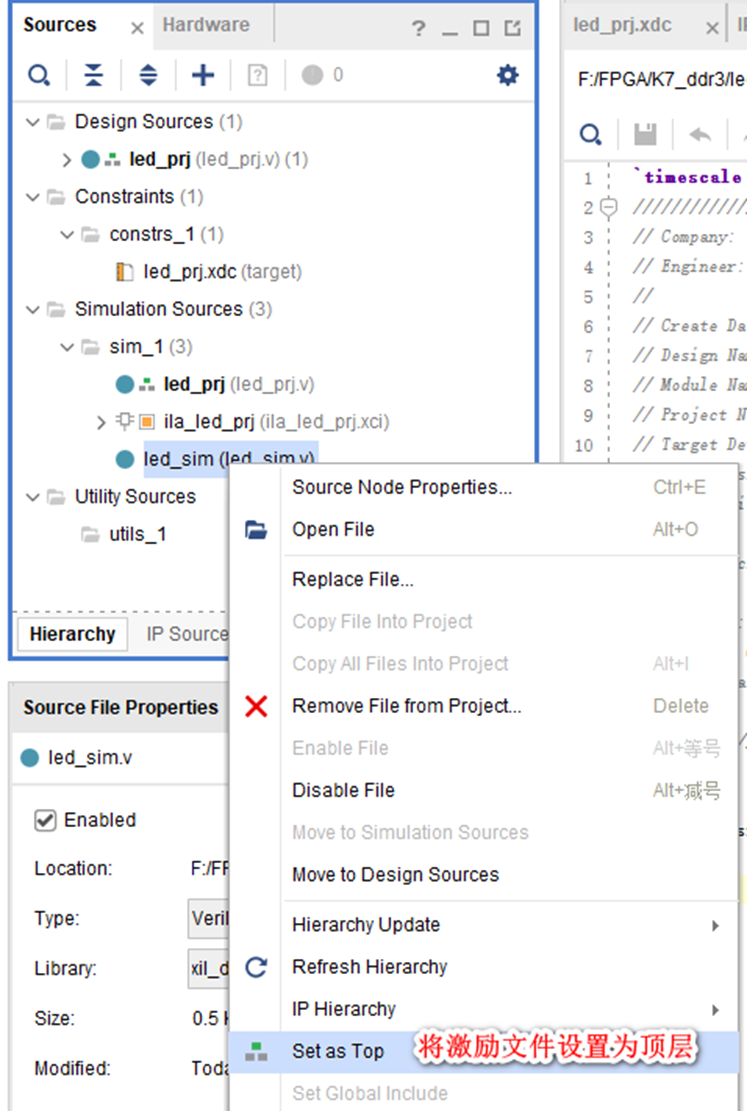

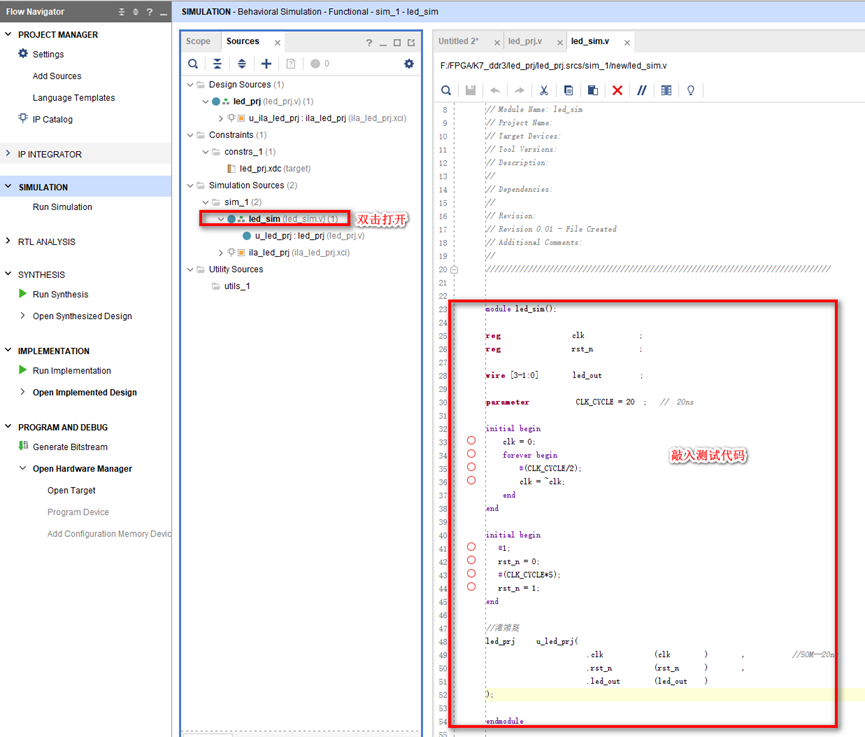

1、 创建激励测试文件

输入激励代码

1 `timescale 1ns / 1ps 2 3 module led_sim(); 4 5 reg clk ; 6 reg rst_n ; 7 8 wire [3-1:0] led_out ; 9 10 parameter CLK_CYCLE = 20 ; // 20ns 11 12 initial begin 13 clk = 0; 14 forever begin 15 #(CLK_CYCLE/2); 16 clk = ~clk; 17 end 18 end 19 20 initial begin 21 #1; 22 rst_n = 0; 23 #(CLK_CYCLE*5); 24 rst_n = 1; 25 end 26 27 //例化 28 led_prj u_led_prj( 29 .clk (clk ) , //50M--20ns 30 .rst_n (rst_n ) , 31 .led_out (led_out ) 32 ); 33 34 endmodule

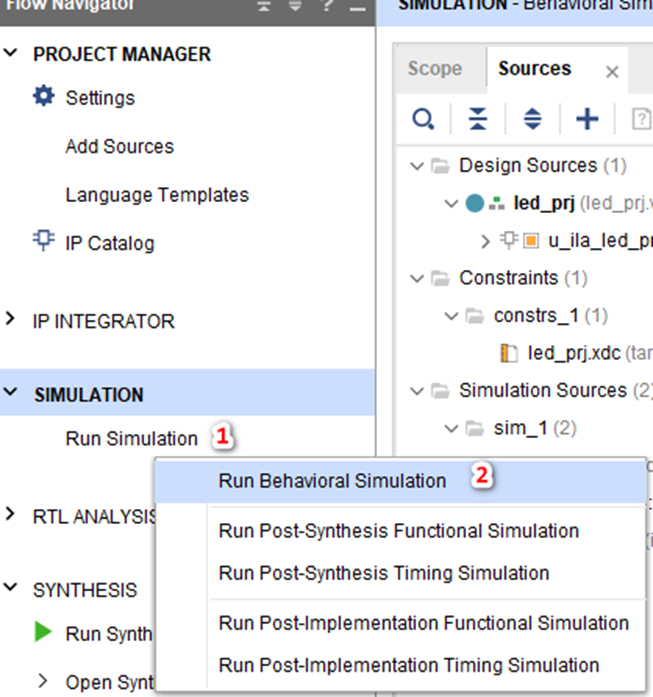

开始放着呢

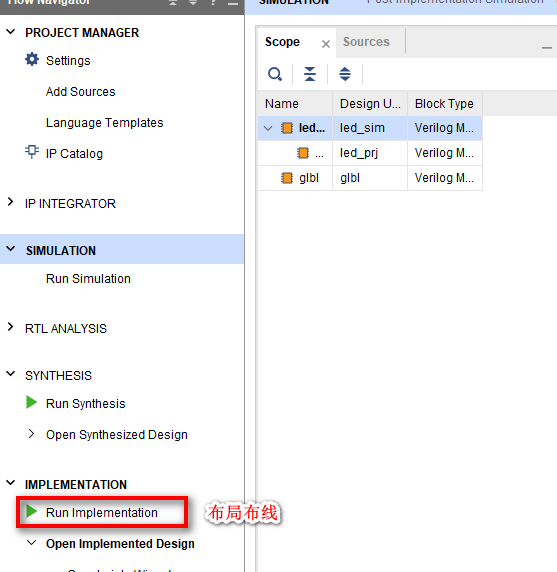

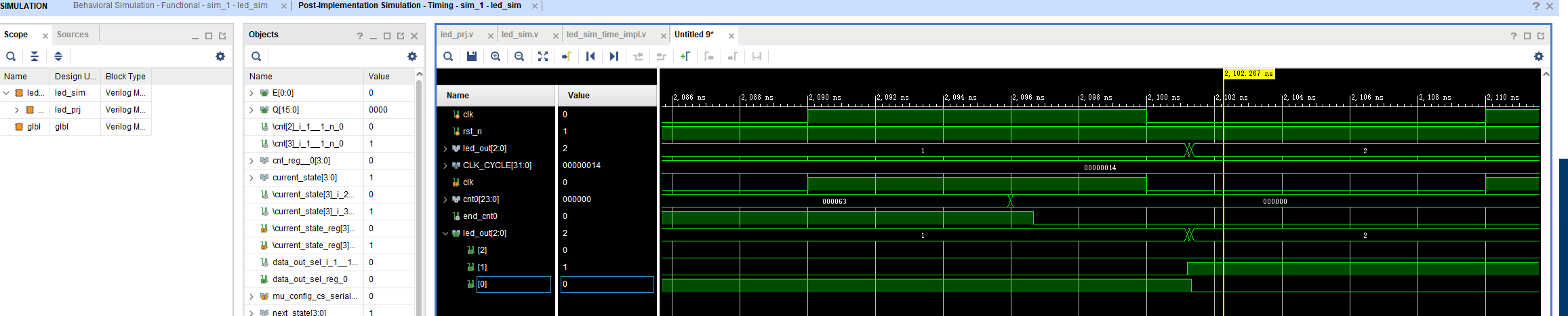

上面是没考虑布局布线的实际延时,点击布局布线

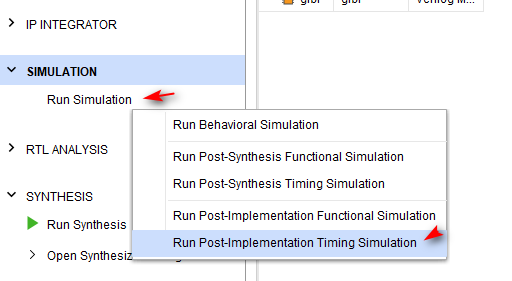

在进行一次仿真

在进行仿真查看波形,与上面对比看出是有差别的,可以看出此时仿真时序中考虑了传输延时

浙公网安备 33010602011771号

浙公网安备 33010602011771号