笔记2:vivado 的 ILA ( Integrated Logic Analyzer 内部逻辑分析仪)的 创建

ILA – Integrated Logic Analyzer 内部逻辑分析仪(是一种在线调试工具,用的非常多)

先例化在生成IP核,好处:

(1)、可以事先明确知道要看多少个信号

(2)、信号的位宽

(3)、可以一次性的配置好在线调试工具,避免先生成IP,在例化,因失误漏了信号,反复添加,编译耗时带来的苦恼问题。

(4)、流程很清楚,不会出什么错

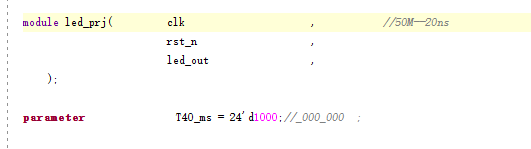

演示代码:

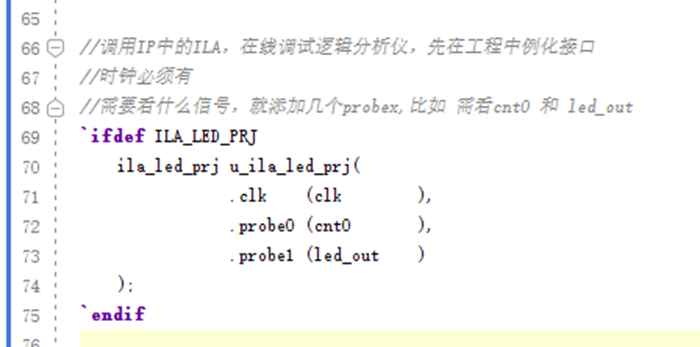

1 module led_prj( clk , //50M--20ns 2 rst_n , 3 led_out , 4 ); 5 6 parameter T40_ms = 24'd10_000_000 ; 7 8 input clk ; 9 input rst_n ; 10 11 output [3-1 :0] led_out ; 12 13 reg [24-1:0] cnt0 ; 14 reg [3-1 :0] led_out ; 15 wire add_cnt0 ; 16 wire end_cnt0 ; 17 18 always@(posedge clk or negedge rst_n)begin 19 if(!rst_n)begin 20 cnt0 <= 0; 21 end 22 else if(add_cnt0)begin 23 if(end_cnt0)begin 24 cnt0 <= 0; 25 end 26 else begin 27 cnt0 <= cnt0 + 1'b1; 28 end 29 end 30 end 31 32 assign add_cnt0 = 1; 33 assign end_cnt0 = add_cnt0 && cnt0 == T40_ms -1; 34 35 always@(posedge clk or negedge rst_n)begin 36 if(!rst_n)begin 37 led_out <= 3'b001; 38 end 39 else if(end_cnt0)begin 40 led_out <= {led_out[1:0],led_out[2]}; 41 end 42 end 43 44 //调用IP中的ILA,在线调试逻辑分析仪,先在工程中例化接口 45 //时钟必须有 46 //需要看什么信号,就添加几个probex,比如 需看cnt0 和 led_out 47 `ifdef ILA_LED_PRJ 48 ila_led_prj u_ila_led_prj( 49 .clk (clk ), 50 .probe0 (cnt0 ), 51 .probe1 (end_cnt0 ), 52 .probe2 (led_out ) 53 ); 54 `endif 55 56 endmodule

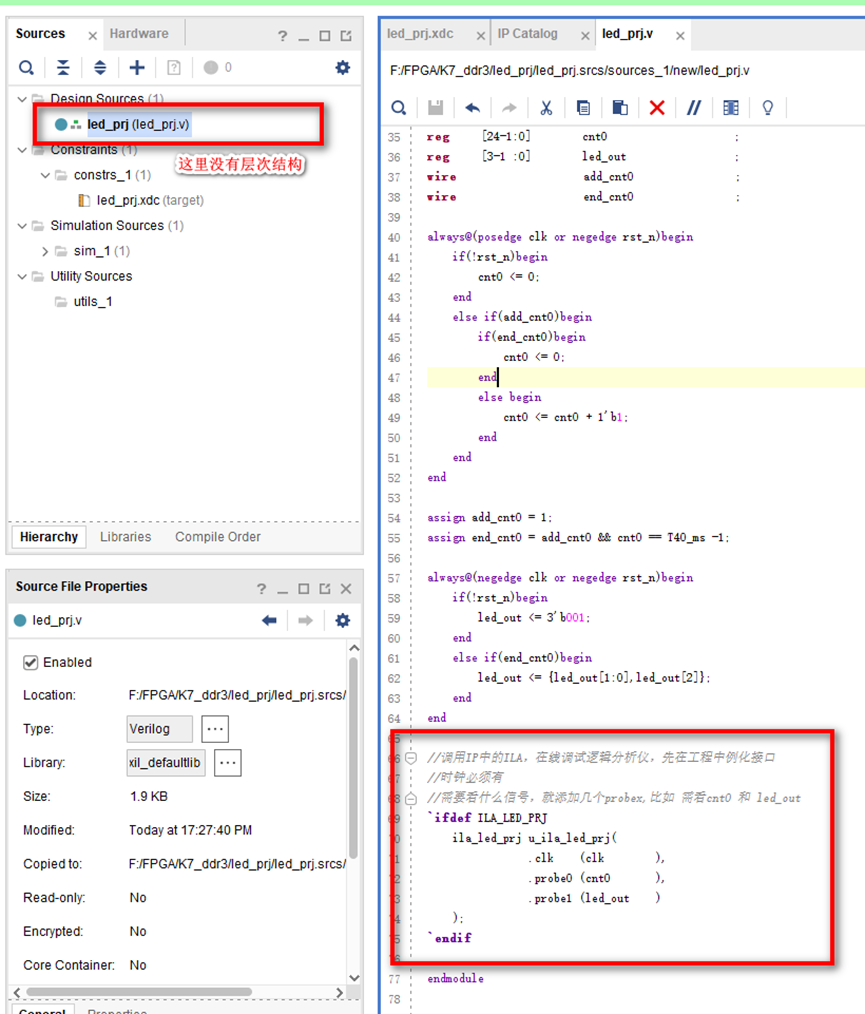

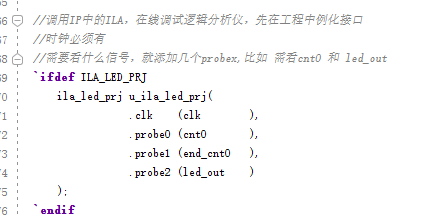

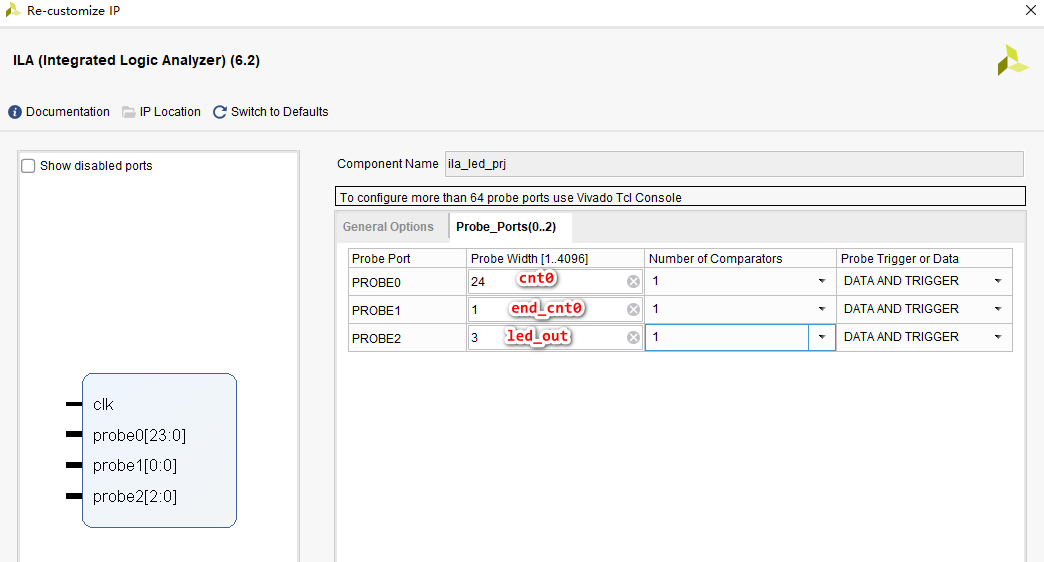

1、先在工程文件中,例化一个实例窗口,如下格式,注意:宏定义-大写名字,例化名-小写名字 ,probex 数量个数和顺序

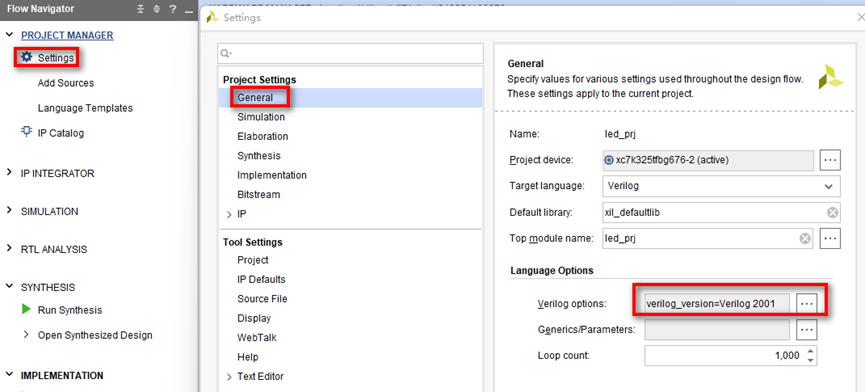

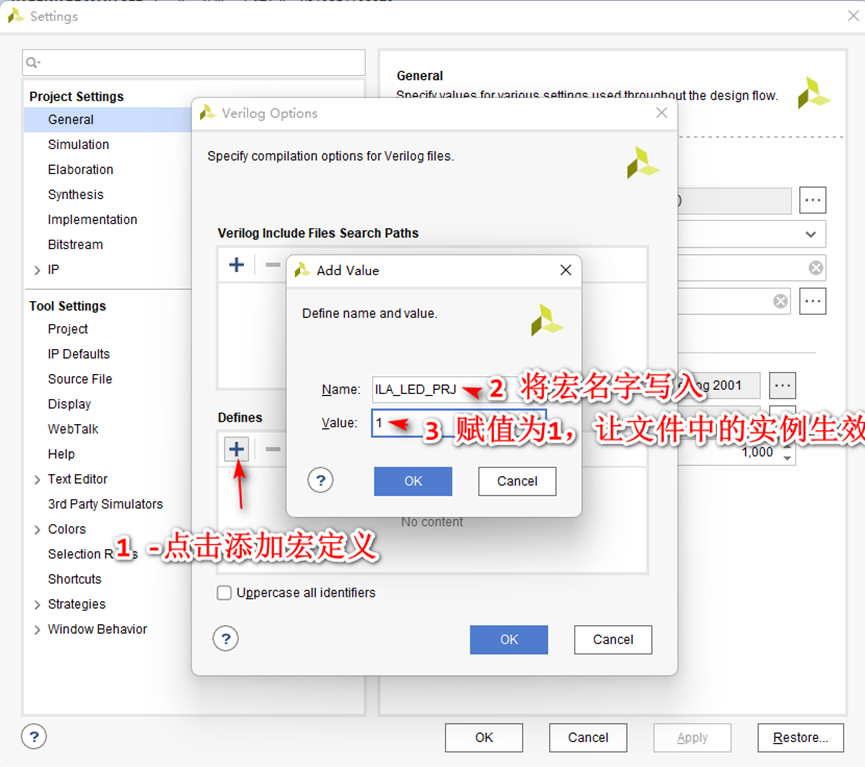

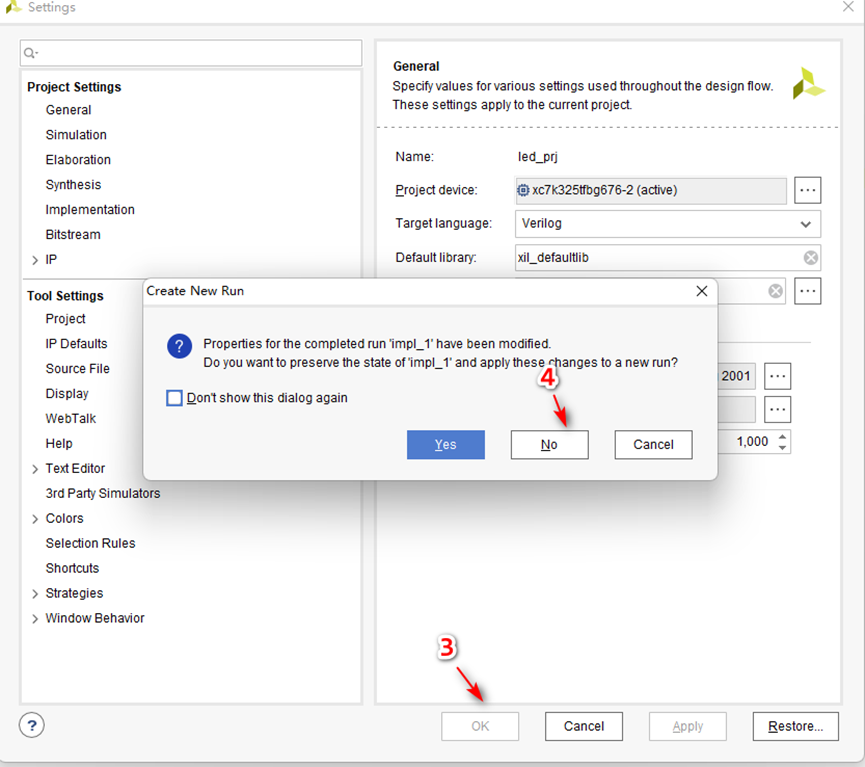

在软件里添加宏定义

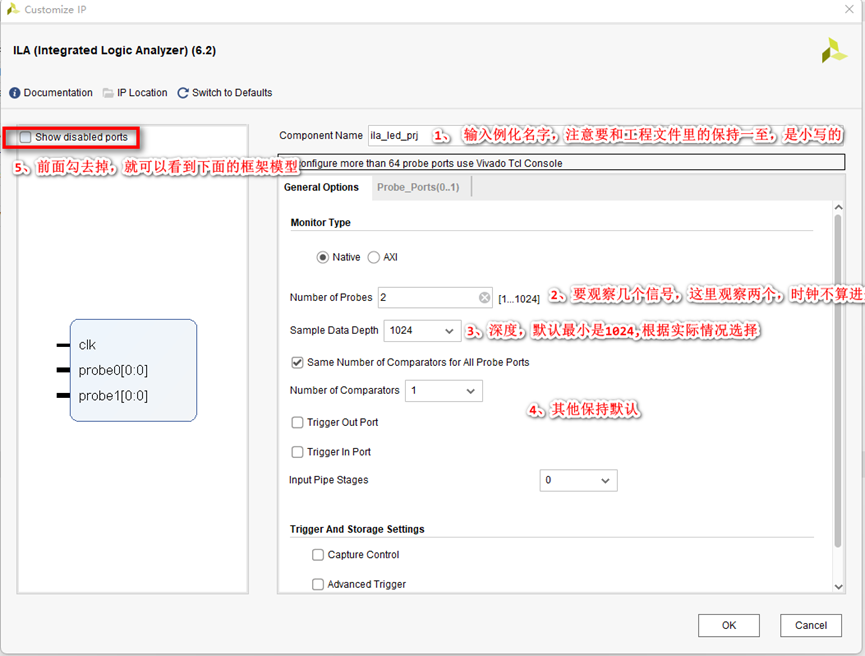

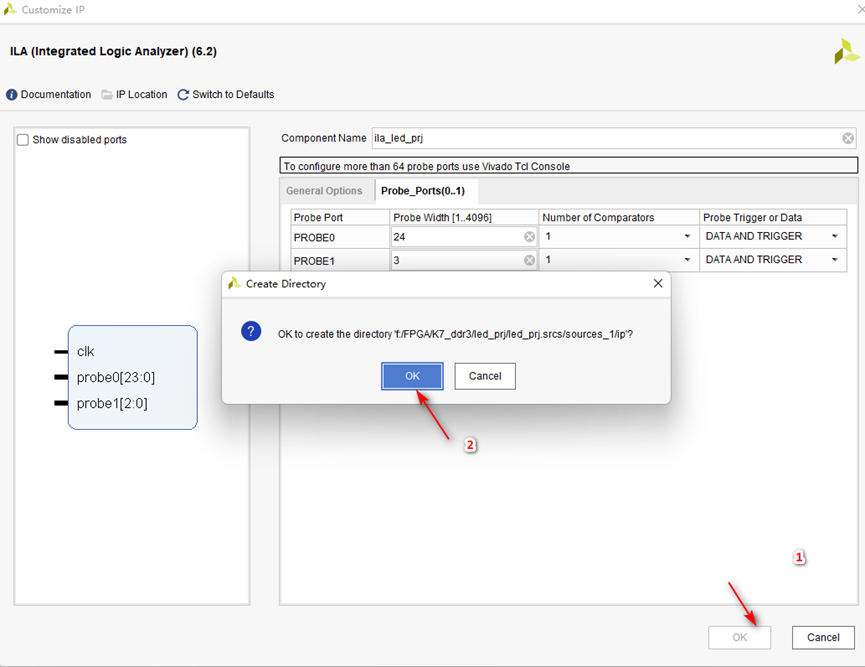

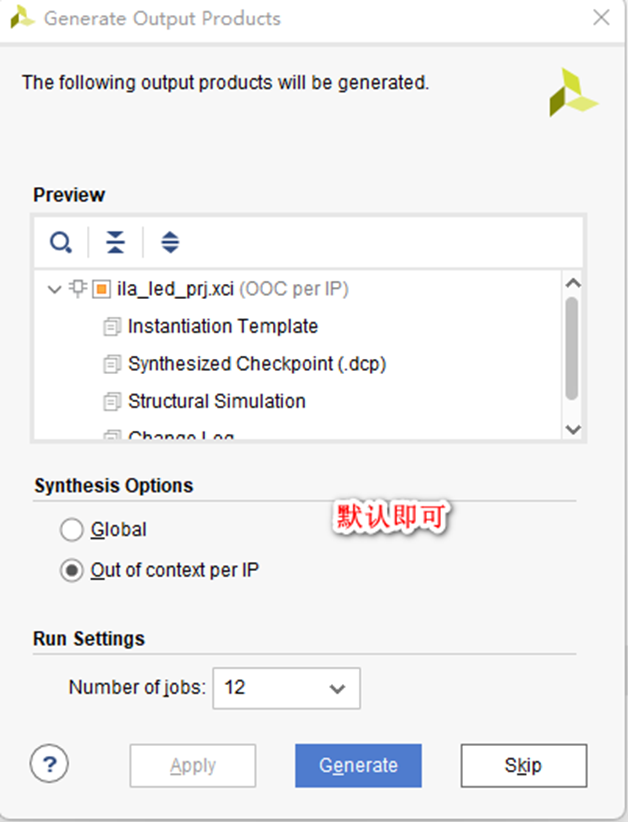

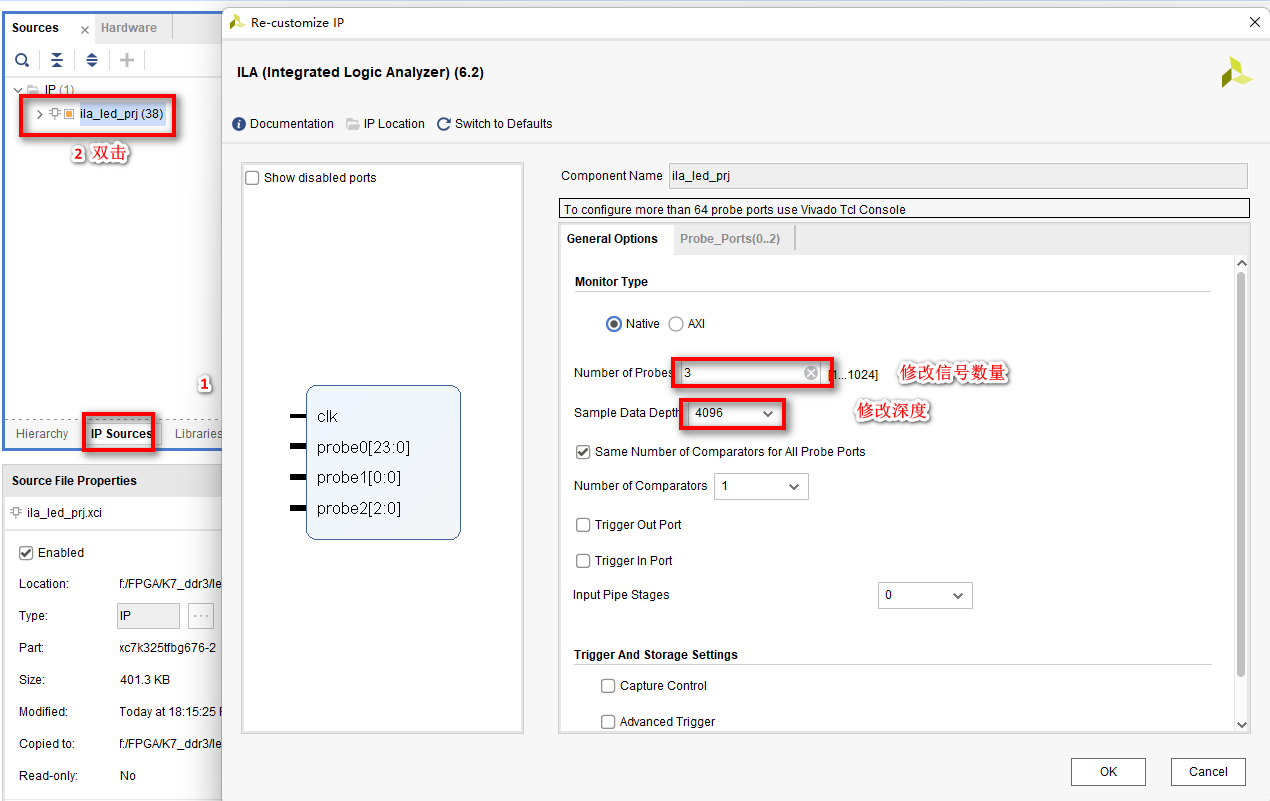

生成ILA IP核

创建完IP后,直接生成bit文件

下载调试

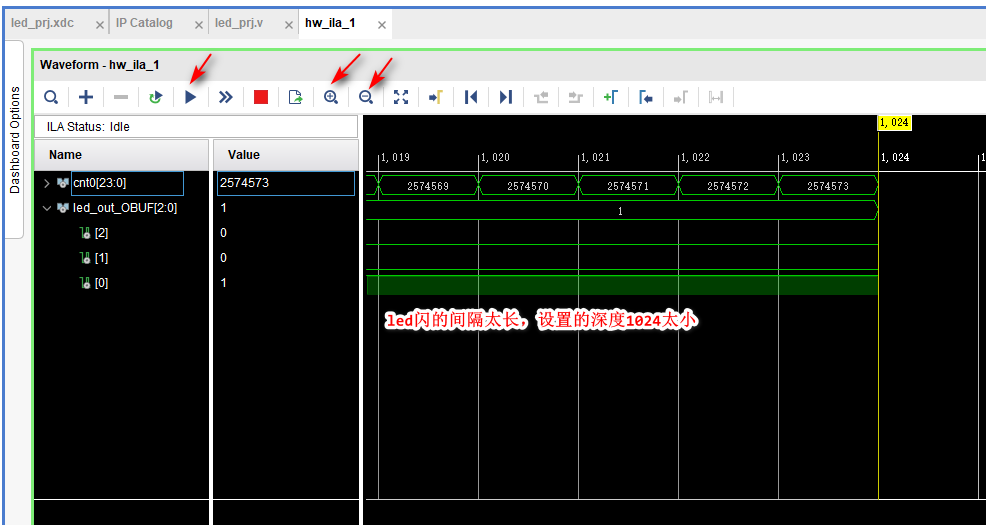

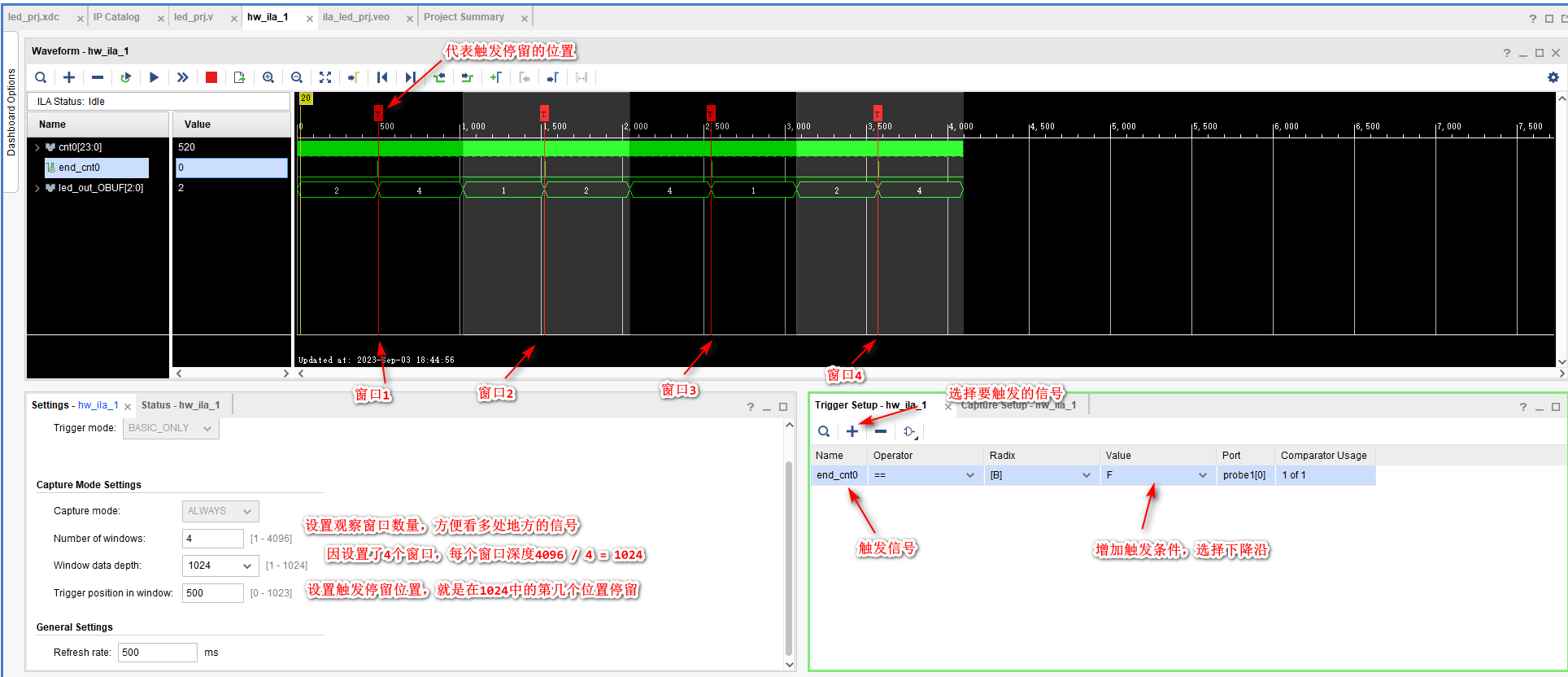

下载进去之后,就可以看到自动打开的ILA波形界面

可以返回软件里对ILA设置进行修改,因流水灯闪的计数太长,闪的慢,为了演示效果,改下计数器,增加一个信号

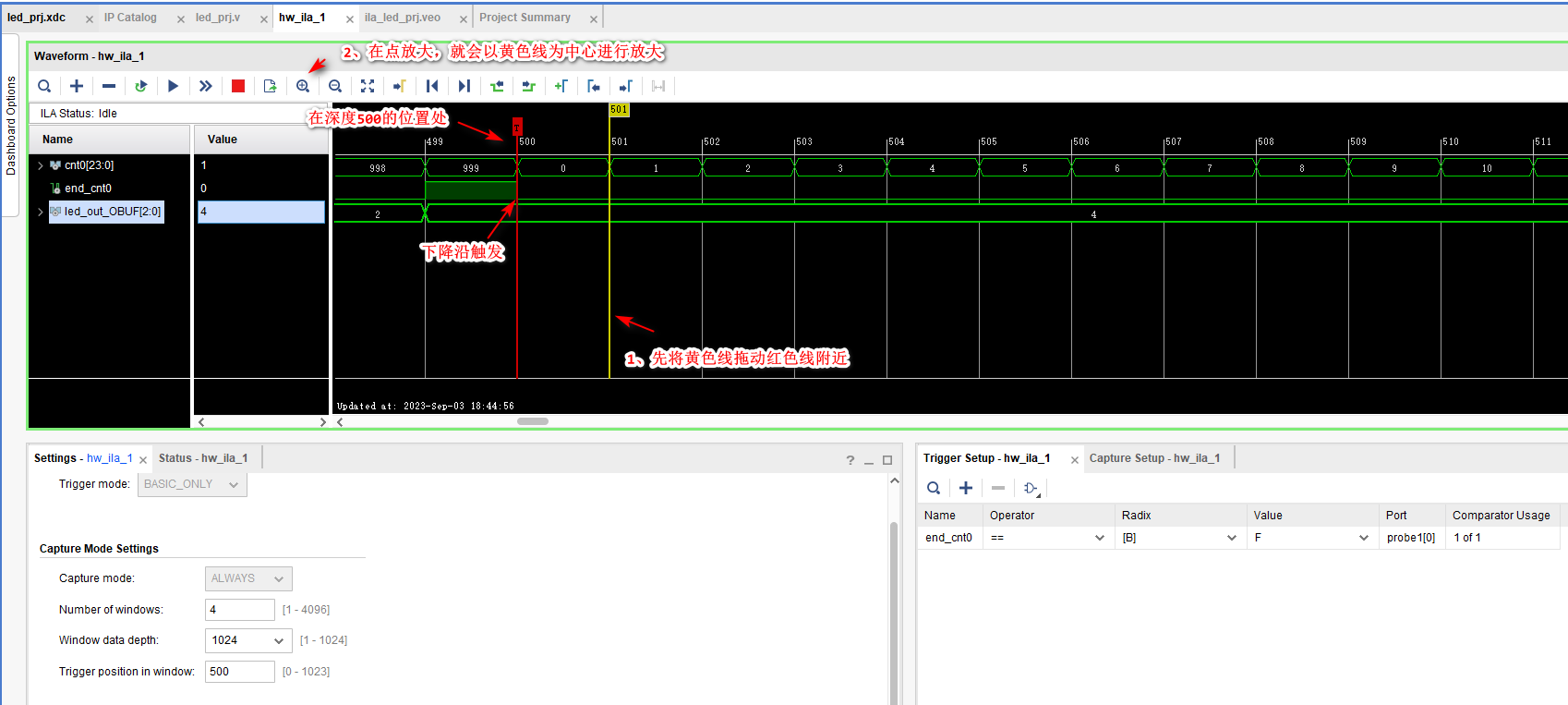

重新生成bit,下载到板子上,然后观看波形

还可以设置多个窗口,看多处地方的波形,触发条件等,如下图

OK, 在线调试工具,ILA 逻辑分析完成。

注意: 如果没有时钟, ILA里的波形是不会有的,所以当没看到波形时 ,首先检查时钟对不对

浙公网安备 33010602011771号

浙公网安备 33010602011771号