基于温度检测工程:ascii_2_hex 练习

因工作关系,中间隔好久没写代码,感觉有点生疏了。看来还是得多写写才行!!

当串口输入的是ascii值时 ,FPGA内部收到的数据需将ascii转为十六进制。

在0~9、 A~F、a~f 范围内是有效数据,并对进行转换,其他值都无效,dout输出为0

模块代码:

1 module ascii_2_hex( 2 clk , 3 rst_n , 4 din , 5 din_vld , 6 dout , 7 dout_vld 8 ); 9 10 input clk ; 11 input rst_n ; 12 input[8-1:0] din ; 13 input din_vld ; 14 15 output[8-1:0] dout ; 16 output dout_vld ; 17 18 reg[8-1:0] dout ; 19 reg dout_vld ; 20 21 wire num_0_9 ; 22 wire num_A_F ; //定义变量中是区分大小写的 23 wire num_a_f ; //定义变量中是区分大小写的 24 25 assign num_0_9 = din >= 8'd48 && din < 8'd58 ; 26 assign num_A_F = din >= 8'd65 && din < 8'd71 ; 27 assign num_a_f = din >= 8'd97 && din < 8'd103 ; 28 29 always @(posedge clk or negedge rst_n)begin 30 if(!rst_n)begin 31 dout <= 0; 32 end 33 else if(num_0_9)begin 34 dout <= din - 8'd48; //输入0~9 35 end 36 else if(num_A_F)begin 37 dout <= din - 8'd55; //输入A~F 38 end 39 else if(num_a_f)begin 40 dout <= din - 8'd87; //输入a~f 41 end 42 else begin 43 dout <= 0; 44 end 45 end 46 47 always @(posedge clk or negedge rst_n)begin 48 if(!rst_n)begin 49 dout_vld <= 1'b0; 50 end 51 else if(din_vld && (num_0_9 || num_A_F || num_a_f))begin //输入数据有效时,同时加上是否在0~9 ,A~F, a~f的范围内 52 dout_vld <= 1'b1; //只保留一个时钟周期 53 end 54 else begin 55 dout_vld <= 1'b0; 56 end 57 end 58 59 endmodule

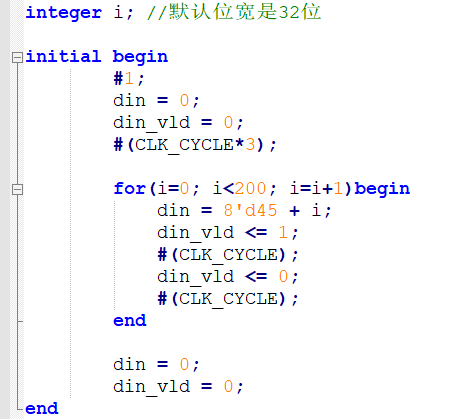

仿真代码:

1 `timescale 1ns/100ps //时间精确到1位小数点 2 3 module test_sim; 4 5 reg clk ; 6 reg rst_n ; 7 reg[8-1:0] din ; 8 reg din_vld ; 9 10 wire[8-1:0] dout ; 11 wire dout_vld ; 12 13 parameter CLK_CYCLE = 20; //时钟50M 14 15 initial begin 16 clk = 0; 17 forever begin 18 #(CLK_CYCLE/2); 19 clk = ~clk; 20 end 21 end 22 23 initial begin 24 rst_n = 1; 25 #1; 26 rst_n = 0; 27 #(CLK_CYCLE*2); 28 rst_n = 1; 29 end 30 31 integer i; //默认位宽是32位 32 33 initial begin 34 #1; 35 din = 0; 36 din_vld = 0; 37 #(CLK_CYCLE*3); 38 39 for(i=0; i<200; i=i+1)begin 40 din = 8'd45 + i; 41 din_vld <= 1; 42 #(CLK_CYCLE); 43 din_vld <= 0; 44 #(CLK_CYCLE); 45 end 46 47 din = 0; 48 din_vld = 0; 49 end 50 51 ascii_2_hex ascii_2_hex_inist( 52 .clk (clk ), 53 .rst_n (rst_n ), 54 55 .din (din ), 56 .din_vld (din_vld ), 57 58 .dout (dout ), 59 .dout_vld (dout_vld ) 60 ); 61 62 endmodule

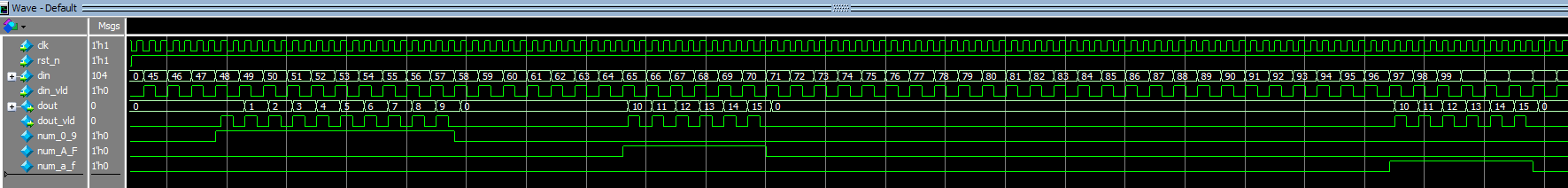

仿真波形:

总结:

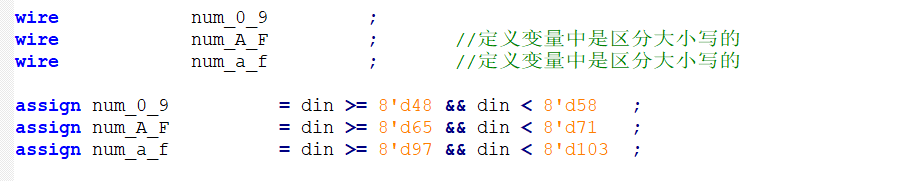

1、定义的变量中,区分大小写的,一开始还值得怀疑,语法这块还不是很扎实,如下写法是对的,

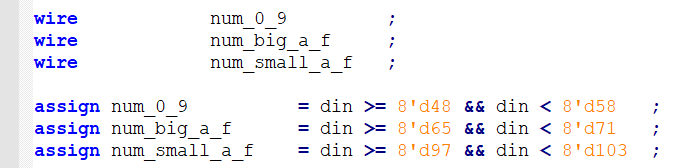

尽量保持规范,以后尽量统一用小写字母表示,如下,理解字母意思就可以了

2、测试文件多写多练,否则很容易忘记,甚至不熟悉,可能单词都不能快速的写出来