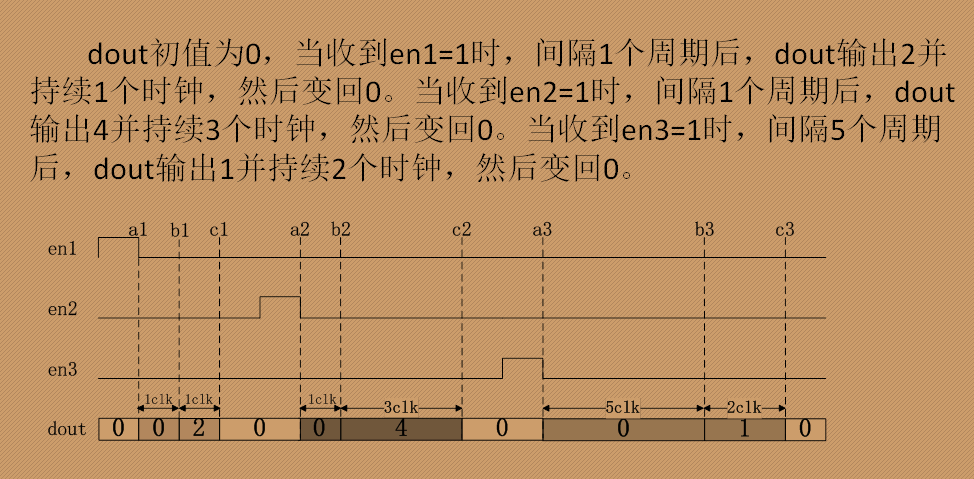

阶段2-计数器练习8

首先只需一个计数器就可以,设定变量x,用来指示计数器cnt0 结束

1 module cnt_test( 2 clk, 3 rst_n, 4 en1, 5 en2, 6 en3, 7 dout 8 ); 9 10 input clk; 11 input rst_n; 12 input en1; 13 input en2; 14 input en3; 15 16 output [2:0] dout; 17 18 reg [2:0] dout; 19 reg flag_add; 20 21 reg [3:0] cnt0; 22 reg [3:0] x; 23 reg [3:0] y; 24 reg [3:0] z; 25 reg [3:0] flag_sel; 26 27 wire add_cnt0; 28 wire end_cnt0; 29 30 always @(posedge clk or negedge rst_n)begin 31 if(!rst_n)begin 32 cnt0 <= 0; 33 end 34 else if(add_cnt0)begin 35 if(end_cnt0)begin 36 cnt0 <= 0; 37 end 38 else begin 39 cnt0 <= cnt0 + 1; 40 end 41 end 42 end 43 44 assign add_cnt0 = flag_add; 45 assign end_cnt0 = add_cnt0 && cnt0 == x - 1; 46 47 always @(posedge clk or negedge rst_n)begin 48 if(!rst_n)begin 49 flag_sel <= 0; 50 end 51 else if(en1)begin 52 flag_sel <= 0; 53 end 54 else if(en2)begin 55 flag_sel <= 1; 56 end 57 else if(en3)begin 58 flag_sel <= 2; 59 end 60 end 61 62 always @(posedge clk or negedge rst_n)begin 63 if(!rst_n)begin 64 flag_add <= 0; 65 end 66 else if(en1 || en2 || en3)begin 67 flag_add <= 1; 68 end 69 else if(end_cnt0)begin 70 flag_add <= 0; 71 end 72 end 73 74 always @(posedge clk or negedge rst_n)begin 75 if(!rst_n)begin 76 dout <= 0; 77 end 78 else if(add_cnt0 && cnt0 == y-1)begin 79 dout <= z; 80 end 81 else if(end_cnt0)begin 82 dout <= 0; 83 end 84 end 85 86 always @(*)begin 87 if(flag_sel == 0)begin 88 x = 2; 89 y = 1; 90 z = 2; 91 end 92 else if (flag_sel == 1)begin 93 x = 4; 94 y = 1; 95 z = 4; 96 end 97 else if(flag_sel == 2)begin 98 x = 7; 99 y = 5; 100 z = 1; 101 end 102 else begin //这个else后面的语句虽不会被执行,但却不能省去,避免被综合出锁存器 103 x = 0; 104 y = 0; 105 z = 0; 106 end 107 end 108 109 endmodule

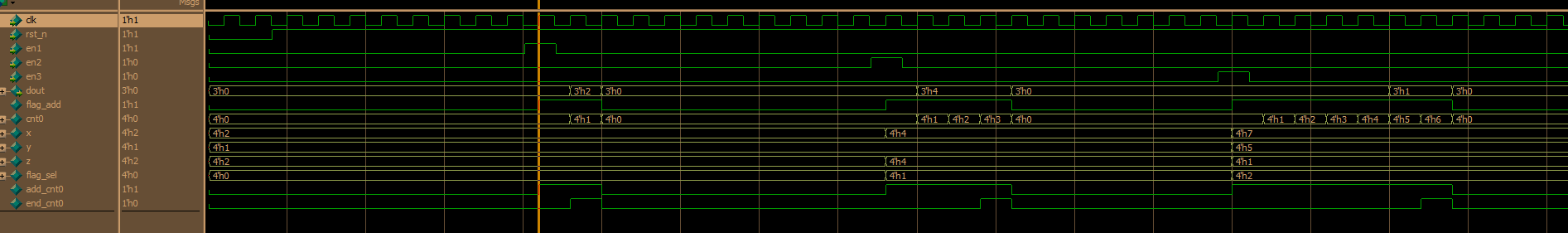

仿真波形:

浙公网安备 33010602011771号

浙公网安备 33010602011771号