FPGA读DDR的三级缓存机制

保证视频读和写DDR不冲突

实现程序:

// ************************************************** // Description : 输入读或写场同步信号的上升沿 // 输出写地址页、读地址页和写原始像素标志位。方法采用三级缓存机制。 // Author : weitter // Email : weitter@qq.com // School : Fuzhou University // Date : 2021-04-01 // Filename : page_make.v // Modulename : page_make // *************************************************** module page_make ( input clk ,//输入时钟信号 input reset_n ,//复位信号 input write_read_vs_pos ,//读或写场同步信号的上升沿 output reg[1:0] wo_page_flag_ddr ,//写原始像素的页地址 output reg[1:0] ro_page_flag_ddr ,//读原始像素的页地址 output reg write_orig_flag //正在写原始像素页的标志 ); // *************************************************** // Code_annotation: // 三级缓存机制 // *************************************************** parameter DDR_page_1 = 2'b01;//DDR的第一页 parameter DDR_page_2 = 2'b10;//DDR的第二页 parameter DDR_page_3 = 2'b11;//DDR的第三页 reg [1:0]state; always@(posedge clk )begin if(!reset_n)begin//同步复位,管理输出 // reset wo_page_flag_ddr <= DDR_page_1;//复位的时候写第1页,读第3页,有个疑问?这个时候第3页会不会没有数据??? ro_page_flag_ddr <= DDR_page_3; state <= DDR_page_1; write_orig_flag <= 1'b0; end else if(write_read_vs_pos)begin//当写的场同步信号有效时候,写的页按照1 2 3 1 2 3....的循环写入 case(state) DDR_page_1:begin wo_page_flag_ddr <= DDR_page_1;//写第1页,读第3页 ro_page_flag_ddr <= DDR_page_3; state <= DDR_page_2;//当前在写第1页,下一次写第2页 end DDR_page_2:begin wo_page_flag_ddr <= DDR_page_2;//写第2页,读第1页 ro_page_flag_ddr <= DDR_page_1; state <= DDR_page_3;//当前在写第2页,下一次写第3页 write_orig_flag <= 1'b1; end DDR_page_3:begin wo_page_flag_ddr <= DDR_page_3;//写第3页,读第1页 ro_page_flag_ddr <= DDR_page_2; state <= DDR_page_1;//当前在写第3页,下一次写第1页 end default:begin wo_page_flag_ddr <= DDR_page_1; ro_page_flag_ddr <= DDR_page_3; state <= DDR_page_1; write_orig_flag <= 1'b0; end endcase end else begin//防止锁存器产生 wo_page_flag_ddr <= wo_page_flag_ddr;//保持 ro_page_flag_ddr <= ro_page_flag_ddr; end end endmodule

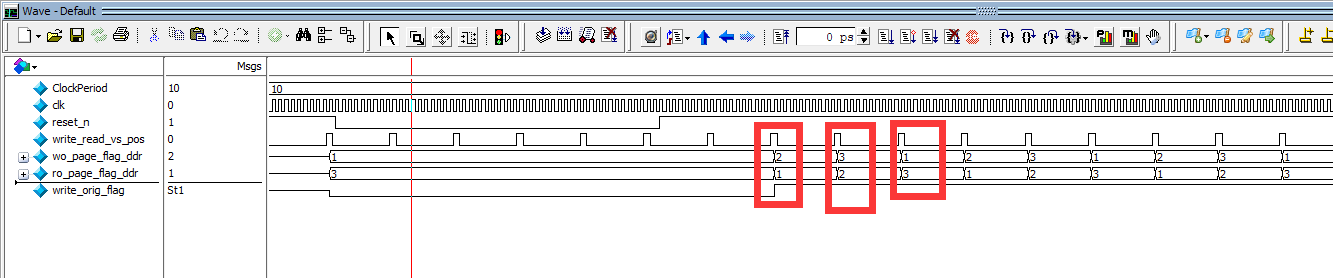

仿真截图:

浙公网安备 33010602011771号

浙公网安备 33010602011771号