2440启动过程分析

2440启动过程分析

2440启动过程算是一个难点,不太容易理解,而对于2440启动过程的理解,影响了后面裸机代码执行流程的分析,从而看出2440启动过程的重要性。

2440启动方式和启动方式选择

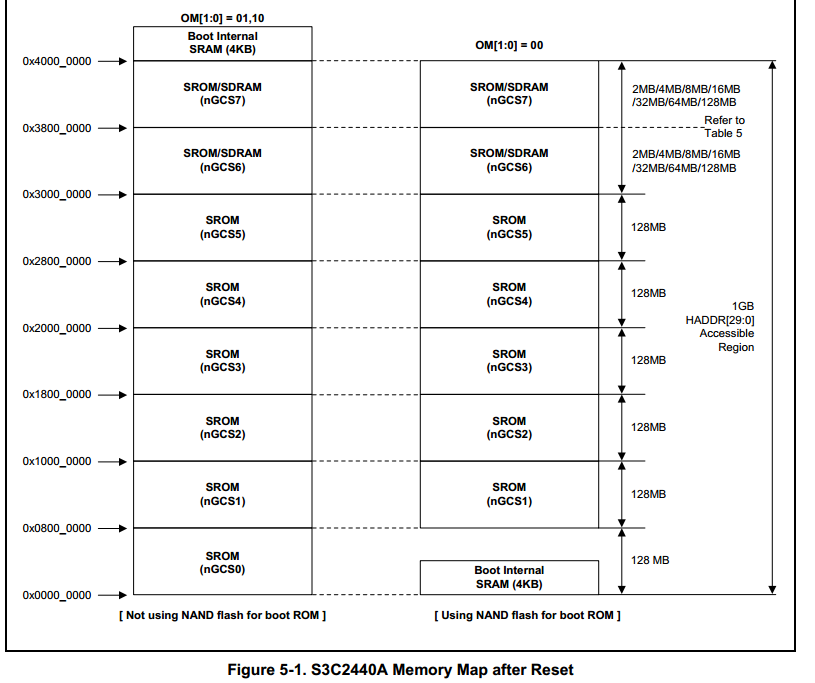

在S3C2440的datasheet《S3C2440A_UserManual_Rev13.pdf》中搜索map,可以在第5章中搜索到下图。

从此图中,可以得知

OM[1:0] = 01,10,Not using NAND flash for boot ROM

OM[1:0] = 00, Using NAND flash for boot ROM

而OM[1:0]又是什么呢?

从S3C2440的datasheet《S3C2440A_UserManual_Rev13.pdf》中搜索OM,

可以在第50页“S3C2440A Signal Descriptions”(芯片信号描述)得到下面的表格。

|

Signal |

Input/ Output |

Descriptions |

|

OM[1:0] |

I |

OM[1:0] sets S3C2440A in the TEST mode, which is used only at fabrication. Also, it determines the bus width of nGCS0. The pull-up/down resistor determines the logic level during RESET cycle. 00: Nand-boot 01: 16-bit 10: 32-bit 11: Test mode |

只能在生产中才能将OM[1:0]设置成S3C2440A的测试模式;

此外,OM[1:0]还决定了nGCS0的总线宽度(后面可以知道:nGCS0对应bank0)。

在芯片RESET复位周期间,OM[1:0]上的上拉/下拉电阻确定其逻辑电平

00:Nand启动 01:16 位 10:32 位 11:测试模式

后面可以知道:

OM[1:0]=01,代表的是nor flash的数据宽度为16位。

OM[1:0]=10,代表的是nor flash的数据宽度为32位。

从而,可以得出结论

2440启动方式有两种启动方式:NOR FLASH启动或NAND FLASH启动。

如何选择从那种方式启动呢?

答案是:通过2440启动方式OM0和OM1引脚来选择。

在S3C2440的datasheet《S3C2440A_UserManual_Rev13.pdf》中第5章还可以得到:

BANK0(nGCS0)的数据总线应当配置为16位或32位的宽度。因为BANK0是作为引导ROM的bank(映射到0x0000_0000),应当在第一个ROM访问前决定BANK0的总线宽度,其依赖于复位时OM[1:0]的逻辑电平。

|

OM1(操作模式1) |

OM0(操作模式0) |

引导ROM数据宽度 |

|

0 |

0 |

Nand Flash模式 |

|

0 |

1 |

16位 |

|

1 |

0 |

32位 |

|

1 |

1 |

测试模式 |

从JZ2440原理图NOR FLASH电路可以得知,使用的NOR FLASH的数据总线宽度为16位。

(NOR FLASH使用了LDATA0到LDATA15,共16根,即NOR FLASH的数据总线宽度为16位)

从而,我们只会使用到OM1=0,OM0=0或1这两种情况。

从而,可以得出下面的结论:

| OM1 | OM0 | 说明 |

| 0 | 1 | nor flash启动 |

| 0 | 0 | nand flash启动 |

从JZ2440原理图中,启动引脚配置OM0和OM1的原理图如下:

(下图为开发板的启动选择的拨码开关)

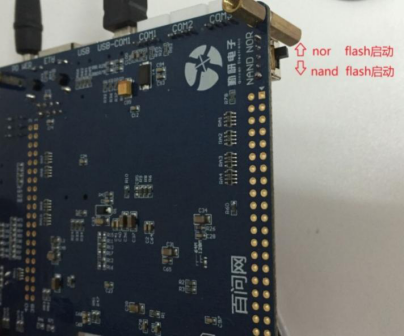

在开发板的PCB中,如图:

补充:

一般芯片有多种启动方式,而这些启动方式都可以由配置引脚来选择。芯片在启动时读取这些配置引脚的电平,就可以判断从那种方式启动。通常在研发阶段的实验板或者很多学习板(如:JZ2440)通常采用开关或跳线帽等方式来将配置引脚的电平置为高电平或置为低电平。在出厂时, 配置引脚一般通过上下拉电阻来设置电平。

1 .从NOR FLASH启动

从NOR FLASH启动时,由前面的图1,由nGCS0控制的bank0直接连接了nor flash,而bank0能访问的地址范围为:256M(0X00000000----0X08000000),JZ2440开发板使用的nor flash大小为2M(0X00000000----0X00200000),从而S3C2440芯片的物理地址(0X00000000----0X00200000)就由nor flash来占据。

选择从NOR FLASH启动,上电,S3C2440芯片就会去运行nor flash上地址为0x0处的指令。从后面的实验中,可以清楚的知道,读nor flash可以像读内存那样读,但是要用额外的命令向nor flash写入数据。如果nor flash像内存那样读和那样写,那nor flash完全可以被内存所替代。

2. 从NAND FLASH启动

在看本节内容之前,建议仔细看S3C2440A的datasheet《S3C2440A_UserManual_Rev13.pdf》的第6章,对S3C2440芯片对nand flash的支持有一个大概的认识。

使用nand flash的理由

目前的NOR Flash存储器价格较高,相对而言SDRAM和NAND Flash存储器更经济,这样促使了一些用户在NAND Flash中执行引导代码,在SDRAM中执行主代码。

可以得到一点:NAND Flash存储器更经济。

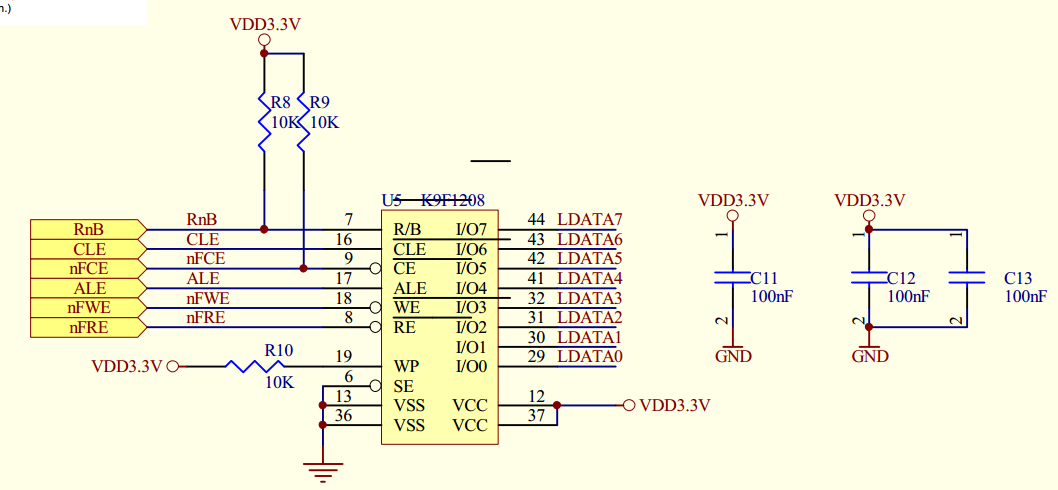

从NAND FLASH原理图来分析数据总线

可以在网上搜索nand flash的特点,其实我们从原理图或者nand flash的引脚数目,也可以分析出:nand flash无法像访问内存SDRAM那样直接访问。

JZ2440开发板使用的NAND FLASH大小为256M。如果像内存SDRAM那样,一次将地址全部发出,至少需要28根地址线才能完成256M的寻址。由JZ2440开发板使用的NAND FLASH

芯片手册可知,该芯片实际使用了29根地址线。多一根地址线访问范围更大一些。

而nand flash只有8根数据线和其他控制线,那怎么办?

通过查询NAND FLASH芯片手册知道,只能将地址分成多个字节,按照某种规则,分批传递给8根数据线。nand flash内部再按照某种规则,将几个批次的8根数据线上的数据合并成29根地址线的数据。从而,可以得出读写NAND FLASH都需要特定命令规则来控制传送的数据。

如何识别nand flash的类型

nand flash的页容量有大页(2k)/小页(512字节),总线宽度有8位/16位,如何区分开发板使用的哪一类型的NAND FLASH呢?

从S3C2440A的datasheet《S3C2440A_UserManual_Rev13.pdf》的第6章,可以得到NAND FLASH启动时的引脚配置:

|

引脚 |

说明 |

|

OM[1:0] = 00 |

使能NAND Flash存储器引导启动 |

|

NCON |

NAND Flash存储器选择(普通/先进) 0:普通NAND Flash(256字或512字节页大小, 3或4个地址周期) 1:先进NAND Flash(1K 字或2K 字节页大小,4或5个地址周期) |

|

GPG13 |

NAND Flash存储器页容量选择 0:页=256字 (NCON=0)或页=1K字 (NCON=1) 1:页=512字节(NCON=0)或页=2K字节(NCON=1) |

|

GPG14 |

NAND Flash存储器地址周期选择 0:3个地址周期(NCON=0)或4个地址周期(NCON=1) 1:4个地址周期(NCON=0)或5个地址周期(NCON=1) |

|

GPG15 |

NAND Flash存储器总线宽度选择 0:8位宽度 1:16位宽度 |

当复位时,芯片的NAND Flash控制器通过读取引脚NCON、GPG13、GPG14、GPG15的电平来得到外接的NAND FLASH的页大小,地址周期,总线宽度等信息。

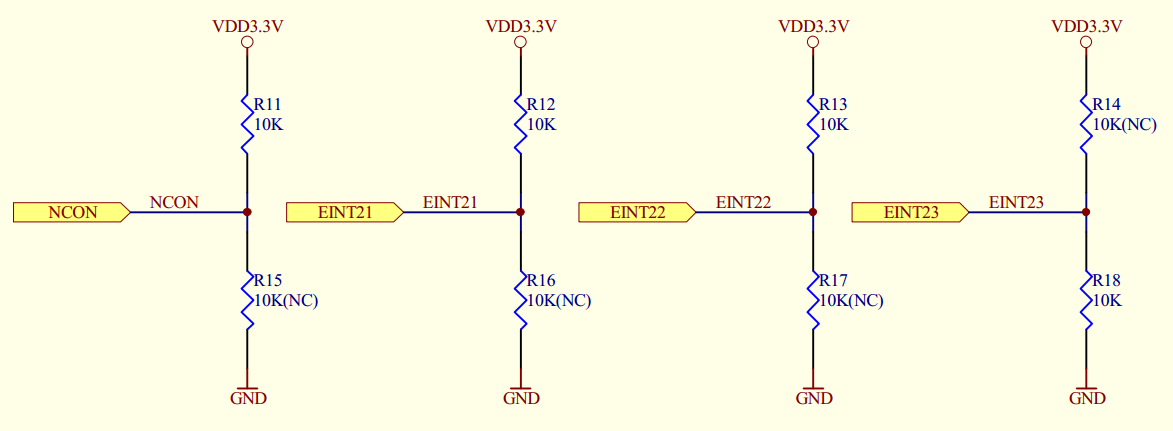

在JZ2440V2开发板上实际使用的是大页(一页有2K字节),5个地址周期,8位宽度的NAND FLASH。在JZ2440原理图中,关于NAND FLASH的启动引脚配置的原理图如下:

其中,R15,R16,R17,R14标记为NC,即这些电阻没有焊接。

从而NCON为高电平,EINT21为高电平,EINT22为高电平,EINT23为低电平。

从上图可以知道:

GPG13和 EINT21是同一信号。

GPG14和EINT22是同一信号。

GPG15和EINT23是同一信号。

从而NCON为高电平,GPG13为高电平,GPG14为高电平,GPG15为低电平。

从而S3C2440A芯片从nand flash启动时,让S3C2440A芯片确定外部挂接的是一个大页(一页有2K字节),5个地址周期,8位宽度的NAND FLASH。

第四小节 从nand flash启动流程

现在已经知道S3C2440A外部挂接的哪一类nand flash,那么就要准备去复制nand中的代码,然后去执行该代码。问题又来了,复制大小是多少?复制到哪里去?复制完接着做什么?并且这个复制过程也只能由S3C2440A的硬件来完成。

从S3C2440A的datasheet《S3C2440A_UserManual_Rev13.pdf》的第6章中:

S3C2440A boot code can be executed on an external NAND flash memory. In order to support NAND flash boot loader, the S3C2440A is equipped with an internal SRAM buffer called ‘Steppingstone’. When booting, the first 4 KBytes of the NAND flash memory will be loaded into Steppingstone and the boot code loaded into Steppingstone will be executed.

S3C2440A引导代码可以在外部NAND Flash存储器上存储。为了支持从NAND Flash启动,S3C2440A配备了一个内置的SRAM缓冲器,叫做“Steppingstone(垫脚石)”。从nand flash启动时,NAND Flash存储器的前4K字节将被加载到Steppingstone中并且执行加载到Steppingstone的引导代码。

复制大小为多少:4K。

复制到哪里去:Steppingstone(垫脚石)。

复制完接着做什么:执行加载到Steppingstone的引导代码。

从图1,OM[1:0]=00时,选择从nand flash启动,S3C2440A的前4K(0X00000000----0X00001000)就被BootSRAM(即:Steppingstone(垫脚石))所占据。

总结: