FPGA新起点V1开发板(五)——Modelsim软件的使用(联合仿真)

文章目录

一、简介

1.1 前仿真

主要是用于验证代码的功能是否正确,不考虑电路的延迟

1.2 后仿真

二、联合仿真

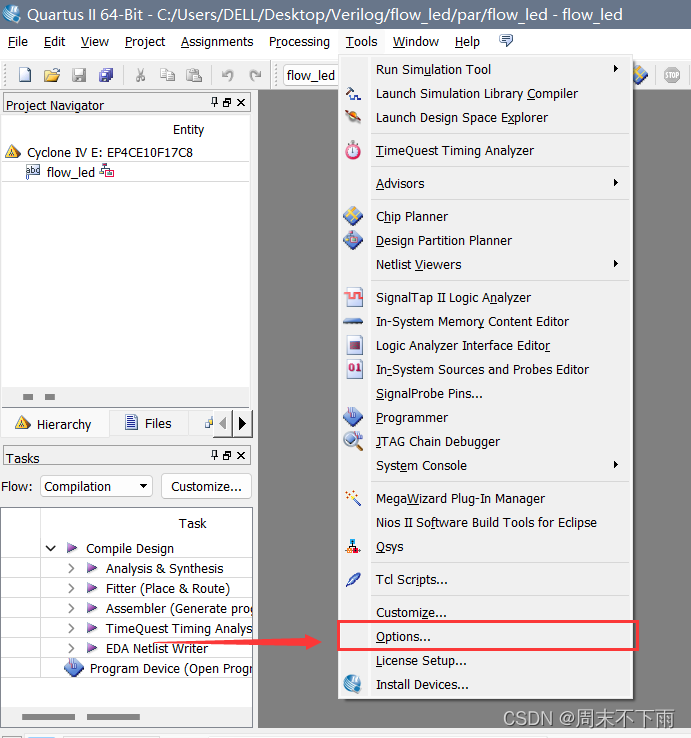

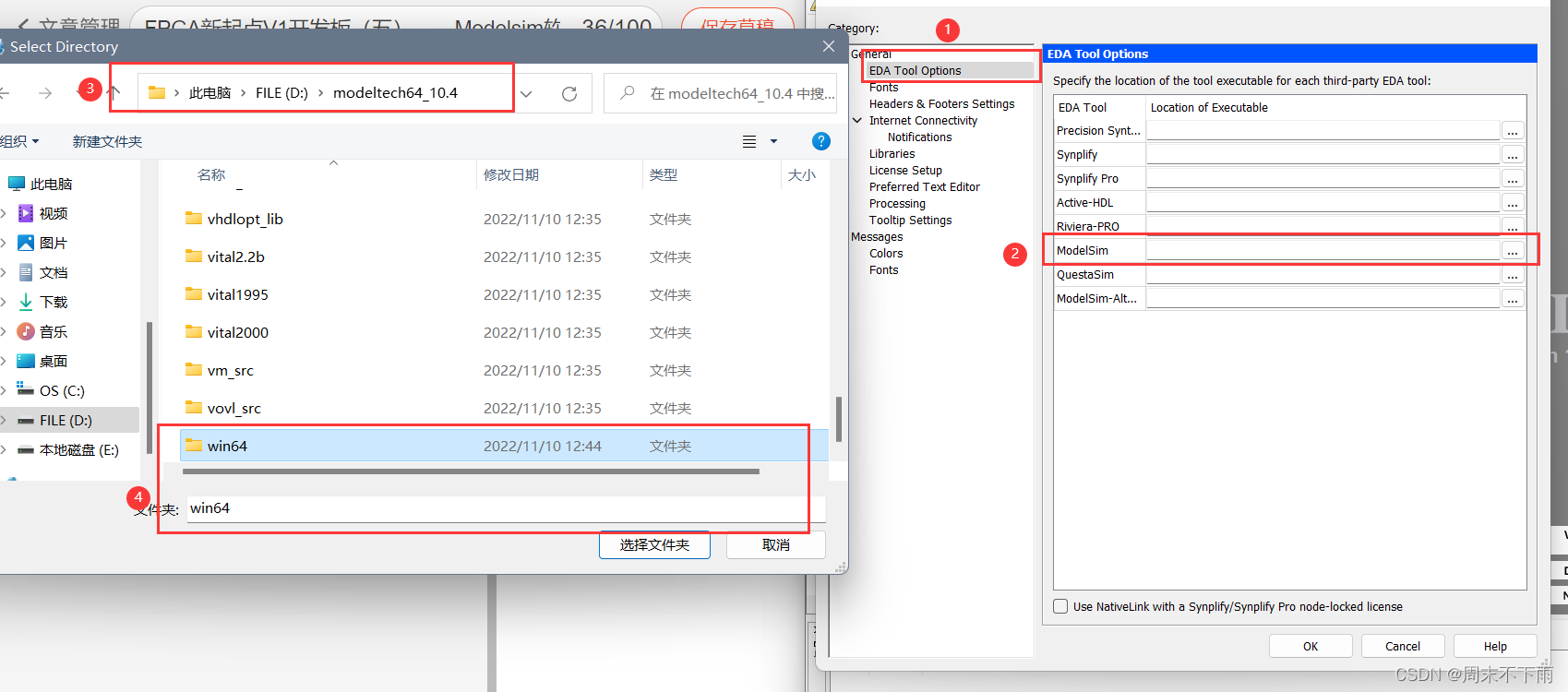

2.1 选择modesim的安装路径

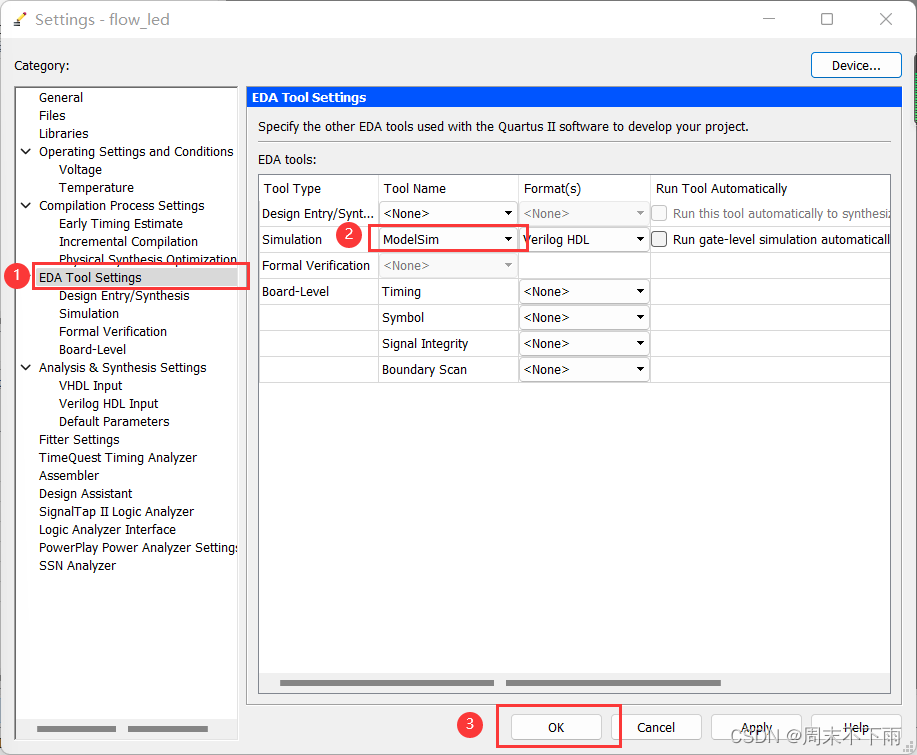

2.2 设置选择eda的工具

已经关联好

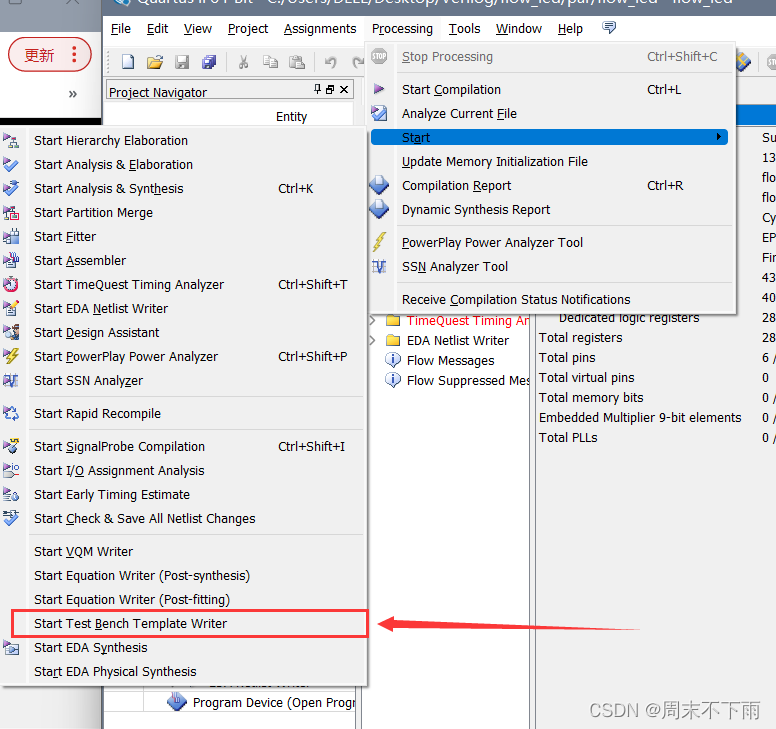

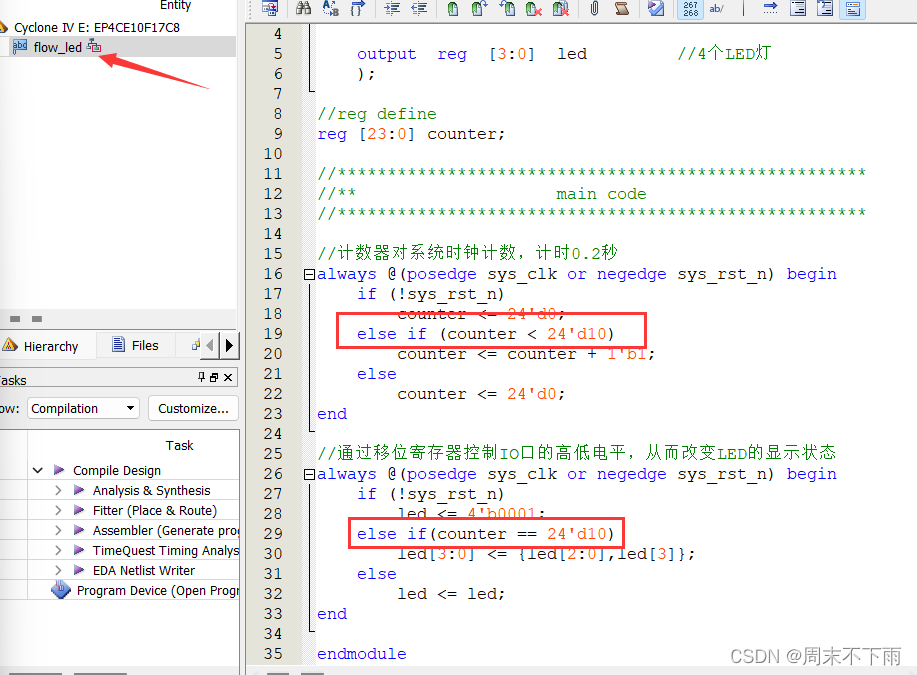

2.3 test bench文件

为顶层文件提供激励,如系统时钟和复位信号,quartes里面有模板

2.4 打开test bench文件

根据下面的路径

通过file的open

2.5 给系统时钟和复位信号赋初值

timescale 1 ps/ 1 ps,前面是仿真的单位后面是仿真的精度,修改成ns

initial

begin

sys_clk = 1'b0; //将系统时钟赋为0

sys_rst_n = 1'b0; //将复位信号赋为0

#100 sys_rst_n = 1'b1; //延时100ns后,复位信号拉高

#1000 $stop;//增加停止条件,运行1微秒后停止

end

//产生时钟的翻转信号,系统时钟是50MHz,则周期是20ns,则每延时10ns系统时钟翻转一次

always #10 sys_clk = ~sys_clk;

endmodule

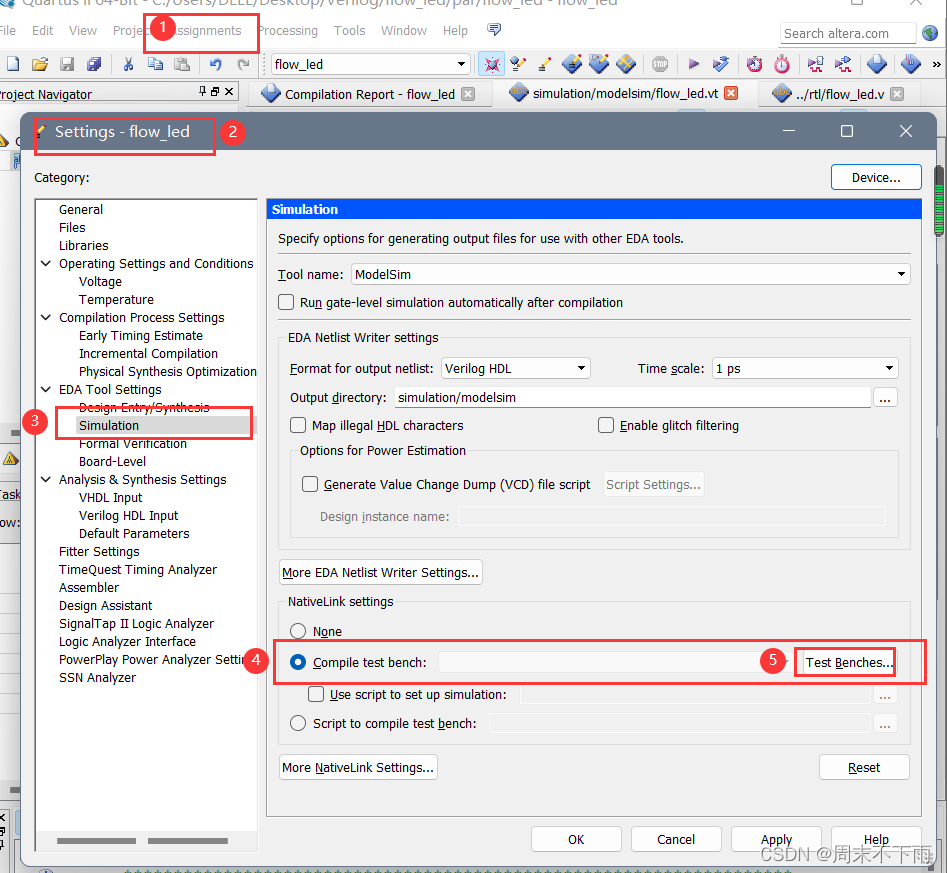

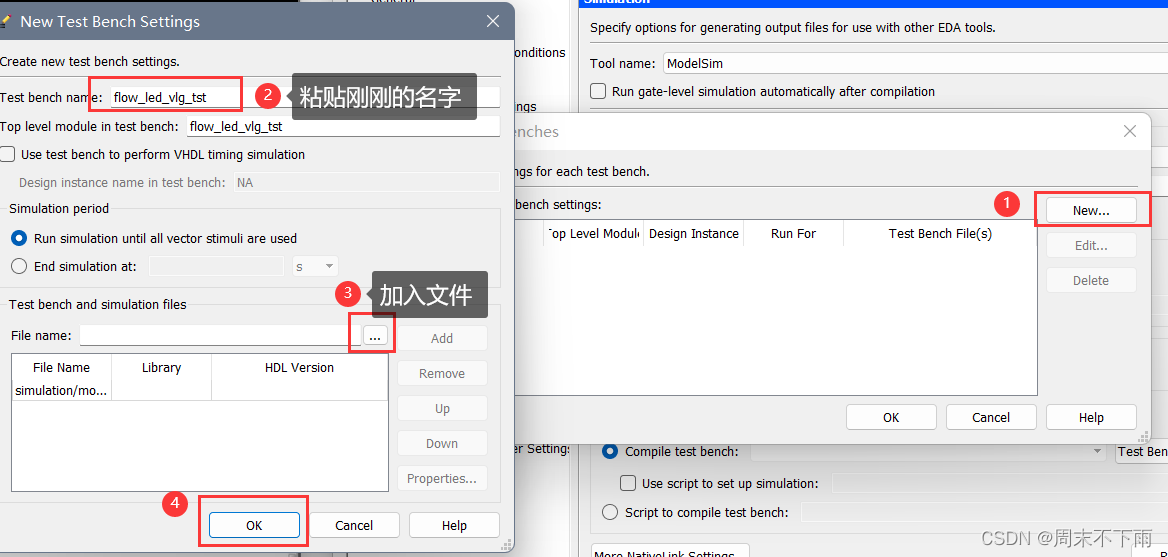

2.6 配置仿真功能

复制test bench的文件名

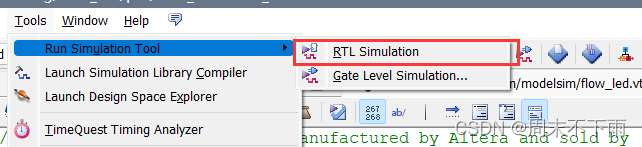

三、RTL仿真

RTL功能仿真

3.1 打开波形窗口

点击最下面,可隐藏路径

右边是几进制显示,这里选择二进制

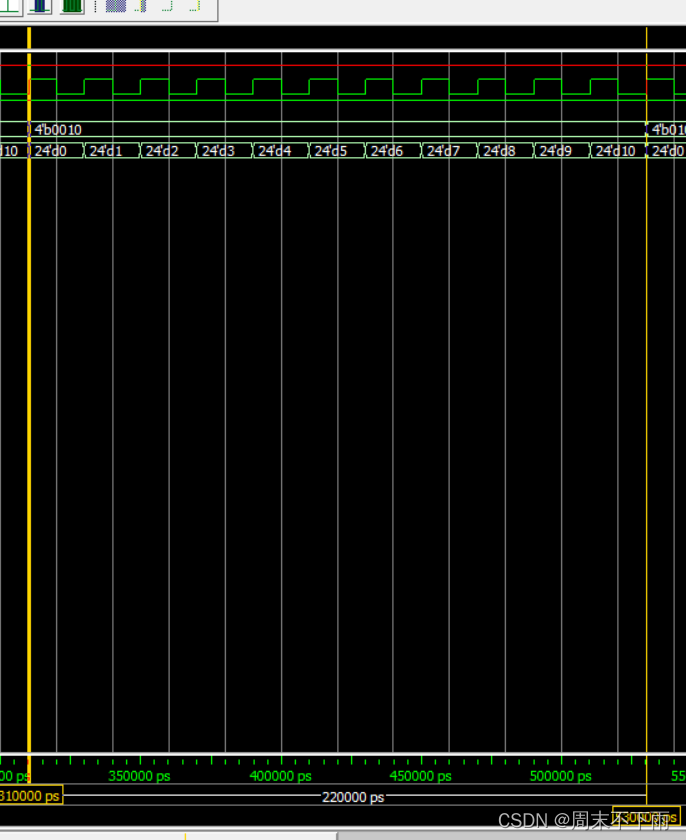

3.2添加内部信号

可以看出count是11次

四、时序仿真

需要编译

直接run

有一点误差