17.TLB

我们只想读4个字节,但我们要经过如下的步骤

读取 4 字节的PDE 读取 4 字节的 PTE 读取 4 字节(int 占用4字节)的物理内存

在 10-10-12 分页模式下,CPU 每次要访问额外的访问 8 字节内存数据才能读取到数据

读取 8 字节 PDPTE 读取 8 字节 PDE 读取 8 字节 PTE 读取 4 字节的物理内存

在2-9-9-12 分页模式下,需要额外的访问 24 字节内存数据才能读取到数据。

还有可能出现四个字节不在同一个物理页上的情况,这样效率就会变得非常低,所以出现了快表:TLB(Translation Lookaside Buffer)

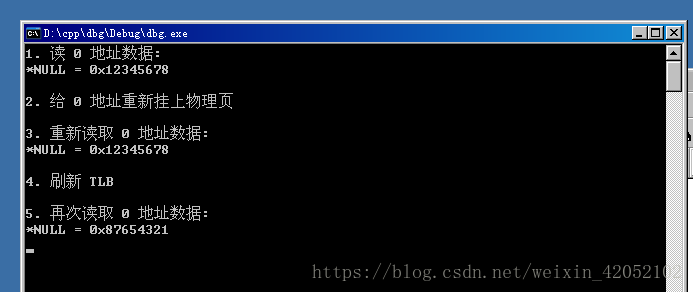

0x12345678如果已经拆分过,TLB表就会记录下次要用的时候直接找TLB,如果没有就只能经过如上的步骤。

- 为了提高效率,只能做记录。

- TLB是CPU内部做的表,来记录这些东西,这个表格是CPU内部的,和寄存器一样快

- 因为是在CPU 中开辟空间,容量不能太大

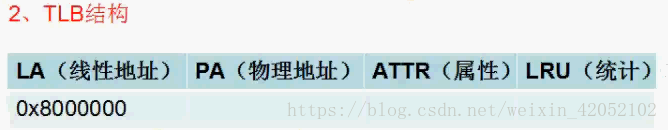

- ATTR (属性) :属性是PDPE PDE PTE三个属性 & 起来的,如果是10-10-12 ,就是PDE & PTE

- 不同的CPU这个表的大小不一样.

- 只要Cr3变了, TLB立马刷新,一核一套TLB.

如果 TLB 满了, LRU 统计信息就会把不经常使用的那一条抹掉,把新值写上。

操作系统的高2G映射基本不变,如果Cr3改了, TLB刷新重建高2G以上很浪费。

所以PDE和PTE中有个G位,如果G位为1刷新TLB时将不会刷新PDE/PTE的 G位为1的页,

当TLB满了,根据统计信息将不常用的地址废弃,最近最常用的保留…[

TLB种类

TLB在X86体系的CPU里的实际应用最早是从Intel的486CPU开始的,在X86体系的CPU里边,一般都设有如下4组TLB:

如果你的CPU只有一核,那就只有一组TLB

- 第一组:缓存一般页表(4K字节页面)的指令页表缓存(Instruction-TLB) ;

- 第二组:缓存一般页表(4K字节页面)的数据页表缓存(Data-TLB);

- 第三组:缓存大尺寸页表(2M/4M字节页面)的指令页表缓存(Instruction-TLB) ;

- 第四组:缓存大尺寸页表(2M/4M字节页面)的数据页表缓存(Instruction-TLB)

感受TLB的存在

浙公网安备 33010602011771号

浙公网安备 33010602011771号