分频器与锁相环配置应用笔记

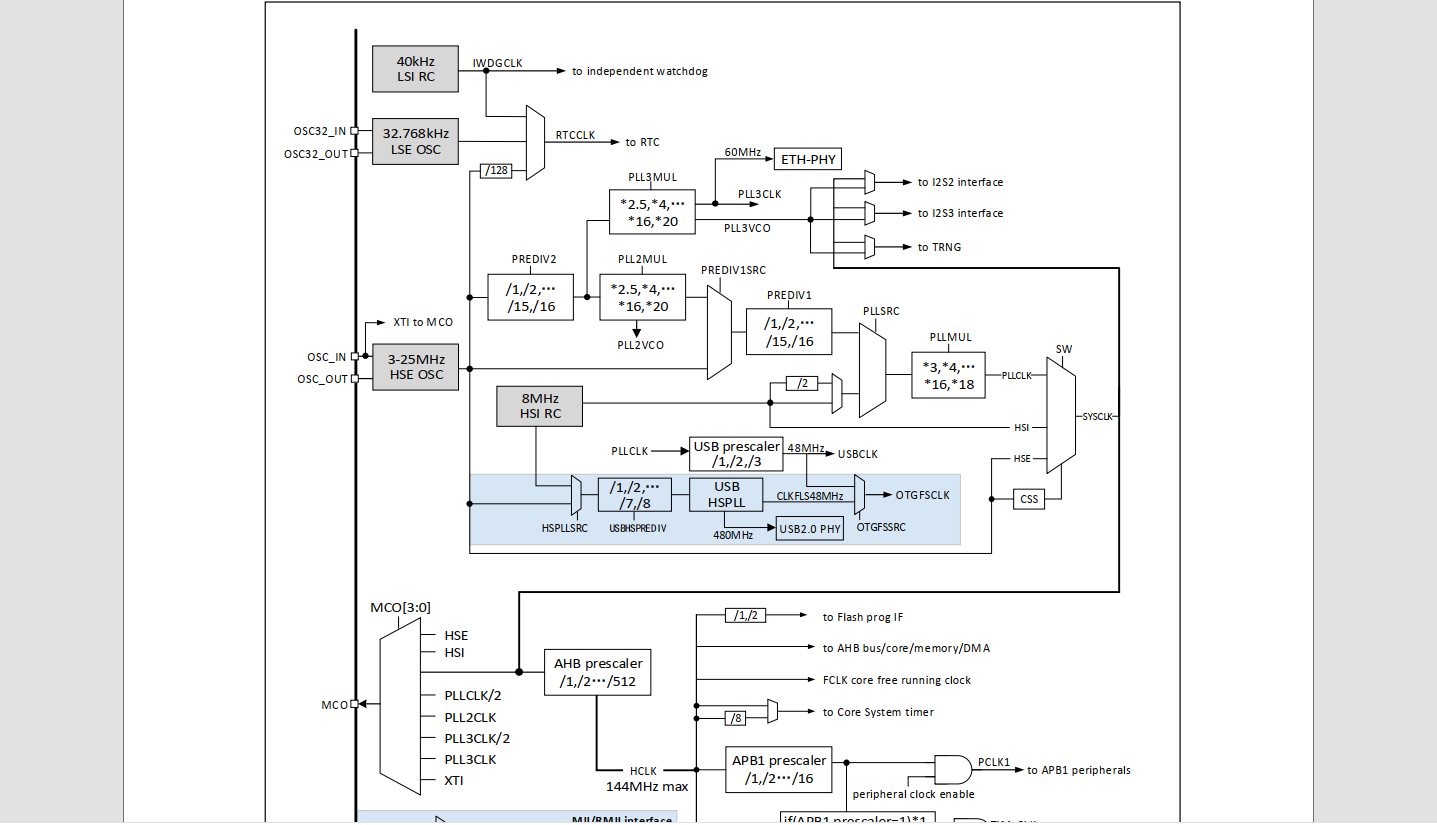

下图为CH32V305/307和CH32F205/207时钟树框图,在此,以CH32V307VCT6芯片,外置25MHz晶振为例,简述图中PREDIV与PLLMUL的配置方法,最终实现144MHz系统主频。

外置晶振信号可直接输入PREDIV1与PLLMUL,也可先通过PREDIV2与PLL2MUL后,再输入PREDIV1与PLLMUL。当外置晶振频率为25MHz时,可先使用PREDIV2进行5分频,然后使用PLL2MUL进行8倍频,再使用PREDIV1进行5分频,最后使用PLLMUL进行18倍频,即SYSCLK(144MHz)=25/5(PREDIV2/5)*8(PLL2MUL*8)/5(PREDIV1/5)*18(PLLMUL*18)。

时钟的修改涉及两个文件,分别是system_ch32v30x.c与ch32v30x.h,首先修改头文件中HSE_VALUE宏定义的值为外置晶振频率。

1. #define HSE_VALUE ((uint32_t)25000000) /* Value of the External oscillator in Hz */

然后在system_ch32v30x.c文件中找到SetSysClockTo144_HSE函数,第一步,在配置RCC_CFGR0前,先配置PREDIV2为5分频与PLL2MUL为8倍频,使能PLL2MUL并等待其就绪;第二步,在使能PLLMUL前,配置PREDIV1的时钟源为PLL2MUL且为5分频。

1. /* PLL configuration: PLLCLK = HSE * 18 = 144 MHz */

2. RCC->CFGR0 &= (uint32_t)((uint32_t)~(RCC_PLLSRC | RCC_PLLXTPRE | RCC_PLLMULL));

3.

4. RCC_PREDIV2Config(RCC_PREDIV2_Div5);

5. RCC_PLL2Config(RCC_PLL2Mul_8);

6. RCC_PLL2Cmd(ENABLE);

7. while( (RCC->CTLR & (1<<27)) == 0 )

8. {

9. }

10.

11. #ifdef CH32V30x_D8

12. RCC->CFGR0 |= (uint32_t)(RCC_PLLSRC_HSE | RCC_PLLXTPRE_HSE | RCC_PLLMULL18);

13. #else

14. RCC->CFGR0 |= (uint32_t)(RCC_PLLSRC_HSE | RCC_PLLXTPRE_HSE | RCC_PLLMULL18_EXTEN);

15. RCC_PREDIV1Config(RCC_PREDIV1_Source_PLL2, RCC_PREDIV1_Div5);

16. #endif

17.

18. /* Enable PLL */

19. RCC->CTLR |= RCC_PLLON;

20. /* Wait till PLL is ready */

21. while((RCC->CTLR & RCC_PLLRDY) == 0)

22. {

23. }

除此之外,在使用USB HS接口时,还应对USBHS_RCC_Init函数做进一步的调整,首先配置USBHS时钟为5分频,然后设置USBHSPLL参考时钟为5MHz。

1. RCC_USBHSConfig( RCC_USBPLL_Div5 );

2. RCC_USBHSPLLCKREFCLKConfig( RCC_USBHSPLLCKREFCLK_5M );

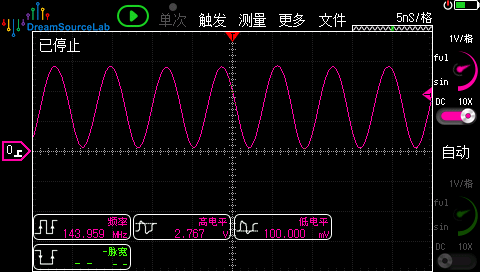

其他系列芯片不再一一赘述,使用时应首先查阅时钟树框图,参考应用手册中具体的配置要求,并结合上述方法进行操作。最终还可以通过MCO将SYSCLK进行输出,使用示波器进行简单的测量。

浙公网安备 33010602011771号

浙公网安备 33010602011771号