MCU晶振负载电容的计算方法

MCU晶振谐振电容的计算方法

在实际应用中使用外置晶振(HSE)作为单片机时钟源时,经常会有工程师遇到定时精度误差较大,或者上电后系统不工作,需要手动复位一次才能正常工作的情况,此类现象多数都是外置晶振(HSE)的谐振电容选择不当导致。

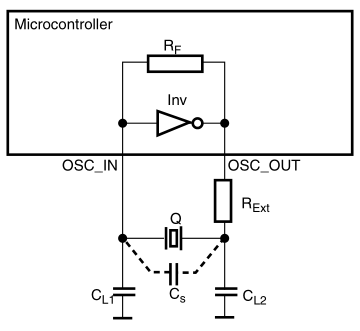

单片机的晶振电路经常使用的是皮尔斯振荡电路,具体电路如下图所示。

▲ 皮尔斯振荡电路

晶振有一个重要的参数,即负载电容CL(Load capacitance),它是电路中跨接晶体两端的总的有效电容 (不是晶振外接的匹配电容),选择好晶振外接的匹配电容使得晶振两端总的有效电容与负载电容值相等的并联电容,就可以得到晶振标称的谐振频率。

MCU的管脚有OSCIN和OSCOUT,一般会连两个电容CL1和CL2,CL1和CL2只是负载电容的一部分,而且大家要注意到,CL1和CL2从晶振来看它们是串联的,只不过它们之间有一个公共点接地。真正的负载是CL1和CL2,MCU OSCIN/OSCOUT这两个管脚自身对地以及PCB走线形成的寄生电容COSCIN,COSCOUT, 还有一个是晶振本身的CS,这几部分共同组成了真正的负载。

并联COSCIN,COSCOUT一般在3~8pf(和PCB制造相关),CS也有1~2pf,也就是说,即使不连接CL1和CL2晶振电路的拓扑也是完整的,而且已经有了一定的电容负载,这也就是用户会发现即使没有连接CL1和CL2,电路往往也能起振的原因。

负载电容的公式如下所示:

CL=CS+(CD×CG)/(CD+CG )

其中,CS为晶体两个管脚间的寄生电容(Shunt Capacitance)

CD表示晶体振荡电路输出管脚到地的总电容,包括PCB走线电容CPCB、芯片管脚寄生电容CO、外加匹配电容CL2,即CD=CPCB+CO+CL2

CG表示晶体振荡电路输入管脚到地的总电容,包括PCB走线电容CPCB、芯片管脚寄生电容CI、外加匹配电容CL1,即CG=CPCB+CI+CL1

一般CS为1pF左右,CI与CO一般为几个皮法,具体可参考芯片或晶振的数据手册,CPCB一般5pF左右。一般近似的认为COSCO = COSCI,通常为了保持晶体的负载平衡,在实际应用中一般要求CL1 = CL2,这样就可以大致的估算出

CL1 = CL2 =(CL – CS)* 2 - CPCB - CI

我们在电路设计时,要尽量使整个晶振电路靠近MCU,同时要尽量避免在晶振电路旁有其他高频信号、大电流的信号,以及有较长走线的信号,从而保证晶振工作时有较小的负载、正确的拓扑,和相对稳定的电磁工作环境。通常为了让晶振上电时快速起振,一般让CL2 > CL1。

在允许的范围内CL1、CL2值越小越好;如果晶振总体负载容值偏差大了会带来两个问题,一个是增加起振时间,另一个是影响晶振的精度。

在选择晶振封装时尽量选择小封装的晶振,封装小的晶振寄生电容也相对更小。

晶振电路内部是一个反相器,反相器工作在放大区,同时放大器的内部还并联一个电阻(RF),这个电阻构成了反馈电路,同时也是用来调整晶振的工作点的。一般情况下用户不需要在外部电路再加入OSC1和OSC2的并联电阻,但还是可以在需要的情况下通过在外部并联电阻(一般来说阻值为M级)来对放大器的工作点进行微调。还有一个方法是在晶振的放大器输出管脚上串一个电阻。这个电阻一般有两个作用,一个作用是用来做选频,另一个作用是限制晶振驱动电路的输出电流,保证晶振工作在一个稳定的频点上,不会把晶振烧坏。

浙公网安备 33010602011771号

浙公网安备 33010602011771号