|

|

Posted on

2017-12-08 10:16

warmbeast

阅读( 2680)

评论()

编辑

收藏

举报

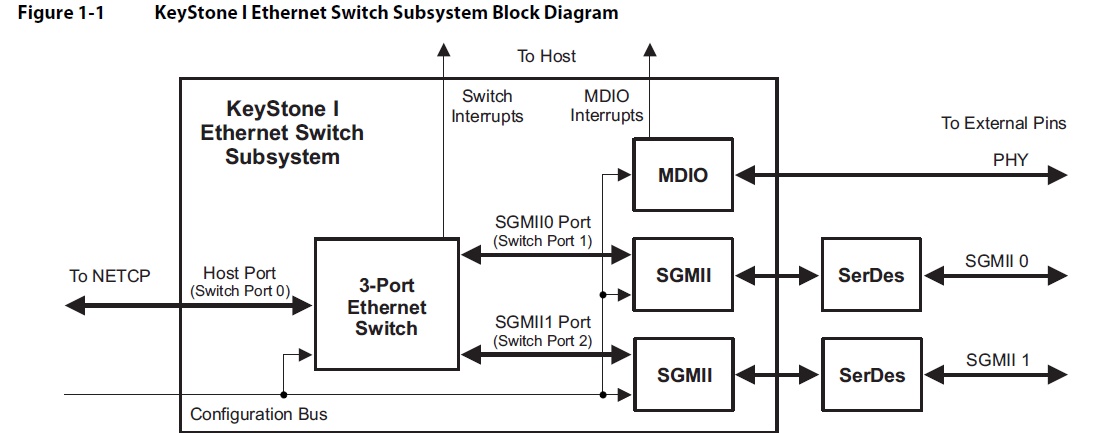

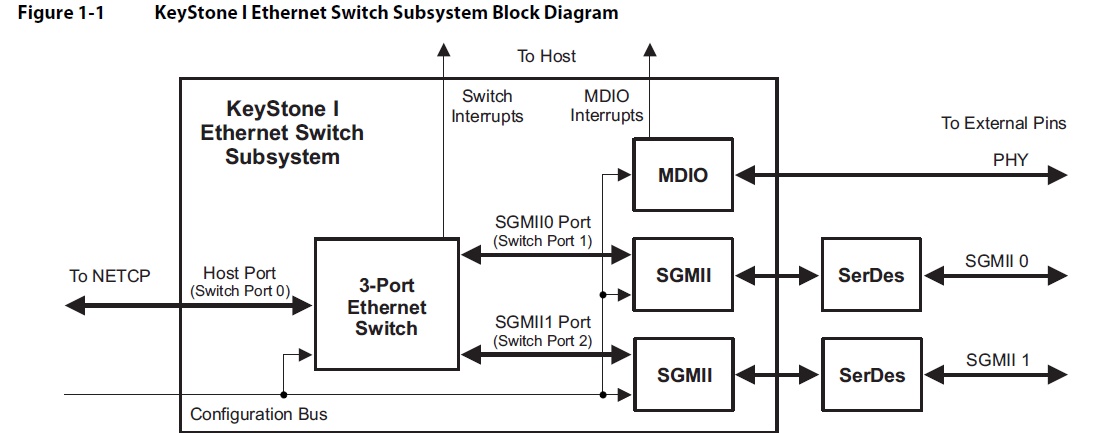

1、C6678 Keystone1架构的GbE switch subsystem如图所示:

2、从图中可以看到MAC层与物理层PHY芯片的连接接口是由SGMII+SerDES构成,SGMII是以太网MAC与PHY之间的媒体接口,SerDES为可编程的串行接口,为差分输入输出。

3、网上很多资料说SGMII接口电器特性与SerDES兼容,可以配置成串行接口,可以直接与PHY芯片连接,但是C6678为什么设计成SGMII+SerDES这种模式?

4、解释3的原因:SGMII只是一个普通的高速串行接口,用来连接MAC与PHY芯片,类似GMII和RGMII,只不过GMII和RGMII都是并行的,而且需要随路时钟,PCB布线麻烦;而SGMII是串行的,不需要另外提供时钟,具有8b/10b编码,速率为1.25Gb。SerDES一般集成在高端FPGA,或者专用加串/解串器IC上。另外:C6678采用SGMII+SerDES这种模式,可能是为了测试SGMII和SerDES进行内部循环通信;还有SGMII的发送接口和接收接口是分开独立的,发送数据时,SGMII的发送接口可以进行8b/10bB编码,将发送数据编码为SerDES接口需要的编码格式;接收数据时,SerDES对从PHY接收的数据进行8b/10bB编码,再传送给SGMII接收接口,接收接口对8b/10bB编码数据进行解码,完成数据接收;如果SGMII与PHY可以直接相连,就不用进行中间的8b/10bB编码解码,为什么要加上SerDes,反而更麻烦;因为8b/10bB编码后的数据抗干扰性更强,传输更稳定,所以中间通过SerDes传输;这说明SGMII与PHY之间不能直接传输8b/10bB编码信号吗。。。。

|