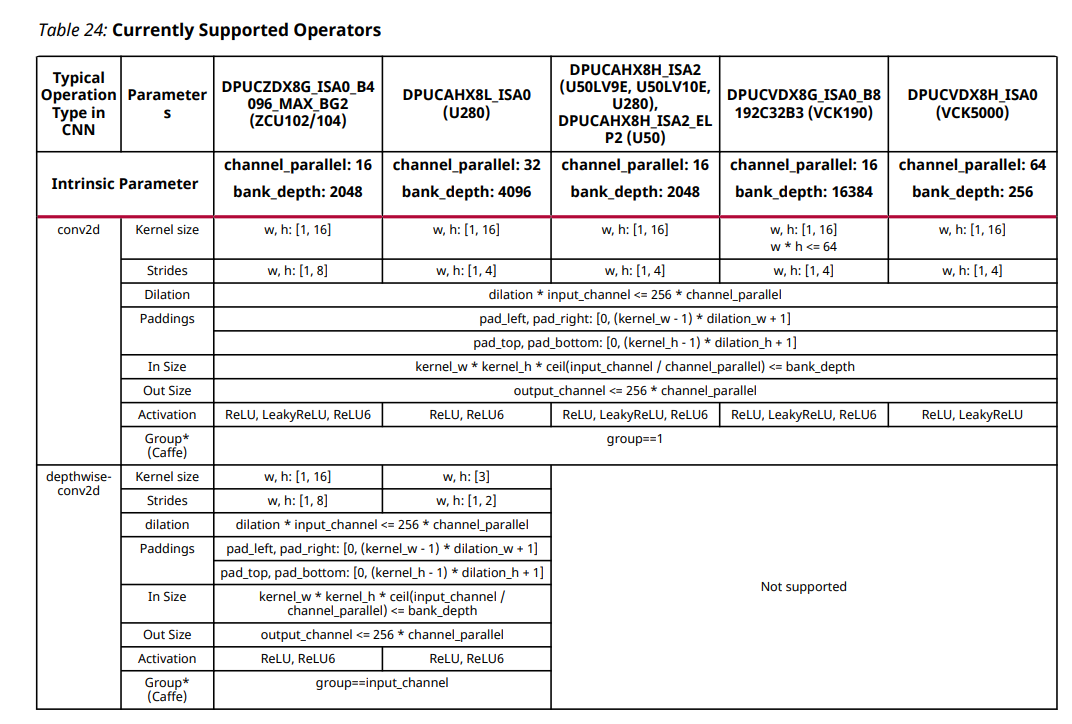

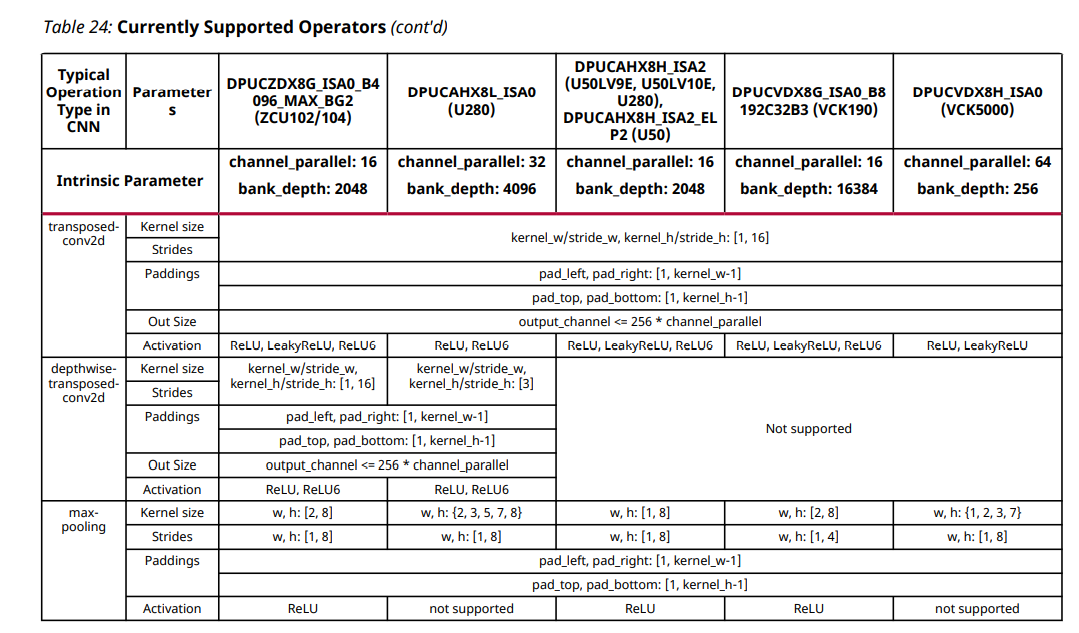

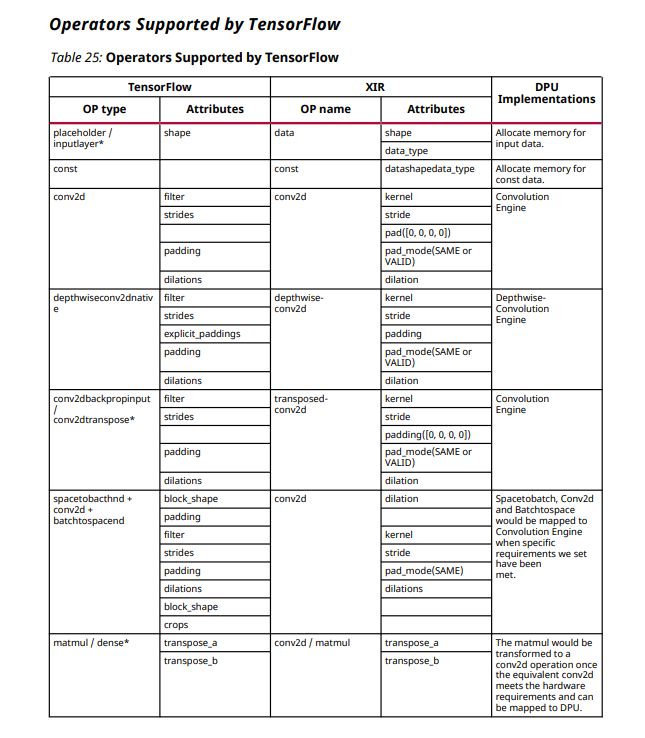

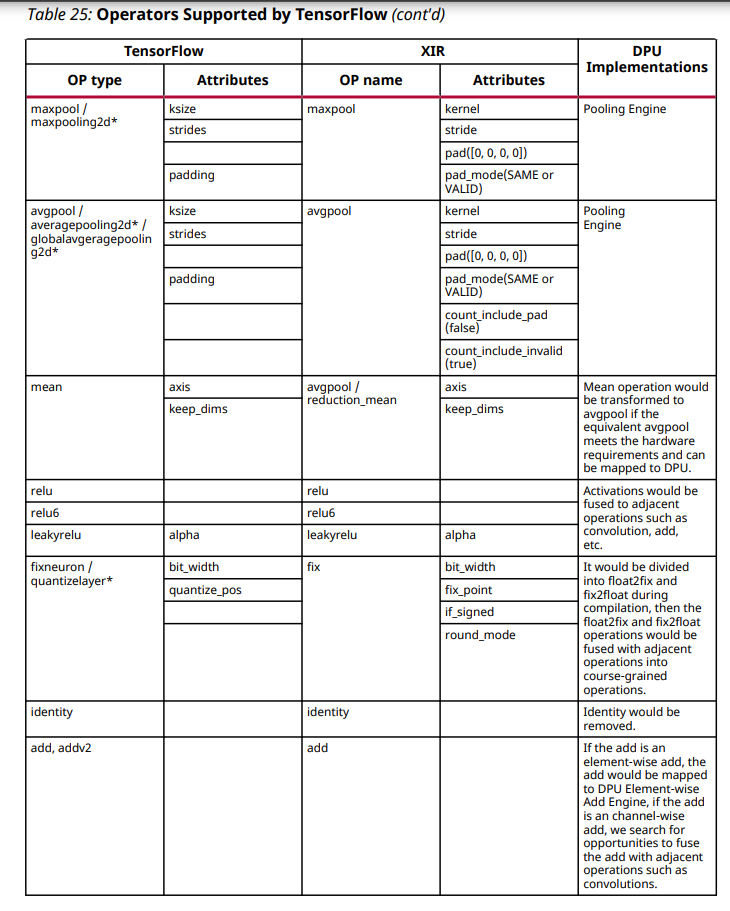

Supported OPs and DPU Limitations

Currently Supported Operators

source:https://www.xilinx.com/html_docs/xilinx2019_2/vitis_doc/zmw1606771874842.html

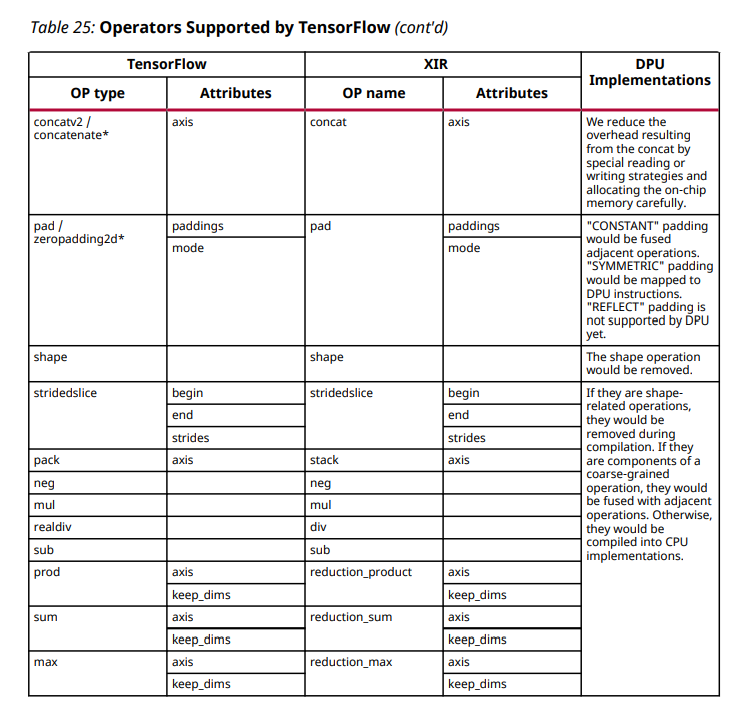

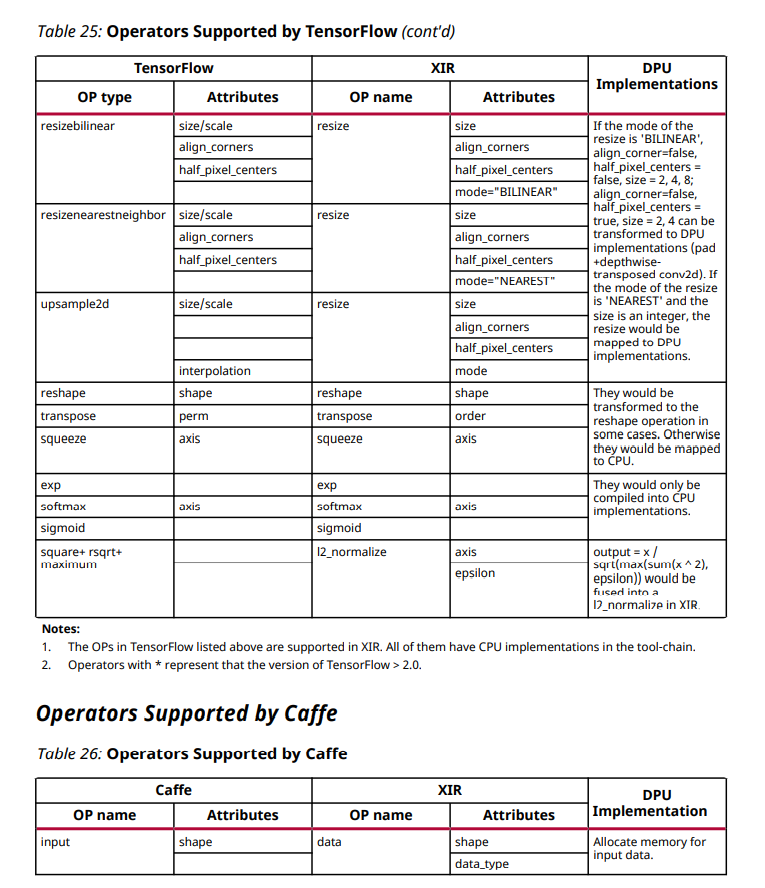

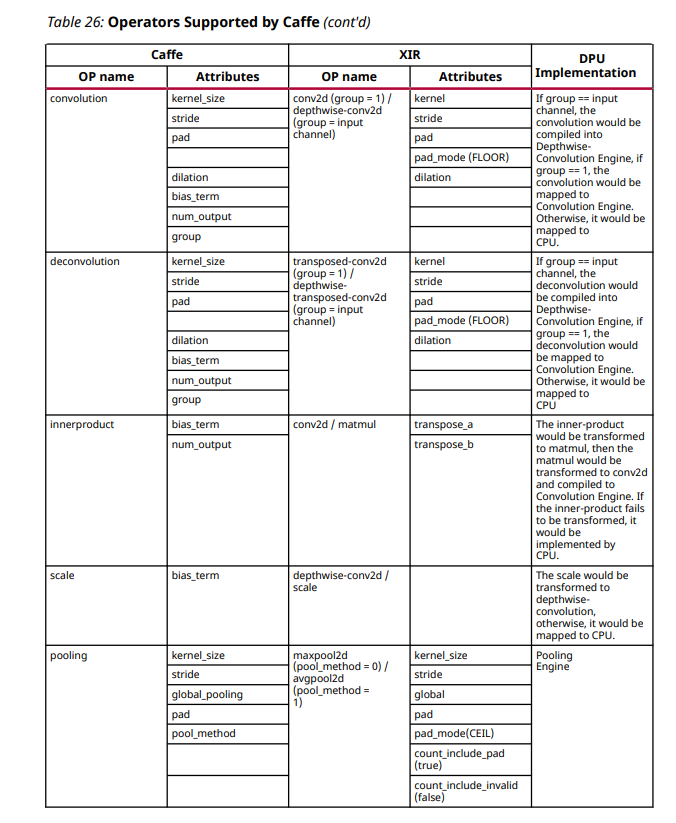

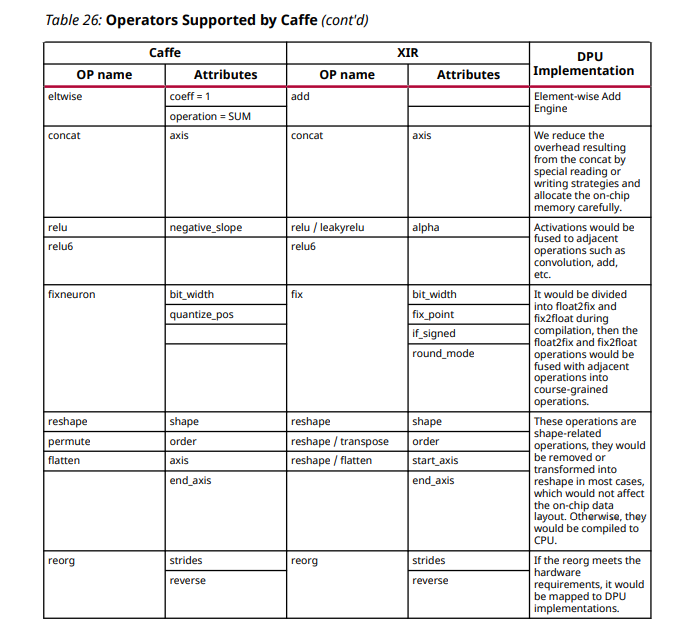

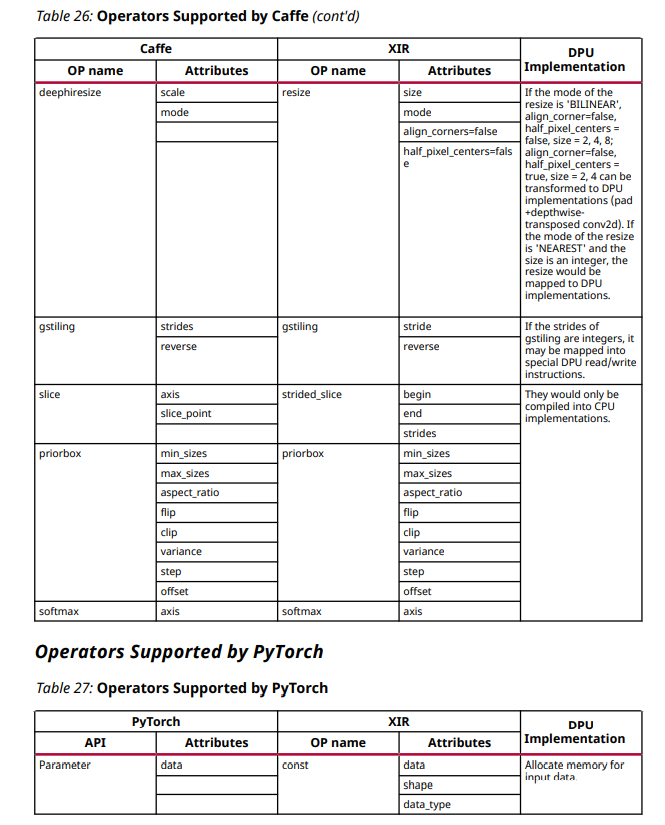

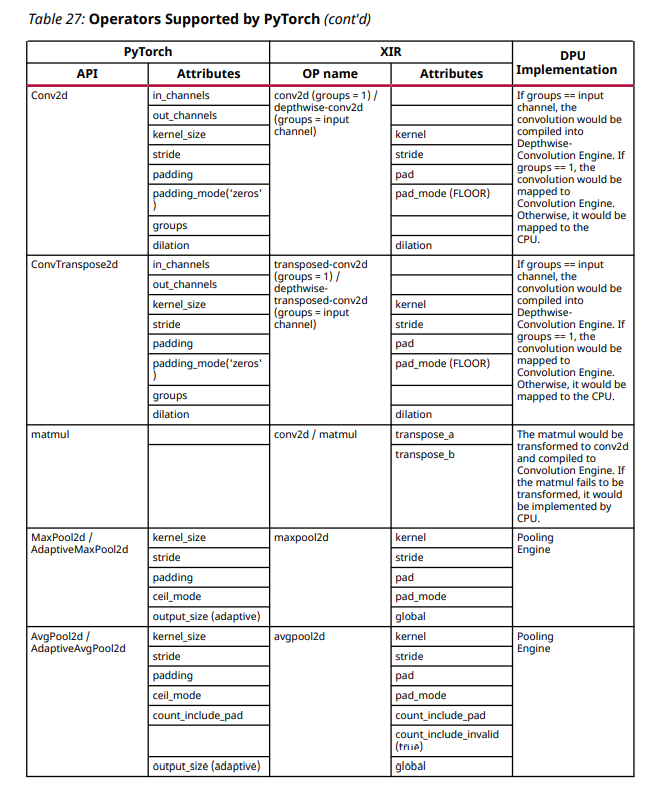

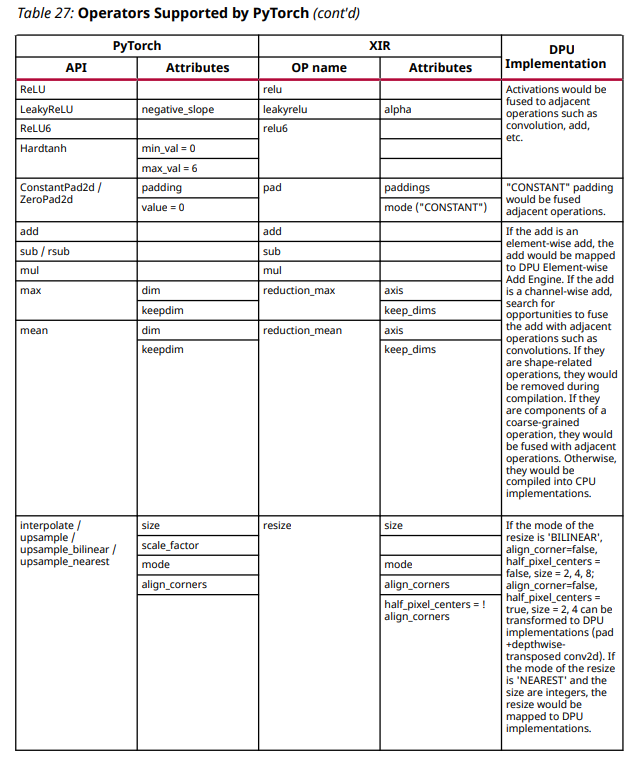

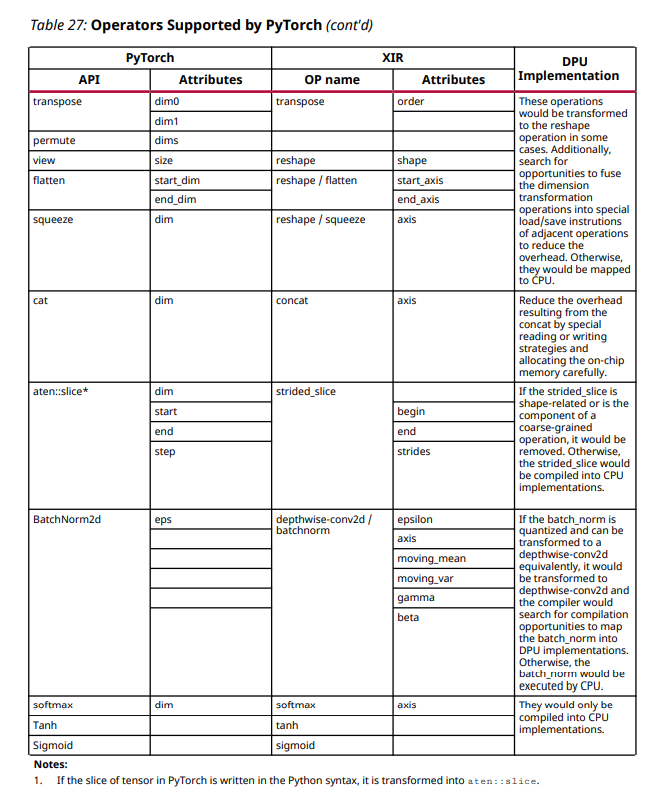

Xilinx is contnuously improving the DPU IP and the compiler to support more operators with beter performance. The following table

lists some typical operatons and the confguratons such as kernel size, stride, etc. that the DPU can support. If the operaton

confguratons exceed these limitatons, the operator will be assigned to the CPU. Additonally, the operators that the DPU can

support are dependent on the DPU types, ISA versions, and confguratons.

In order to make DPU adaptable to a variety of FPGA devices, some kinds of DPU are confgurable. You can choose necessary engines,

adjust some intrinsic parameters and create your own DPU IP with TRD projects. But that means the limitatons can be very different

between confguratons. You can fnd more informaton about how will those optons impact on the limitatons in PG338. Or it is

recommended that you could try compiling the model with your own DPU confguraton. The compiler will tell you which operators

would be assigned to CPU and why they would be so. The table shows a specifc confguraton of each DPU architeciture.

浙公网安备 33010602011771号

浙公网安备 33010602011771号