verilog代码:

// Build a 100-bit left/right rotator, with synchronous load and left/right enable.

//A rotator shifts-in the shifted-out bit from the other end of the register,

// unlike a shifter that discards the shifted-out bit and shifts in a zero. If enabled,

// a rotator rotates the bits around and does not modify/discard them.

// 移出的一位不会丢弃而是补在空缺的位置,即就是题目中的a rotator要求

// load: Loads shift register with data[99:0] instead of rotating.

// ena[1:0]: Chooses whether and which direction to rotate.

// 2'b01 rotates right by one bit

// 2'b10 rotates left by one bit

// 2'b00 and 2'b11 do not rotate.

// q: The contents of the rotator.

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @(posedge clk)

begin

if(load)begin

q <= data;

end

else begin

case(ena)

2'b01: q <= {q[0],q[99:1]};//拼接运算符号{,} ,向右移动1bit

2'b10: q <= {q[98:0],q[99]};//向左边移动1bit

2'b00,2'b11:q <= q; // 保持

default:

q<= q; //所有情况考虑完整的情况下,此处可以省略

endcase

end

end

endmodule

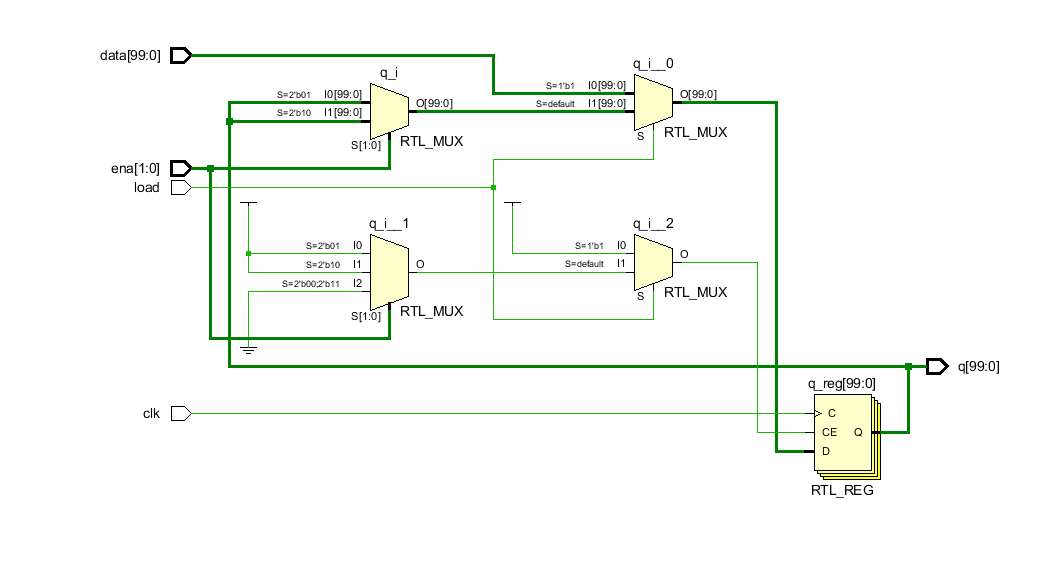

RTL原理图:

![]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号