FPGA-高斯滤波

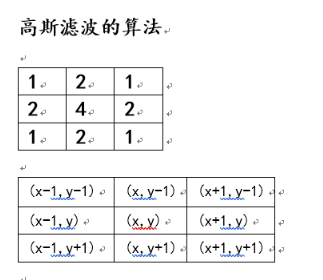

这里我选择的模板

实现步骤3步

1、每行做乘积

2、求和

3、右移4位

1 //高斯滤波 2 /* 模板 3 [ 1 2 1 ] 4 [ 2 4 2 ] * 1/16 5 [ 1 2 1 ] 6 */ 7 /* 3步 8 1、求乘积 9 2、求和 10 3、右移4 11 */ 12 `timescale 1ns/1ns 13 module gaussian_fliter( 14 clk, 15 rst_n, 16 matrixp11,matrixp12,matrixp13, 17 matrixp21,matrixp22,matrixp23, 18 matrixp31,matrixp32,matrixp33, 19 gaussian_data 20 ); 21 22 //********************** input and output ***********************// 23 input clk ; 24 input rst_n ; 25 input [7:0] matrixp11 ; 26 input [7:0] matrixp12 ; 27 input [7:0] matrixp13 ; 28 input [7:0] matrixp21 ; 29 input [7:0] matrixp22 ; 30 input [7:0] matrixp23 ; 31 input [7:0] matrixp31 ; 32 input [7:0] matrixp32 ; 33 input [7:0] matrixp33 ; 34 output reg [7:0] gaussian_data ; 35 //********************** main code ******************************// 36 //第一步求乘积 37 reg [11:0] row1_mul; 38 reg [11:0] row2_mul; 39 reg [11:0] row3_mul; 40 always@(posedge clk or negedge rst_n) begin 41 if(!rst_n) begin 42 row1_mul <= 'd0; 43 row2_mul <= 'd0; 44 row3_mul <= 'd0; 45 end 46 else begin 47 row1_mul <= matrixp11 + (matrixp12 << 1) + matrixp13; 48 row2_mul <= (matrixp21 << 1) + (matrixp22 << 2) + (matrixp23 <<1); 49 row3_mul <= matrixp31 + (matrixp32 << 1) + matrixp33; 50 end 51 end 52 //第二步求和 53 reg [11:0] sum; 54 always@(posedge clk or negedge rst_n) begin 55 if(!rst_n) begin 56 sum <= 'd0; 57 end 58 else begin 59 sum <= row1_mul + row2_mul + row3_mul; 60 end 61 end 62 //第三步移位 63 always@(posedge clk or negedge rst_n) begin 64 if(!rst_n) begin 65 gaussian_data <= 'd0; 66 end 67 else begin 68 gaussian_data <= sum[11:4]; 69 end 70 end 71 72 endmodule

`timescale 1ns/1ns module gaussian_fliter_top( //system clk , //像素时钟的同步,coms_clk , vga_clk rst_n , //复位信号 //coms or vga pre_vs, //前行同步 pre_hs, //前场同步 pre_en, //前数据有效 pre_img_Y, //数据灰度图像 post_vs, //输出行同步 post_hs, //输出场同步 post_en, //输出数据有效 post_img_Y //输出数据灰度图像 ); //**********************input and output ********************// //system input clk ; //像素时钟的同步,coms_clk , vga_clk input rst_n ; //复位信号 //coms or vga input pre_vs ; //前行同步 input pre_hs ; //前场同步 input pre_en ; //前数据有效 input [7:0] pre_img_Y ; //数据灰度图像 output post_vs ; //输出行同步 output post_hs ; //输出场同步 output post_en ; //输出数据有效 output [7:0] post_img_Y ; //输出数据灰度图像 //********************** main code **************************// wire [7:0] matrixp11,matrixp12,matrixp13; wire [7:0] matrixp21,matrixp22,matrixp23; wire [7:0] matrixp31,matrixp32,matrixp33; wire matrix_vs ; wire matrix_hs ; wire matrix_en ; Generate_Matrix_3x3_8bit Generate_Matrix_3x3_8bit( //system .clk (clk ), //像素时钟的同步,coms_clk , vga_clk .rst_n (rst_n ), //复位信号 //coms or vga .pre_vs (pre_vs ), //前行同步 .pre_hs (pre_hs ), //前场同步 .pre_en (pre_en ), //前数据有效 .pre_img_Y (pre_img_Y ), //数据灰度图像 .matrixp11 (matrixp11 ), .matrixp12 (matrixp12 ), .matrixp13 (matrixp13 ), .matrixp21 (matrixp21 ), .matrixp22 (matrixp22 ), .matrixp23 (matrixp23 ), .matrixp31 (matrixp31 ), .matrixp32 (matrixp32 ), .matrixp33 (matrixp33 ), .matrix_vs (matrix_vs ), .matrix_hs (matrix_hs ), .matrix_en (matrix_en ) ); //消耗3个时钟 wire [7:0] gaussian_data; gaussian_fliter gaussian_fliter( .clk (clk ), .rst_n (rst_n ), .matrixp11 (matrixp11 ), .matrixp12 (matrixp12 ), .matrixp13 (matrixp13 ), .matrixp21 (matrixp21 ), .matrixp22 (matrixp22 ), .matrixp23 (matrixp23 ), .matrixp31 (matrixp31 ), .matrixp32 (matrixp32 ), .matrixp33 (matrixp33 ), .gaussian_data (gaussian_data ) ); //延迟3个时钟 reg [2:0] matrix_vs_r; reg [2:0] matrix_hs_r; reg [2:0] matrix_en_r; always@(posedge clk or negedge rst_n) begin if(!rst_n) begin matrix_vs_r <= 3'd0 ; matrix_hs_r <= 3'd0 ; matrix_en_r <= 3'd0 ; end else begin matrix_vs_r <= {matrix_vs_r[1:0],matrix_vs}; matrix_hs_r <= {matrix_hs_r[1:0],matrix_hs}; matrix_en_r <= {matrix_en_r[1:0],matrix_en}; end end assign post_vs = matrix_vs_r[2]; assign post_hs = matrix_hs_r[2]; assign post_en = matrix_en_r[2]; assign post_img_Y = post_en ? gaussian_data:8'd0; endmodule

`timescale 1ns/1ns module gaussian_fliter_top_tb; //system reg clk ; //像素时钟的同步,coms_clk , vga_clk reg rst_n ; //复位信号 //coms or vga reg pre_vs ; //前行同步 reg pre_hs ; //前场同步 reg pre_en ; //前数据有效 reg [7:0] pre_img_Y ; //数据灰度图像 wire post_vs ; //输出行同步 wire post_hs ; //输出场同步 wire post_en ; //输出数据有效 wire [7:0] post_img_Y ; //输出数据灰度图像 initial clk = 1; always #5 clk = ~clk; initial begin rst_n = 0; pre_vs =0 ; pre_hs = 0; pre_en = 0; pre_img_Y = 0; #51; rst_n = 1; pre_vs = 1; #20; pre_hs = 1; #20; pre_en = 1; #60; pre_en = 0; #20; pre_hs = 0; #20; pre_hs = 1; #20; pre_en = 1; #60; pre_en = 0; #20; pre_hs = 0; #20; pre_hs = 1; #20; pre_en = 1; #60; pre_en = 0; #20; pre_hs = 0; #20; pre_hs = 1; #20; pre_en = 1; #60; pre_en = 0; #20; pre_hs = 0; #20; pre_hs = 1; #20; pre_en = 1; #60; pre_en = 0; #20; pre_hs = 0; $stop; end reg [7:0] shiftin; always@(posedge clk or negedge rst_n ) begin if(!rst_n) shiftin <= 'd1; else if(pre_en) shiftin <= shiftin + 1'b1; else shiftin <= shiftin; end gaussian_fliter_top gaussian_fliter_top( //system .clk (clk ), //像素时钟的同步,coms_clk , vga_clk .rst_n (rst_n ), //复位信号 //coms or vga .pre_vs (pre_vs ), //前行同步 .pre_hs (pre_hs ), //前场同步 .pre_en (pre_en ), //前数据有效 .pre_img_Y (shiftin ), //数据灰度图像 //output .post_vs (post_vs ), //输出行同步 .post_hs (post_hs ), //输出场同步 .post_en (post_en ), //输出数据有效 .post_img_Y (post_img_Y ) //输出数据灰度图像 ); endmodule