FPGA-均值滤波

均值滤波

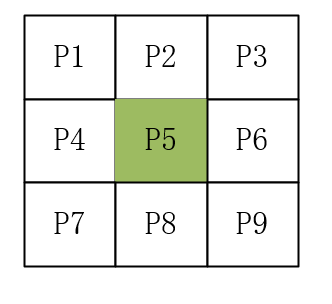

P5 = (P1+P2+P3+P4+P6+P7+P8+P9)/8 方便在硬件上做运算 >>3

同样用到的代码上几节提到的FPGA-shift_ram代码

代码

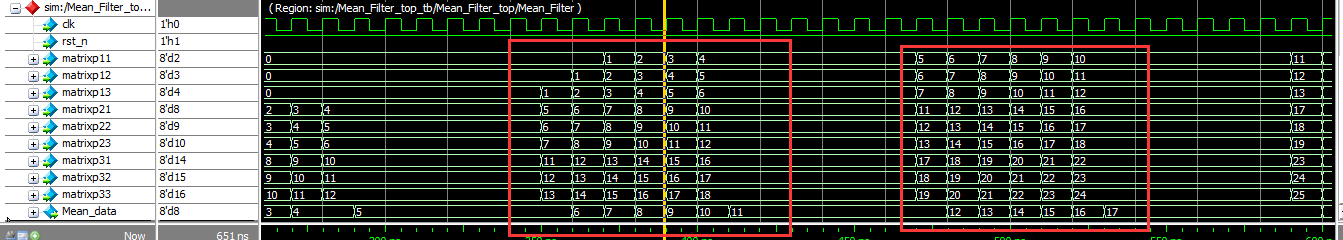

1 `timescale 1ns/1ns 2 3 4 module Mean_Filter( 5 clk , 6 rst_n , 7 matrixp11 , 8 matrixp12 , 9 matrixp13 , 10 matrixp21 , 11 matrixp22 , 12 matrixp23 , 13 matrixp31 , 14 matrixp32 , 15 matrixp33 , 16 Mean_data 17 18 ); 19 20 //********************* input and output ******************// 21 //system 22 input clk ; //像素时钟的同步,coms_clk , vga_clk 23 input rst_n ; //复位信号 24 input [7:0] matrixp11,matrixp12,matrixp13; 25 input [7:0] matrixp21,matrixp22,matrixp23; 26 input [7:0] matrixp31,matrixp32,matrixp33; 27 output reg [7:0] Mean_data; 28 29 30 //********************* main code *************************// 31 always@(posedge clk or negedge rst_n) begin 32 if(!rst_n) 33 Mean_data <= 'd0; 34 else 35 Mean_data <= (matrixp11+matrixp12+matrixp13+matrixp21+matrixp23+matrixp31+matrixp32+matrixp33)>>3; 36 end 37 38 39 endmodule

1 `timescale 1ns/1ns 2 3 4 module Mean_Filter_top( 5 clk , 6 rst_n , 7 pre_vs , 8 pre_hs , 9 pre_en , 10 pre_img_Y , 11 12 post_vs , 13 post_hs , 14 post_en , 15 post_img_Y 16 ); 17 18 //****************** input and output ******************// 19 //system 20 input clk ; //像素时钟的同步,coms_clk , vga_clk 21 input rst_n ; //复位信号 22 //coms or vga 23 input pre_vs ; //前行同步 24 input pre_hs ; //前场同步 25 input pre_en ; //前数据有效 26 input [7:0] pre_img_Y ; //数据灰度图像 27 28 output post_vs ; //输出行同步 29 output post_hs ; //输出场同步 30 output post_en ; //输出数据有效 31 output [7:0] post_img_Y ; //输出数据灰度图像 32 33 //****************** main code ************************// 34 35 wire [7:0] matrixp11,matrixp12,matrixp13; 36 wire [7:0] matrixp21,matrixp22,matrixp23; 37 wire [7:0] matrixp31,matrixp32,matrixp33; 38 wire matrix_vs; 39 wire matrix_hs; 40 wire matrix_en; 41 Generate_Matrix_3x3_8bit Generate_Matrix_3x3_8bit( 42 //system 43 .clk (clk ), //像素时钟的同步,coms_clk , vga_clk 44 .rst_n (rst_n ), //复位信号 45 //coms or vga 46 .pre_vs (pre_vs ), //前行同步 47 .pre_hs (pre_hs ), //前场同步 48 .pre_en (pre_en ), //前数据有效 49 .pre_img_Y (pre_img_Y ), //数据灰度图像 50 .matrixp11 (matrixp11 ), 51 .matrixp12 (matrixp12 ), 52 .matrixp13 (matrixp13 ), 53 .matrixp21 (matrixp21 ), 54 .matrixp22 (matrixp22 ), 55 .matrixp23 (matrixp23 ), 56 .matrixp31 (matrixp31 ), 57 .matrixp32 (matrixp32 ), 58 .matrixp33 (matrixp33 ), 59 .matrix_vs (matrix_vs ), 60 .matrix_hs (matrix_hs ), 61 .matrix_en (matrix_en ) 62 ); 63 wire [7:0] Mean_data; 64 Mean_Filter Mean_Filter( 65 .clk (clk ), 66 .rst_n (rst_n ), 67 .matrixp11 (matrixp11 ), 68 .matrixp12 (matrixp12 ), 69 .matrixp13 (matrixp13 ), 70 .matrixp21 (matrixp21 ), 71 .matrixp22 (matrixp22 ), 72 .matrixp23 (matrixp23 ), 73 .matrixp31 (matrixp31 ), 74 .matrixp32 (matrixp32 ), 75 .matrixp33 (matrixp33 ), 76 .Mean_data (Mean_data ) 77 ); 78 79 //延迟一个时钟 80 reg matrix_vs_r ; 81 reg matrix_hs_r ; 82 reg matrix_en_r ; 83 always@(posedge clk or negedge rst_n) begin 84 if(!rst_n) begin 85 matrix_vs_r <= 1'b0; 86 matrix_hs_r <= 1'b0; 87 matrix_en_r <= 1'b0; 88 end 89 else begin 90 matrix_vs_r <= matrix_vs; 91 matrix_hs_r <= matrix_hs; 92 matrix_en_r <= matrix_en; 93 end 94 end 95 96 assign post_vs = matrix_vs_r; 97 assign post_hs = matrix_hs_r; 98 assign post_en = matrix_en_r; 99 assign post_img_Y = post_en ? Mean_data:8'd0; 100 101 endmodule

1 `timescale 1ns/1ns 2 module Mean_Filter_top_tb; 3 4 5 6 7 //system 8 reg clk ; //像素时钟的同步,coms_clk , vga_clk 9 reg rst_n ; //复位信号 10 //coms or vga 11 reg pre_vs ; //前行同步 12 reg pre_hs ; //前场同步 13 reg pre_en ; //前数据有效 14 reg [7:0] pre_img_Y ; //数据灰度图像 15 16 wire post_vs ; //输出行同步 17 wire post_hs ; //输出场同步 18 wire post_en ; //输出数据有效 19 wire [7:0] post_img_Y ; //输出数据灰度图像 20 21 initial clk = 1; 22 always #5 clk = ~clk; 23 24 initial begin 25 rst_n = 0; 26 pre_vs =0 ; 27 pre_hs = 0; 28 pre_en = 0; 29 pre_img_Y = 0; 30 #51; 31 rst_n = 1; 32 pre_vs = 1; 33 #20; 34 pre_hs = 1; 35 #20; 36 pre_en = 1; 37 #60; 38 pre_en = 0; 39 #20; 40 pre_hs = 0; 41 #20; 42 pre_hs = 1; 43 #20; 44 pre_en = 1; 45 #60; 46 pre_en = 0; 47 #20; 48 pre_hs = 0; 49 #20; 50 pre_hs = 1; 51 #20; 52 pre_en = 1; 53 #60; 54 pre_en = 0; 55 #20; 56 pre_hs = 0; 57 #20; 58 pre_hs = 1; 59 #20; 60 pre_en = 1; 61 #60; 62 pre_en = 0; 63 #20; 64 pre_hs = 0; 65 #20; 66 pre_hs = 1; 67 #20; 68 pre_en = 1; 69 #60; 70 pre_en = 0; 71 #20; 72 pre_hs = 0; 73 $stop; 74 end 75 76 reg [7:0] shiftin; 77 always@(posedge clk or negedge rst_n ) begin 78 if(!rst_n) 79 shiftin <= 'd1; 80 else if(pre_en) 81 shiftin <= shiftin + 1'b1; 82 else 83 shiftin <= shiftin; 84 end 85 86 87 Mean_Filter_top Mean_Filter_top( 88 //system 89 .clk (clk ), //像素时钟的同步,coms_clk , vga_clk 90 .rst_n (rst_n ), //复位信号 91 //coms or vga 92 .pre_vs (pre_vs ), //前行同步 93 .pre_hs (pre_hs ), //前场同步 94 .pre_en (pre_en ), //前数据有效 95 .pre_img_Y (shiftin ), //数据灰度图像 96 //output 97 .post_vs (post_vs ), //输出行同步 98 .post_hs (post_hs ), //输出场同步 99 .post_en (post_en ), //输出数据有效 100 .post_img_Y (post_img_Y ) //输出数据灰度图像 101 102 ); 103 104 105 106 107 endmodule