FPGA-中值滤波

FPGA-中值滤波

排序实现sort从大到小

`timescale 1ns/1ns module sort( clk, rst_n, //input data1, data2, data3, //output max_data, mid_data, min_data ); //************************** inout ************************// input clk ; input rst_n ; //input input [7:0] data1 ; input [7:0] data2 ; input [7:0] data3 ; //output output [7:0] max_data ; output [7:0] mid_data ; output [7:0] min_data ; //************************* main code ************************// always@(posedge clk or negedge rst_n) begin if(!rst_n) begin max_data <= 'd0; mid_data <= 'd0; min_data <= 'd0; end else begin //求最大值 if(data1 >= data2 && data1 >= data3) max_data <= data1 else if(data2 >= data1 && data2 >= data3) max_data <= data2; else max_data <= data3; //求中间值 if((data1 >= data2 && data1 <= data3) || (data1 <= data2 && data1 >= data3) ) mid_data <= data1; else if((data2 >= data1 && data2 <= data3) || (data2 <= data1 && data2 >= data3) ) mid_data <= data2; else mid_data <= data3; //求最小值 if(data1 <= data2 && data1 <= data3) min_data <= data1 else if(data2 <= data1 && data2 <= data3) min_data <= data2; else min_data <= data3; end end endmodule

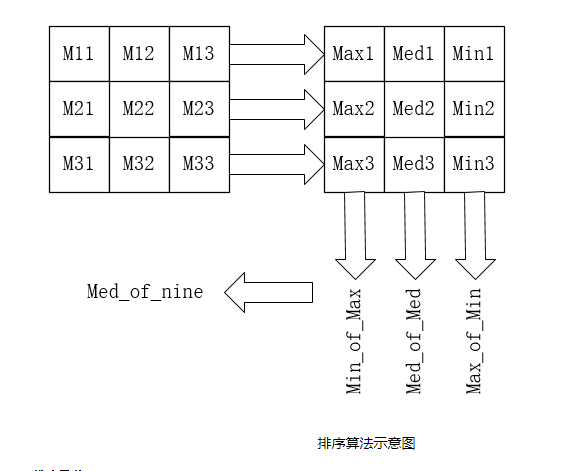

//中值滤波 //中值滤波 //功能:提取已经排列好的3x3数据,对列进行排列 // a11 a12 a13 已经排列成功行从大到小排列 // a21 a22 a23 // a31 a32 a33 //对排列好的3x3数据,对列排列 `timescale 1ns/1ns module Median_Filter_3X3( //system clk , //像素时钟的同步,coms_clk , vga_clk rst_n , //复位信号 //coms or vga matrixp11, matrixp12, matrixp13, matrixp21, matrixp22, matrixp23, matrixp31, matrixp32, matrixp33, median_data ); //**************************** input and output **********************************// //system input clk ; //像素时钟的同步,coms_clk , vga_clk input rst_n ; //复位信号 input [7:0] matrixp11 ; input [7:0] matrixp12 ; input [7:0] matrixp13 ; input [7:0] matrixp21 ; input [7:0] matrixp22 ; input [7:0] matrixp23 ; input [7:0] matrixp31 ; input [7:0] matrixp32 ; input [7:0] matrixp33 ; output [7:0] median_data ; //****************************** main code ***************************************// //第一行排序 wire [7:0] row1_max ; wire [7:0] row1_mid ; wire [7:0] row1_min ; sort sort_row1( .clk (clk ), .rst_n (rst_n ), //input .data1 (matrixp11 ), .data2 (matrixp12 ), .data3 (matrixp13 ), //output .max_data (row1_max ), .mid_data (row1_mid ), .min_data (row1_min ) ); //第二行排序 wire [7:0] row2_max ; wire [7:0] row2_mid ; wire [7:0] row2_min ; sort sort_row2( .clk (clk ), .rst_n (rst_n ), //input .data1 (matrixp21 ), .data2 (matrixp22 ), .data3 (matrixp23 ), //output .max_data (row2_max ), .mid_data (row2_mid ), .min_data (row2_min ) ); //第三行排序 wire [7:0] row3_max ; wire [7:0] row3_mid ; wire [7:0] row3_min ; sort sort_row3( .clk (clk ), .rst_n (rst_n ), //input .data1 (matrixp31 ), .data2 (matrixp32 ), .data3 (matrixp33 ), //output .max_data (row3_max ), .mid_data (row3_mid ), .min_data (row3_min ) ); //第一列排序 wire [7:0] col1_max ; wire [7:0] col1_mid ; wire [7:0] col1_min ; sort sort_col1( .clk (clk ), .rst_n (rst_n ), //input .data1 (row1_max ), .data2 (row2_max ), .data3 (row3_max ), //output .max_data (col1_max ), .mid_data (col1_mid ), .min_data (col1_min ) ); //第二列排序 wire [7:0] col2_max ; wire [7:0] col2_mid ; wire [7:0] col2_min ; sort sort_col2( .clk (clk ), .rst_n (rst_n ), //input .data1 (row1_mid ), .data2 (row2_mid ), .data3 (row3_mid ), //output .max_data (col2_max ), .mid_data (col2_mid ), .min_data (col2_min ) ); //第三列排序 wire [7:0] col3_max ; wire [7:0] col3_mid ; wire [7:0] col3_min ; sort sort_col31( .clk (clk ), .rst_n (rst_n ), //input .data1 (row1_min ), .data2 (row2_min ), .data3 (row3_min ), //output .max_data (col3_max ), .mid_data (col3_mid ), .min_data (col3_min ) ); //行排序 sort sort_row( .clk (clk ), .rst_n (rst_n ), //input .data1 (col1_min ), .data2 (col2_mid ), .data3 (col3_max ), //output .max_data ( ), .mid_data (median_data), .min_data ( ) ); endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号