SRAM(静态)存储器芯片的读/写周期

一、

要保证正确地读/写,必须注意CPU时序与存储器读/写周期的配合。一般存储器芯片手册都会给出芯片读/写周期的时序图。

Intel 2114芯片的读、写周期时序如图所示。

二、 读周期

读操作时,必须保证片选信号为低电平,读写信号为高电平。

tRC (读周期时间):指对芯片连续两次读操作之间的最小间隔时间。

tA (读出时间):从给出有效地址后,经过译码电路、驱动电路的延迟,到读出所选单元内容,并经I/O电路延迟,直到数据在外部数据总线上稳定出现所需的时间。显然,读出时间小于读周期时间。

tCO (片选到数据输出稳定的时间):数据能否送到外部数据总线上,不仅取决于地址,还取决于片选信号。因此,tCO是从有效到数据稳定出现在外部数据总线上的时间。

tCX(片选到数据输出有效时间):从片选有效到数据开始出现在数据总线上的间隔时间。

tOTD:片选无效后数据还需在数据总线上保持的时间。

tOHA:地址失效后,数据线上的有效数据维持时间,以保证所读数据可靠。

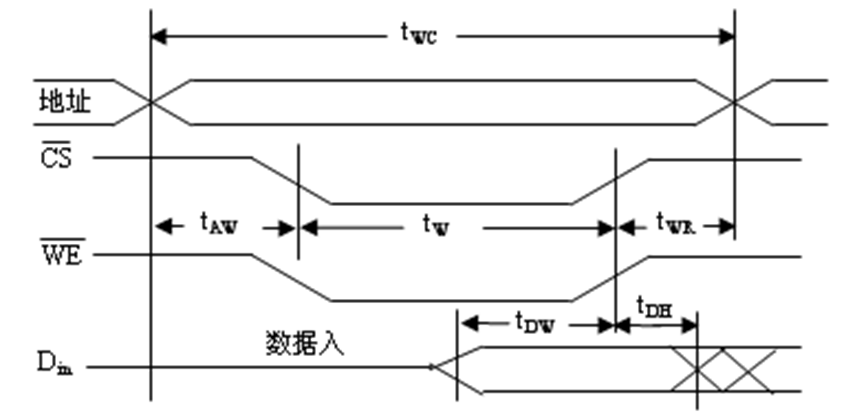

三、写周期

执行写操作时,为低电平,读写信号为低电平。

tW(写入时间):为保证数据可靠地写入,与同时有效的时间必须大于或等于tW。

tAW(滞后时间):地址有效后,必须经过tAW时间,WE/信号才能有效(低),否则可能产生写出错。

tWR(写恢复时间):WE/无效后,经tWR时间后地址才能改变,否则也可能错误地写入。

tDW:写入数据必须在写无效之前tDW时间就送到数据总线上。

tDH:WE/无效后,数据还要保持的时间。此刻地址线仍有效,tWR>tDH,以保证数据可靠写入。

tWC(写周期时间):表示连续两次写操作之间的最小时间间隔。tWC = tAW + tW + tWR。

朝闻道

浙公网安备 33010602011771号

浙公网安备 33010602011771号