以太网学习(三)——FPGA的MAC与PHY芯片之间的接口,以及RGMII接口时序

主要有SMII, MII, RMII, GMII, RGMII这几种接口,其中SMII是串行的接口,引脚最少。

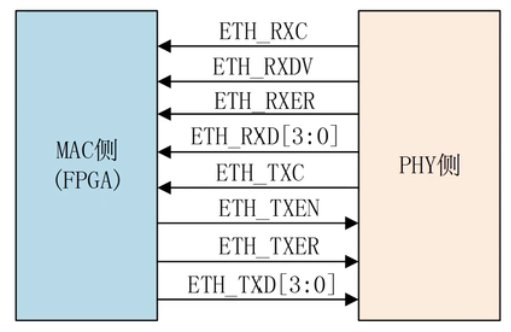

MII接口

通信速率10M/100M(百兆以太网的通信接口)

ETH_RXC:PHY侧输出给MAC的以太网的接受时钟

ETH_RXDV:PHY侧输出给MAC的接收有效信号

ETH_RXER:PHY侧输出给MAC的接收错误信号

ETH_RXD:PHY侧输出给MAC的4位接收数据

只有当ETH_RXDV为高电平,ETH_RXER为低电平时,这时传输的数据才是有效数据

ETH_TXC:发射时钟同样是有PHY芯片提供给MAC的

ETH_TXEN:MAC提供给PHY芯片的发送使能信号

ETH_TXER:MAC提供给PHY芯片的发送错误指示信号

ETH_TXD:MAC提供给PHY芯片的待发送的4位数据

只有当ETH_TXEN为高电平,ETH_TXER为低电平时,这时传输的数据才是有效数据

10M:时钟为2.5MHz,单沿采样;100M:时钟为25MHz,单沿采样

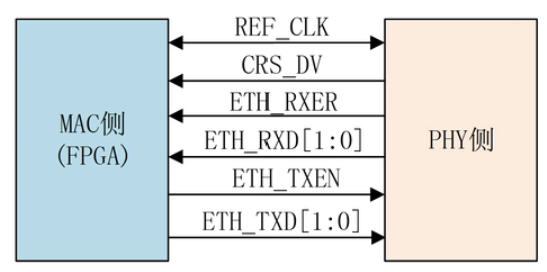

RMII接口(Reduced MII)

通信速率为10M/100M

发送数据核接收数据都是两位的;

参考时钟通常是由外部晶振提供给MAC侧或PHY芯片的;

CRS和DV信号复用一个端口;

10M:时钟为5M,单沿采样;100M:时钟为50M,单沿采样

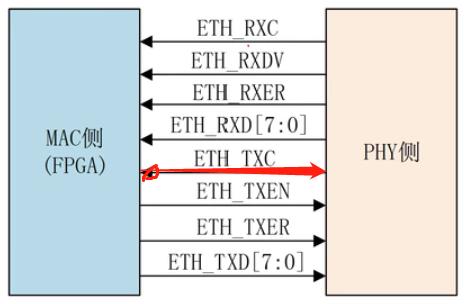

GMII接口(Gigabit MII)

通信速率1G/100M/10M

与MII接口相比,TXC由MAC侧产生(原图中画错了),并且将数据位宽从4位提高到了8位;

10M:时钟为2.5M,单沿采样,只用到了4位;100M:时钟为25M,单沿采样,只用到了4位;1G:时钟为125M,单沿采样

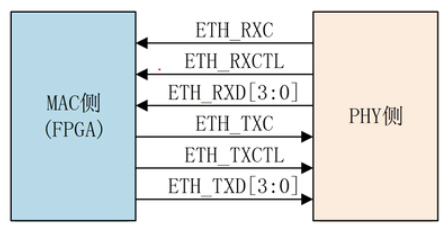

RGMII(Reduced GMII)

通信速率为1G/100M/10M

TXC由MAC侧产生;

将RXDV和RXER信号集成到了RXCTL上,时钟上升沿采到的是RXDV,下降沿采到的是RXDV^RXER(异或);

将TXEN和TXER信号集成到了TXCTL上,时钟上升沿采到的是TXEN,下降沿采到的是TXEN^TXER(异或);

数据位宽由8位减少到了4位;

1G:时钟为125M,双沿采样;100M:时钟为25M,单沿采样;10M:时钟为2.5M,单沿采样

RGMII接口时序

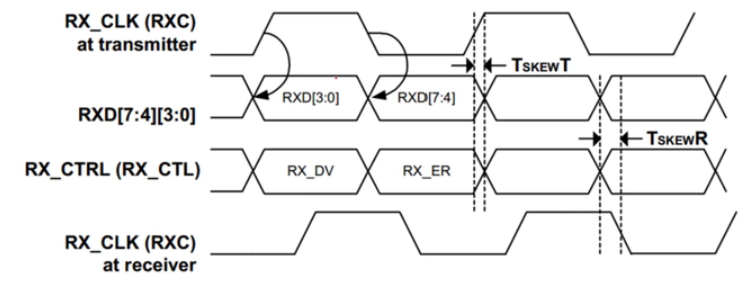

RGMII接收时序(1G)(PHY芯片产生的信号时序)

注:由于下降沿传输的是异或结果,所以正常情况下,RXCTL信号一直为高电平时传输的才是有效数据。

为保证能够正确采到数据,PHY芯片需要将接收到的TXC信号延迟约1/4个时钟周期。

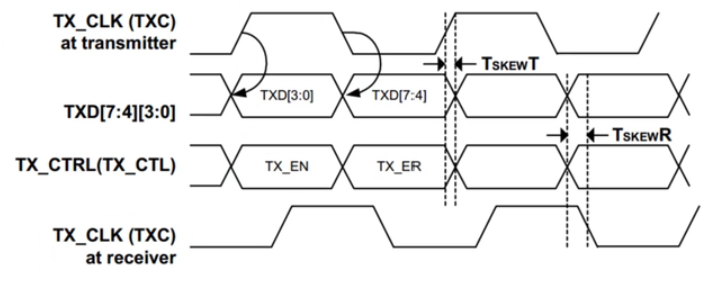

RGMII发送时序(1G)(FPGA MAC侧产生的信号时序)

注:由于下降沿传输的是异或结果,所以正常情况下,TXCTL信号一直为高电平时传输的才是有效数据。

为保证FPGA能够正确采到数据,PHY芯片需要将发送给MAC的RXC信号延迟约1/4个时钟周期。

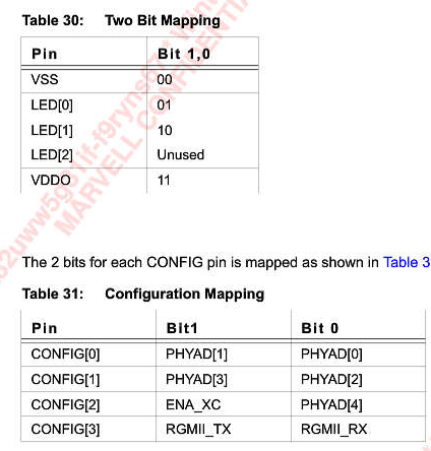

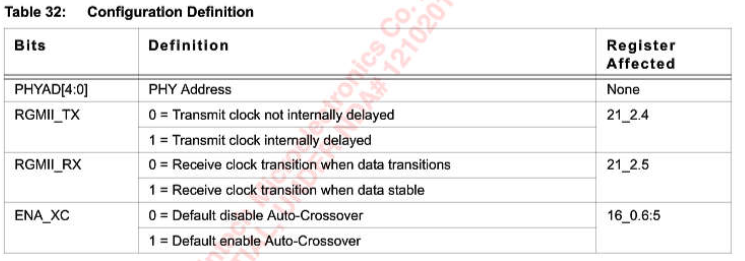

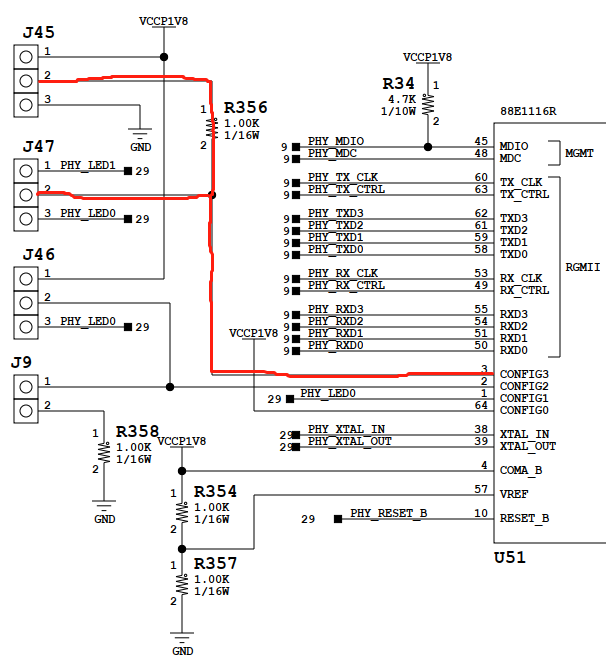

对于ZC706开发板上的88E1116R PHY芯片来说,控制时钟是否延迟的方式是CONFIG引脚或者通过寄存器的方式进行配置:

这个意思是,如果CONFIG[3]连到了LED[0]上,那么相当于配置了接收时钟的延时处理,但是没有配置发送时钟的延时处理。

或者可以通过MDIO配置相对应的寄存器21_2.4和21_2.5,用软件的方式配置时钟延时:

查看ZC706的PHY芯片88E1116R部分的原理图:

发现CONFIG[3]连到了排针的中间的引脚2,如果将J45中间的引脚通过短路片与1脚相连,那么就可以将PHY芯片配置成发送时钟和接收时钟都添加延迟。

参考:正点原子官方视频