Verilog基本语法(二)模块

模块

module <模块名> (<模块端口列表>, <端口声明>(若有), <参数声明>(可选)); ... // 模块内容 // 1 - wire, reg和其他类型的变量声明; // 2 - 数据流语句(assign); // 3 - 低层模块实例; // 4 - always和initial块,所有行为语句全都在这些块中; // 5 - 任务和函数 ... endmodule // 模块结束语句

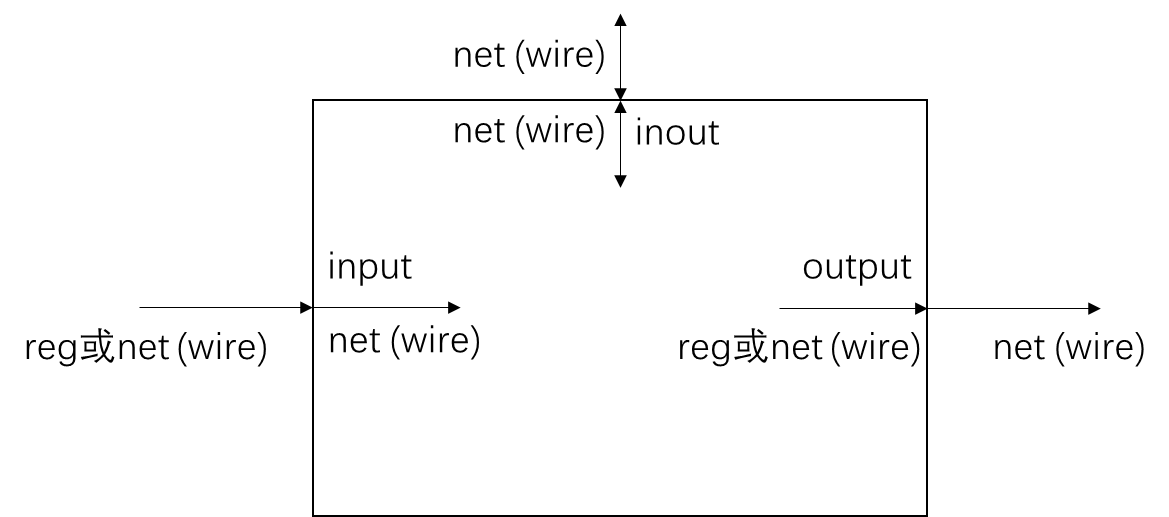

端口

端口声明

- input - 输入端口

- output - 输出端口

- inout - 输入/输出双向端口

注释:

- 所有端口隐含地声明wire类型。

- 输出(output)端口可以被声明为reg数据类型,用于保持输出值。

实例一

module fulladd4(sum, c_out, a, b, c_in); // 端口声明开始 output [3:0] sum; output c_cout; input [3:0] a, b; input c_in; // 端口声明结束 ... <模块的内容> ... endmodule

实例二(输出端口保持值)

module DFF(q, d, clk, reset); output q; reg q; // 输出端口q保持值 input d, clk, reset; ... <模块的内容> ... endmodule

实例三(ANSI C风格)

module fulladd4(output reg [3:0] sum, output reg c_out, input [3:0] a, b, // 默认类型为wire input c_in); // 默认类型为wire ... <模块的内容> ... endmodule

端口连接规则

浙公网安备 33010602011771号

浙公网安备 33010602011771号