Verilog 奇数分频

代码:

module odd_div( ); parameter DIV_PARA = 3; //分频系数,3即3分频 parameter DIV_PARA_2 = DIV_PARA >> 1; reg clk, rstn, clk_div_pos, clk_div_neg; wire clk_div_out; reg [31:0] cnt; initial begin clk <= 0; rstn <= 0; #50 rstn <= 1; end always begin #10 clk <= 0; #10 clk <= 1; end // 计数循环 always@(posedge clk or negedge rstn) begin if (!rstn) begin cnt <= 32'd0; end else if (cnt < (DIV_PARA-1)) cnt <= cnt + 1; else cnt <= 0; end // 上升沿触发 always@(posedge clk or negedge rstn) begin if (!rstn) begin clk_div_pos <= 0; end else begin if (cnt < DIV_PARA_2) clk_div_pos <= 1; else clk_div_pos <= 0; end end // 下降沿触发 always@(negedge clk or negedge rstn) begin if (!rstn) begin clk_div_neg <= 0; end else begin if (cnt < DIV_PARA_2) clk_div_neg <= 1; else clk_div_neg <= 0; end end // 生成分频信号 assign clk_div_out = clk_div_pos | clk_div_neg; endmodule

这个代码比较简单,而且为了仿真方便,将dut和bench写在一个模块了。。。。

代码设计思路来自这个帖子 https://blog.csdn.net/lt66ds/article/details/10035187

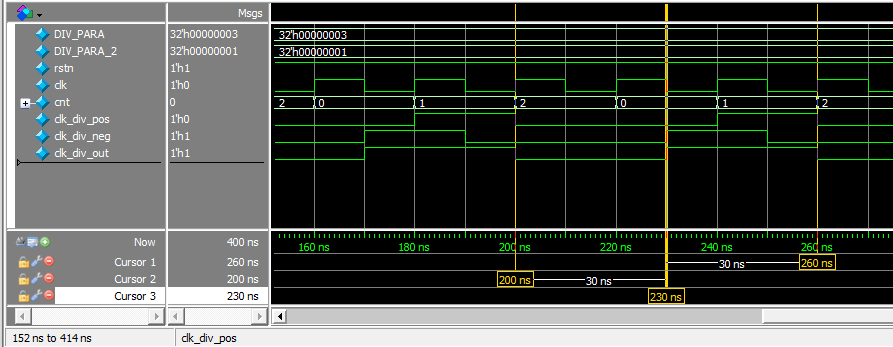

DIV_PARA参数设置分频系数,MoldelSIm仿真图如下

3分频:

DIV_PARA = 3

原时钟周期20ns,分频后的时钟周期为60ns,占空比为50%

5分频:

DIV_PARA = 5

原时钟周期20ns,分频后的时钟周期为100ns,占空比为50%

浙公网安备 33010602011771号

浙公网安备 33010602011771号